近幾年來,無線通訊傳輸系統在全球快速發展;而提供高速傳輸服務之無線通訊系統亦成為重要的研究之一。但無線網路在空氣中遭受到不可預期的傳輸影響,如通道衰減、都普勒效應(Doppler Effect)及傳輸基頻不一致,都可能降低訊號品質。因此,為處理上述問題,在接收端設計一個同步電路是必要的。

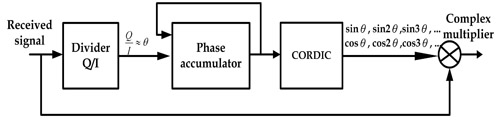

本文提出一種估測載波頻率偏移之方法及其創新旋轉座標弦波疊代振盪器(CORDIC-based Sinusoidal Iterative Oscillator, CSIO)電路,可應用於正交分頻多工(OFDM)無線區域網路之同步化訊號系統中載波回復問題。

本文所提之方法及其電路使用的弦波疊代振盪器,係以座標旋轉理論為基礎,可減少數位電路之振盪向量計算,亦提出新的偏移頻率角度計算及振盪量計算共用架構,可減少硬體實現的面積,提高可回復偏移頻率的精確度。對於多重輸入多重輸出(MIMO)系統,在可加性白色高斯雜訊(AWGN))影響下,整個電路可以回復625KHz的頻率偏移,更藉由共用偏移角度回復器而減少硬體實現之面積。

傳統的載波/時序回復振盪器包括類比及數位兩大類。類比電路架構所設計的振盪器,乃利用鎖相迴路(PLL)技術,但所產生之振盪電路無法完全置入正交分頻多工基頻系統中。數位方法則利用累計器計算旋轉角度的累進,再重複計算其對應之振盪波形。傳統的頻率回復數位振盪器大致採用之方法有兩種,一為利用Sin/Cos列表數值,來尋找每一個時脈(Clock),通訊接收端之角度累積器所需要回復的角度值;另一種方式乃利用數位座標旋轉器(Coordinate Rotation Digital Computer, CORDIC)來取代sin/cos列表數值。

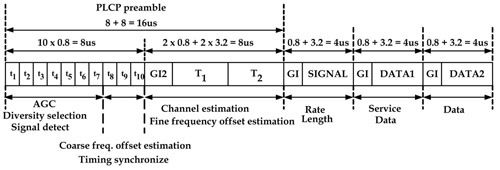

在無線區域網路(WLAN)IEEE 802.11a系統中,每個訊框都有一個前置訊號(Preamble),其定義如圖1所示,其中t1~t10為週期為十六個時脈的十次重複短前置符元,T1及T2為週期為六十四個時脈的二次重複長前置符元;後面則為訊號區及資料區。一個短前置訊號經由傅立葉快速轉換(FFT)將頻域訊號轉成週期性的時域訊號,週期性訊號之相關性,致此接收器可偵測封包及估測載波頻率偏移。IEEE 802.11a協定中所制定的短前置訊號,可作自動增益控制(AGC)、多樣性選擇(Diversity Selection)、時間同步化及粗略的頻率偏移估測及其同步;至於長符元則可於接收器作通道估測及副通道修正。

|

| 圖1 訊框前置訊號在IEEE 802.11a WLAN系統的定義 |

應用環境通道複雜 多元演算法有助釐清

本文所提之研究係以IEEE 802.11a為基礎,並將詳細說明其接收器中,正交分頻多工無線區域網路同步電路之設計方法及硬體實施。

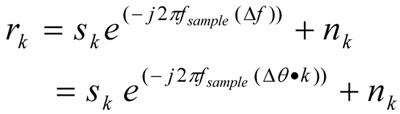

首先利用IEEE 802.11a標準,實體層聚合程序(Physical Layer Convergence Procedure, PLCP)前置訊號來設計之同步化電路,其中前七項短前置訊號(Short Preamble)符號用於AGC及訊框偵測(Frame Detection);最後三個短前置訊號符號用於時間估測(Timing Estimation)及粗略的載波頻率偏移(Carrier Frequency Offset, CFO)估測。通道估測(Channel Estimation)及精確的CFO估測則靠兩個長前置訊號(Long Preamble)符號。假設AGC及時脈同步化係於訊框偵測之前完成,且接收訊號受可加性白色高斯雜訊、時間延遲及頻率偏移影響,公式如下:

其中sk及rk分別為在第k個採樣時間所發射及接收之序列。當發射器及接收器的頻率不同 時,則產生載波頻率偏移。此誤差可由前端PLL或都普勒效應推知。

時,則產生載波頻率偏移。此誤差可由前端PLL或都普勒效應推知。

偵測訊框/符元邊界 時間估測同步化

在應用環境通道演算法分析中,時間估測係根據間歇模式(Burst Mode)中正交分頻多工的短前置以知序列與接收訊號之互相關性(Cross Correlation),找出第一個符元的起點,當第一個符元的起點為已知,間歇模式中後續符元的起點亦可得知。時間同步化包括訊框偵測及符元邊界偵測。藉此可找出符元邊界及短前置訊號的終點,則可計數粗略CFO估測、精確CFO估測及FFT開始的時間(圖1)。

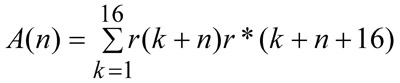

在訊框偵測部分,接收器接收的訊號與本身的短符元的延遲相關,公式如下:

其中r(n)為接收序列,A(n)為自相關(Autocorrelation)輸出,接收器的訊框可藉由比對門檻值(Threshold)的大小而得知。若採用輸入訊號功率強度的動態門檻值,由短前置訊號的前兩個週期訊號(t1、t2)於自動增益控制時操作,則其門檻值如下式:

其中r(n)為接收的短前置訊號訊號。當A(n)> THR時,時序控制器產生突波,用以告知接收端系統準備接收封包及控制接收器的時序。

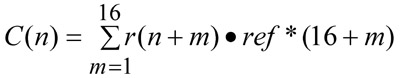

至於符元邊界偵測,當訊框的起點已知時,接收器可使用滑動相關器(Sliding Correlator)找出接收訊號與前置訊號中已知正交分頻多工符元的波形的相關性,以偵測符元邊界並偵知短前置訊號結束的時間。交互相關器作用有如匹配濾波器(Matched Filter)。16-tap相關器係由第一個得知的訊框產生,十個波峰如下所示:

其中C(n)為交互相關的第n次匹配濾波器輸出,ref(m)為第m個已知序列的複數值。

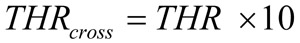

然而,具有複數的浮點係數相關器需要昂貴的複數乘法器,若將相關器係數的實部及虛部以2的冪次和表示,則只須移位及加法運算,以此避免乘法器使用之面積及其功率消耗。假設refm的實部及虛部滿足式如下:

其中=2-n,n為0或正整數。將係數乘以10後,再以

其中=2-n,n為0或正整數。將係數乘以10後,再以 =1化成[0 -1 -j 1 1 1 -j -1 0 -j -1 j j j -1 -j]。根據接收器門檻值之公式,交互相關的門檻值可表示成

=1化成[0 -1 -j 1 1 1 -j -1 0 -j -1 j j j -1 -j]。根據接收器門檻值之公式,交互相關的門檻值可表示成 。

。

藉由相關性的波峰,可知短前置訊號並未通過。這些波峰甚至可表示符元邊界的起點,並啟動有限狀態機(FSM)以於每十六個樣本後找出短前置訊號的終點。

CFO影響訊號精確度 回復載波扭轉乾坤

CFO的後果為:減弱匹配載波的濾波器輸出訊號,及由其他載波引入載波間干擾(ICI)。因此,累積載波頻率同步在正交分頻多工系統非常重要。根據IEEE 802.11a規範,發射中心頻率容許度最大為±20ppm;亦即當最大粗略補償容忍範圍為約625 kHz,而最大精確補償容忍範圍為約156.25kHz時,發射器與接收器之間的最大CFO為40ppm或大約200kHz。以下所述之方法則係以準確的時間估測及時脈同步化為基礎。

在粗略的CFO估測中,假設訊號係於緩慢衰減通道中傳送,則短前置符元之兩重複週期之間相關性受相位旋轉影響。根據IEEE 802.11a,相關器執行CFO最大相似可能性度估測(Maximum Likelihood Estimation, MLE),最後三個短符元係用於粗略的CFO估測。事實上,AGC之後的任何三個在時域上的連續短週期訊號皆可適用下列演算法。

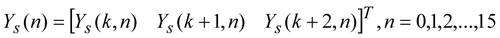

以Xs(m,n)表示第m個無雜訊短前置符元的第n個樣本,Ys(m,n)表示經由該通道接收到的雜訊輸出;則Ys(m,n)=Xs(m,n)+es(m,n),其中es(m,n)為AWGN雜訊。

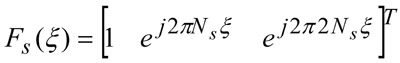

令

其中(.)T表示轉置,Ns=16,ξ表示CFO;則可得下式:

所有連續的短前置訊號可用於如下式之非線性最小平方(Nonlinear Least Squares, NLS)函數:

其中||.||表示歐基里得模(Euclidean Norm)。以Xs(k,n) 及ξ最小化式則得下二式:

令

以ξ微分上式,並令其為0時,可得式:

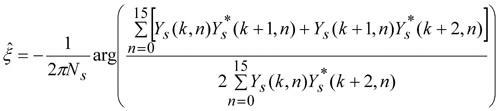

使短前置訊號之式最小化之CFO的粗估結果如下:

若為降低硬體成本,並可修改為下式:

其中arg(.)表示幅角(Argument)。由上式可找出延遲,且降低自相關的相關性。

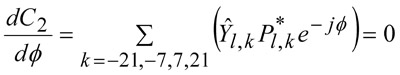

至於精確的CFO估測,在IEEE 802.11a標準中,兩個長前置訊號係用於精確的CFO估測。類似粗略的CFO估測,可得下列兩方程式:

未經FFT的複數訊號可藉由粗略及精確的CFO估測,得下式:

其中rk表示以接收的長前置訊號開始的複數取樣值。

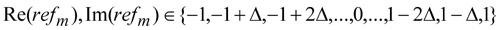

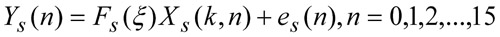

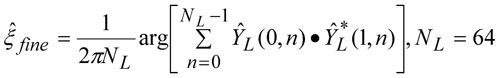

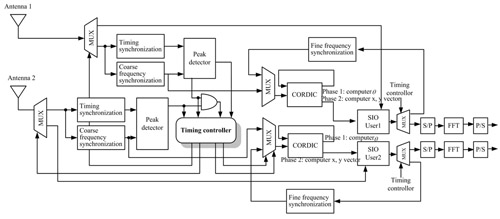

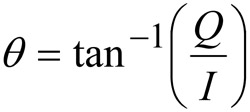

值得一提的是,雖然CFO估測儘可能補償CFO,但估測誤差仍存在於不同的訊噪比(SNR)值。較高的QAM調變可有較高的資料傳輸速率,但卻無法忍受載波頻率偏移。當連續接收OFDM符元時,相偏移會愈來愈明顯,最後導致傳送失敗(圖2)。在FFT後,仍有CFO引起的少許相偏轉,則可藉由額外的相位校正來去除。

|

| 圖2 2×2無線傳輸系統接收端同步電路方塊圖 |

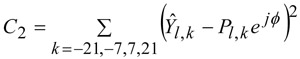

根據802.11a標準,四個導引副載波的值為{1.0, 1.0, 1.0, -1.0},於每一個OFDM符元中與四十八個資料副載波混合。藉由四個導引副載波的特性,於頻域之一個訊號週期中,與FFT後的訊號產生相關。此法類似粗略的CFO估測並詳述如下:

其中 為第1個符元的第k個訊號,

為第1個符元的第k個訊號, 為第k個頻率副載波的值。擴充上述方程式並以φ微分之,可得下二式:

為第k個頻率副載波的值。擴充上述方程式並以φ微分之,可得下二式:

CSIO強化同步電路硬體設計

旋轉座標弦波疊代振盪電路方法亦可實作至單一裝置,包括時間估測及CFO估測,並藉由軟體模擬及硬體驗證了解其效果。

自相關器/交互相關器位居時間估測要角

在時間估測方面,時間估測包括時間偏移間隔為十六個時脈的自相關器及十六個已知係數的分接頭(16-tap)之交互相關器,其架構如同匹配濾波器。為偵測波峰,須比對自相關器的絕對值及具有門檻值的交互相關器。

自相關器在同步電路中相當重要,因其不僅用於時間估測,亦可再用於粗略的CFO估測;類似的架構亦用於深度為64的精確CFO估測。深度16的自相關器包括延遲暫存器、複數乘法器及移動加法器。

複數乘法器的原理如下:

由前二式加及減乘積AD及AC,可得下式:

由此二式可知,有三個有號數(Sign)乘法器及五個加法器。相較於R=AC–BD與I=AD+BC二式,一個乘法被三個加法取代了。

有號數乘法器進一步利用radix-4改良布斯(Booth)編碼,可加速運算及節省乘法器面積。radix-4編碼器之輸出為-2×、-1×、0×、1×及2×(其中2×表2倍被乘數),可藉由位移運算域簡單得到。

在此不採用分時多工(TDM)壓縮Wallace Tree的部分積,而使用完全加法器達到低冪次及高速的目標。

此外,亦須考量複數乘法器之截斷位元。16×16之有號數乘法器須具有32位元輸出,才能有非失真解析度。若不截斷位元,下一個有號數乘法器將有32位元輸入及64位元輸出。因此32位元於所有有號數乘法器用於系統後截斷。為減少截斷引起的失真,只在輸出作截斷,內部運算則保持高精確度。

在交互相關器及波峰偵測器部分,則試圖以加法取代乘法可減少面積,係數則量化為前述之{0, -1, 1, j, -j}。

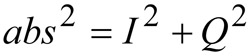

訊號進入波峰偵測器之前,自相關器及匹配濾波器的輸出絕對值先平方後相加,如下所示:

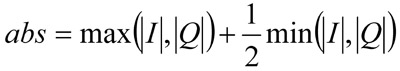

上式取絕對值之操作,須以下式取代,以提高數位電路設計的有效性,且此式的效率較高,所需硬體面積亦較小。

匹配濾波器藉由比對已知的門檻值即可偵測得到波峰位置。當第一個波峰找到後,藉由有限狀態機可找出短前置訊號的起點及終點時間的位置,或決定粗略及精確CFO估測的開始時間。本例使用一個4位元計數器,其長度為一個短符元的樣本數。

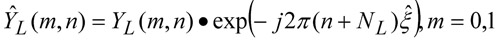

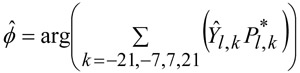

CFO估測改善傳統振盪器效能

CFO估測包括粗略的CFO估測及精確的CFO估測:粗略的CFO估測使用短前置訊號持續期間自相關輸出值的實部及虛部;精確的CFO估測類似粗略的CFO估測,但於長前置訊號持續期間進行。利用估測之頻率偏移值驅動創新旋轉座標弦波疊代振盪電路,此重要之創新架構可改善傳統數位振盪器的功率消耗、運算執行時間及硬體成本,以下將詳述這CFO估測及CSIO的架構。

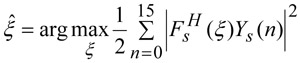

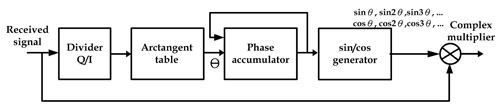

圖3為傳統CFO估測的架構,在取得自相關輸出值的實部及虛部後,令實部為I,虛部為Q,二者相除之商即正切值,則CFO的旋轉角可以下式表示:

|

| 圖3 傳統CFO估測的ROM架構 |

此角度可在反正切值的表格中找到。若弧度小於0.5,則商可滿足下式:

,ifθ<0.5

,ifθ<0.5

表1列出字元長度為22位元的近似值;其中旋轉角度愈小,則近似值愈相近。本實施例使用此法係因802.11a標準中,載波頻率偏移的公差甚小。

表1 DVB-T參數

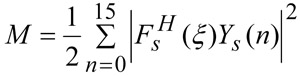

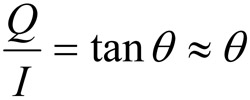

藉由除法器找出旋轉角之後,傳統方法中尚需累計器及sin/cos產生器,由於建立sin/cos對照表的建立需要較長字元的記憶體空間,以滿足系統所需的表達之值及減少擷取值誤差,故此表的大小與所需精確度成正比。另一傳統架構(圖4)係以數位座標旋轉器的架構取代ROM。然而,CORDIC須經許多時脈循環,才能產生sin/cos的值;雖然可減少硬體面積,但效率較差。

|

| 圖4 傳統CFO估測的CORDIC架構 |

為改善上述缺陷,可採用如圖5所示的CFO估測架構,其包含CORDIC及正弦疊代振盪器(Sinusoid Iteration Oscillator, SIO)。

|

| 圖5 CFO估測的CORDIC及SIO架構 |

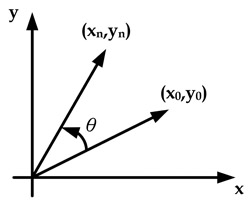

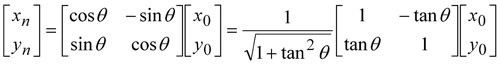

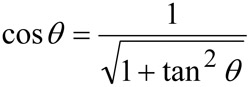

CORDIC主要用於乘法、除法及雙曲函數。向量[x0, y0]T在極座標旋轉角度為θ時,以[xn, yn]T表示。如圖6所示,此結果向量可藉由矩陣運算法運算。

|

| 圖6 極座標中角度旋轉之示意圖 |

其中 。

。

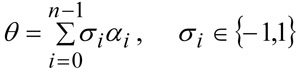

由參數σi規範,分角αi的和趨近θ,

在矩陣運算法中αi的正切可以下式中2的冪次表示:

tanαi=2-i, i=0, 1, …, n-1

累加的分角zi可用來控制分角的符號,z0=θ

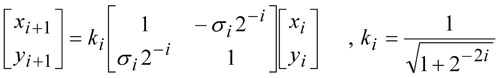

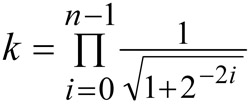

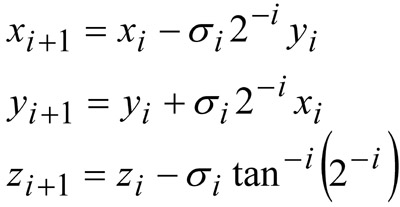

其中σi為第i疊代的旋轉方向,且每一步驟的矩陣積可簡化為下式:

下式的部分因子ki為所有n次疊代之總和因子。

根據先前的假設,無部分因子ki的疊代方程式如下所示:

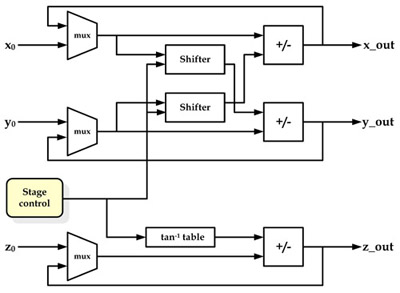

上述方程式可藉由位移及反正切表查知:x0及y0分別為1及0,z0為θ。藉由選擇適當的k值,可得sinθ及cosθ的精確值。CORDIC的架構如圖7。

|

| 圖7 顯示CORDIC的架構 |

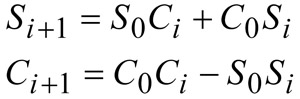

以正弦疊代振盪器取代傳統的相位累計器,則下列三角函數用以計算sin(kθ)及cos(kθ)之值,其中k=1, 2, 3 ... N,N為接收器的訊號數:

假設A=θ,B=θ, 2θ, 3θ, …… (k-1)θ。第一個旋轉向量sinθ及cosθ可由CORDIC計算出,並作為下式正弦疊代振盪器的初始值:

sinθ及cosθ可視為常數,則可得修正方程式如下:

其中S0=sinθ,C0=cosθ

圖8為SIO的架構,其藉由截斷保持下一階段輸入字元的長度。除了自相關的長度改為長前置符元的六十四個時脈取樣之外,精確CFO估測的架構與粗略CFO估測相似。須注意的是,由於精確的CFO估測所欲找出的角度甚小,因此sinθ視為θ,而cosθ視為1。換言之,精確的CFO估測的架構不須靠CORDIC計算第一個旋轉向量,sinθ及cosθ修正方程式的初始值變成S0=θ,C0=1。

|

| 圖8 SIO架構 |

粗略及精確的CFO估測的架構可合併。為減少硬體面積,因粗略及精確的CFO估測於不同時間進行,因此可共用除法器。接收訊號在粗略的CFO估測作第一次旋轉後,再於精確的CFO估測作第二次旋轉。

表2為比較使用圖3~5中不同架構所需的時間及面積;假設CORDIC需要M個時脈循環及N個接收資料訊號,則相位累計器、sin/cos產生器及正弦疊代振盪器分別需要一個時脈循環。

表2 不同振盪器架構所需的時間及面積比較表 |

| 電路形式 |

執行時間(時脈) |

硬體面積 |

| ROM |

1+1*N |

大 |

| CORDIC |

1+M*N |

小 |

| CSIO |

M+1*N |

中 |

以0.18微米1P6M互補式金屬氧化層半導體(CMOS)的1.8伏特製程製造無線系統的同步架構;比較所提出的CSIO結構與其他電路的特性,結果如表3所示。就WLAN系統來說,系統封包時脈頻率的容許偏差為40ppm,最大長度為4,095;則頻率容許範圍在200k~407kHz之間。同時比較在20MHz操作頻率下,單天線與2×2MIMO WLAN系統的差異。字元長度為16位元複數輸入及輸出訊號,其可描述精細載波同步化的值,而避免量測誤差。

| 表3 CSIO結構與其他電路的特性比較 |

| |

CSIO |

CORDIC |

NCDL |

| 字元寬度(bits) |

16 |

9 |

12 |

| ROM(bits) |

16×18 |

10×12 |

256×12×4 |

| 頻率解析度(Hz) |

76.3 |

1.55 |

610 |

| 最大頻率旋轉(KHz) |

625 |

6.35 |

625 |

| CFO Tolerance |

符合 |

符合底限 |

符合上限 |

創新架構有優勢 應用範圍再延伸

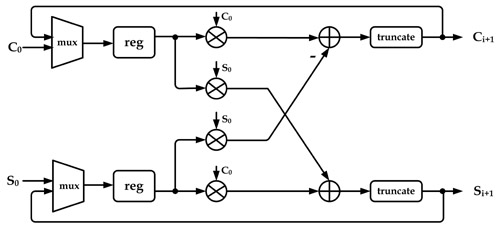

為確認此次相關電路設計之優劣,因此在以MATLAB進行浮點及定點高階模擬後,以Verilog硬體描述語言(HDL)編輯暫存器轉移邏輯碼(RTL Code)。接著用Verilog-XL編譯RTL碼以確保所有程式皆可執行,接著再以設計影像(DV)合成RTL碼,以得到閘層級碼(Gate Level Code),並以EDA工具檢查波形。最後將編碼載入現場可編程閘陣列(FPGA)以檢測結果,並與閘層級模擬結果比較。以SIO的θ=π/18及π/4作MATLAB模擬,結果如圖9(a)及(b)所示,角度小於π/4時,SIO的值較精確。

|

| 圖9 SIO的MATLAB模擬結果 |

在RTL碼模擬之後,利用DV作閘層級模擬及以Verilog-XL驗證所提出電路架構的效果是否如預期。輸入訊號旋轉約0.03弧度(600kHz),目的為藉由CFO估測找出旋轉角。

圖10(a)顯示自相關及交互相關的絕對值的波形,可由其中發現時間點。圖10(b)及(c)為粗略及精確CFO估測中,正弦疊代振盪器的輸出;其中圖10(b)顯示粗略頻率同步化結果在645.752kHz,比實際頻率約45.752kHz要大,經精確頻率同步化再回復至59.937kHz,如圖10(c)所示。圖10(d)顯示在無正負號的十六進位中所找到的角度,粗略CFO估測為0.031738弧度,精確CFO估測則為-0.001587弧度。總角度為0.030151弧度,非常接近0.03弧度,精確度達0.0001。模擬結果得到的時間、面積及冪次列於表4。證明本方法及電路設計於5GHz旋轉600kHz,及於2.4GHz旋轉300kHz非常成功。至於在FPGA檢測部分,單天線系統的功率及硬體面積同樣於表4,所需硬體面積約為1.682平方毫米。

|

| 圖10 (a)圖顯示自相關及交互相關的絕對值的波形;(b)及(c)圖為粗略及精確CFO估測中正弦疊代震盪器的輸出(d)圖顯示粗略及精確CFO估測中所找到的角度 |

表4 單天線系統與2×2 MIMO系統的功率及硬體面積 |

| |

單天線系統 |

2×2 MIMO系統 |

| 面積 |

0.867平方毫米 |

1.682平方毫米 |

6201/7680 slices

(VirtexII XC2V1500) |

| 功率 |

76毫瓦 |

90.53毫瓦 |

536毫瓦

(VirtexII XC2V1500) |

根據上述,主要使用在多重輸入多重輸出正交分頻多工無線區域網路之同步,其特點包括:以座標旋轉理論為基礎,藉由弦波疊代振盪器有效減少數位電路之振盪向量計算;利用CORDIC技術,藉由偏移頻率角度計算與振盪量計算共用之架構,有效減少硬體實現之面積;提高可回復偏移頻率的精確度達0.1%;於多重輸入多重輸出系統中,因共用偏移角度回復器,可減少硬體實現之面積,只需0.839 平方毫米的面積;包括無線區域網路及4G技術領域如手機、WLAN等正交分頻多工傳輸系統均可應用本技術。

雖然本文之較佳實施例以IEEE 802.11a標準為規範,但可據以延伸至如全球微波存取互通介面(WiMAX)等其他有線/無線通訊同步系統。

(本文作者任職於工研院系統晶片科技中心)

| 參考資料 |

‧IEEE Standard for Local and metropolitan area networks, Part 16: Air Interface for Fixed Broadband Wireless Access Systems, 2004.

‧IEEE Std 802.11g as amended by IEEE Stds Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specification. IEEE std. 802.11a-1999.

‧The TGn Sync Proposal Technical Specification in http://www.tgnsync.org/home.

‧S. Menon, G. Cho, and M. Soderstrand, "An improved numerically controlled digital oscillator," IEEE Pacific Rim Conference on Communications, Computers and Signal Processing, vol.2, pp. 1040-1044, 2003.

‧H. Zou and B. Daneshrad, "VLSI implementation for a low power mobile OFDM receiver ASIC," IEEE Wireless Communications and Networking Conference, vol. 4, pp. 2120-2124, 2004. ‧A.M. Sayeed and V. Veeravalli, "The essential degrees of freedom in space-time fading channels," IEEE International Symposium on Personal, Indoor and Mobile Radio Communications, Vol. 4, pp. 1512-1516, Sept. 2002.

‧M.-C. Chen, Design of 802.11a Baseband Transmitter and Synchronization, Mater Thesis, National Chiao Tung University, 2002.

‧C.-S. Peng, K.-A. Wen, "Synchronization for carrier frequency offset in wireless LAN 802.11a system," The 5th International Symposium on Wireless Personal Multimedia Communications, vol.3, pp.1083-1087, Oct. 2002.

|

‧J. Li, G. Liu, G.B. Giannakis, "Carrier frequency offset estimation for OFDM-Based WLANs," IEEE Signal Processing Letters, vo.8, no.3, pp.80-82, March 2001.

‧Y.P.G. Jimenez, M.J.F Garcia, F.J.G. Serrano, A.G. Armanda, "Design and implementation of synchronization and AGC for OFDM-based WLAN receivers," IEEE Transactions on Consumer Electronics, vol. 50, no. 4, pp.1016-1025, Nov. 2004.

‧H. Zou, B. Daneshrad, "VLSI Implementation for a low power mobile OFDM Receiver ASIC" Wireless Communication and Networking Conference on WCNC, vol.4, no.4, pp.2120-2124, Los Angeles, 2004.

‧S. Chang and B. Kelley, "Time synchronization for OFDM-based WLAN system," Electronics Letters, vol. 39, no. 13, pp. 1024 - 1026, Jun., 2003.

‧K.-W. Yip, Y.-C. Wu, and T.-S. Ng, "A new multiplierless correlator for timing synchronization in IEEE 802.11a WLANs," Proceeding of International Symposium on Circuits and Systems, vol. 2, pp. II-344 - II-347, May 2003

‧W.C. Yeh and C.-W. Jen, "High-speed booth encoded parallel multiplier design," IEEE Transactions on Computers, vol.49, no.7, pp.692-701, July 2000.

‧H.-L. Lin, C.-C. Hsu, R. C. Chang, “Implementation of synchronization for 2x2 MIMO WLAN system,” IEEE Transactions on Consumer Electronics, vol. 52, no. 3, pp. 766 – 773, Aug. 2006. |