在先前已刊出的上集文中,總結了JESD204B子類和確定性延遲,並提供子類0系統中多晶片同步的應用層解決方案詳情。本文下集將詳細討論子類1和子類2的不同之處。

具體而言,將討論滿足確定性延遲相關的時序要求時遇到的挑戰、子類2中元件時脈速度限值,以及對於給定的系統應用,採用何種子類效果最佳的相關指導。

子類1

在子類1系統中,確定性延遲的精度取決於元件時脈和SYSREF之間的時序關係,以及系統中這些訊號的分布偏斜。除了SYSREF的設定時間和保持時間要求(TSU和THOLD),應用對於確定性延遲不確定的容忍程度對於定義SYSREF與元件時脈的應用分布偏斜要求而言至關重要。

精準捕捉SYSREF

採用JESD204B介面的轉換器具有極高的採樣速率。為了降低系統中的相位雜訊,這些轉換器通常會使用一個參考時脈,該參考時脈與JESD204元件時脈相同,其速率等於或大於採樣速率。很多情況下,該時脈頻率為GHz級。在如此高的速度下,要滿足設定和保持時間要求就會變得非常具有挑戰性。為了簡化系統設計,對於JESD204B系統組成部分的各元件而言,也許有必要採用可編程的SYSREF和/或元件時脈相位失調。

子類1相對於子類2所具有的一個優勢,是前者採用源同步時脈。子類2系統使用系統同步時脈,相較於使用源同步時脈會更早遇到頻率限值問題。後文會詳細研究子類1和子類2時序示例時,將加以說明。

確定性延遲不確定性

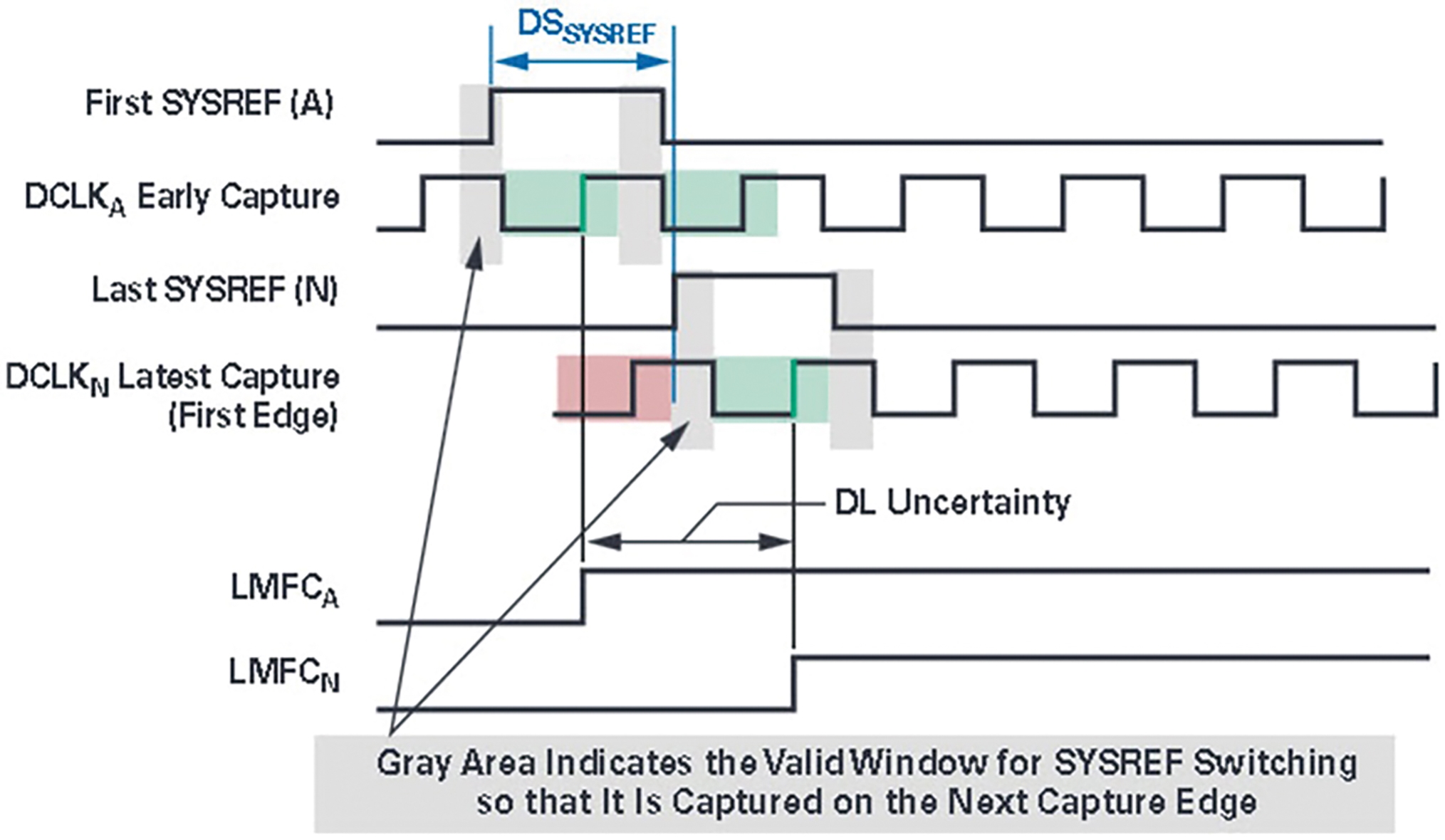

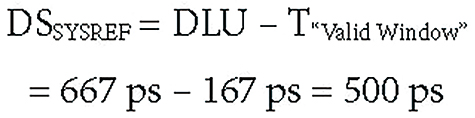

確定性延遲不確定性(DLU)在JESD204B系統中表現為LMFC偏斜,由系統中最早與最遲可能捕捉的SYSREF時間之差確定。圖1顯示的是最差情況下的DLU,此時系統中一切元件均不滿足SYSREF捕捉的設定和保持時間要求。當系統中元件時脈的分布偏斜不受控時便會發生;它會使最多一個元件的時脈(DCLK)產生不確定性。這種不確定性會疊加到SYSREF分布偏斜中(DSSYSREF),形成總DLU,如公式1所示:

................公式(1)

圖1 確定性延遲不確定性的最差情況

圖1 確定性延遲不確定性的最差情況

DSSYSREF是系統中SYSREF的最早到達時間以及SYSREF的最遲到達時間之差(針對全部元件)。在圖中,TSU是TDCLK的一半且THOLD是TDCLK的四分之一。最早到達的SYSREF (A)在可能的最早時間加以捕捉(DCLKA剛好滿足設定時間要求),而最遲到達的SYSREF (N)在可能的最晚時間加以捕捉(DCLKN剛好不滿足設定時間要求)。因此,相應的LMFC對齊誤差等於DSSYSREF + TDCLK。為保持DLU概念圖示的清晰明瞭,此處未考慮時脈抖動和製程、電壓以及溫度(PVT)的變化。

在很多應用中,都以能夠接受這種最差情況下的DLU作為要求。這些應用可能無須過於嚴格地控制元件的時脈分布偏斜。確保SYSREF的脈衝寬度(2× TDCLK),然後控制SYSREF分布偏斜,就應當足以滿足系統時序要求。

對於無法接受額外元件時脈不確定性的應用,就必須嚴格控制元件的時脈分布偏斜,保證系統中每一個元件的SYSREF時序要求得到滿足,這種情況如圖2所示。

圖2 滿足SYSREF設定與保持時間的DLU

圖2 滿足SYSREF設定與保持時間的DLU

.最小化確定性延遲不確定性

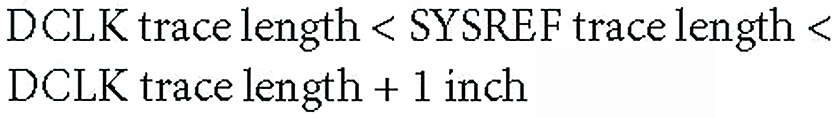

如以上DLU等式所示,透過保證每一對SYSREF/DCLK均滿足設定與保持時間,以及最小化對內分布偏斜,便可最小化DLU。 若要滿足設定與保持時間要求,JESD204B系統中的每一個元件都應有自己的SYSREF/DCLK對。可透過在各對內實現布線長度匹配,以保證時序。布線長度匹配限值由SYSREF切換的有效視窗時間確定。此外,SYSREF應在DCLK的捕捉邊緣上輸出,且SYSREF長度必須大於DCLK的長度,以滿足保持時間要求(如果THOLD等於0,則長度可以相等)。

由於採用了布線長度匹配,最小化對內分布偏斜基本上等同於最小化SYSREF分布偏斜。該分布偏斜限值等於DLU限值減去有效視窗時間,同樣可以透過布線長度匹配來處理。DLU限值由應用要求所決定。

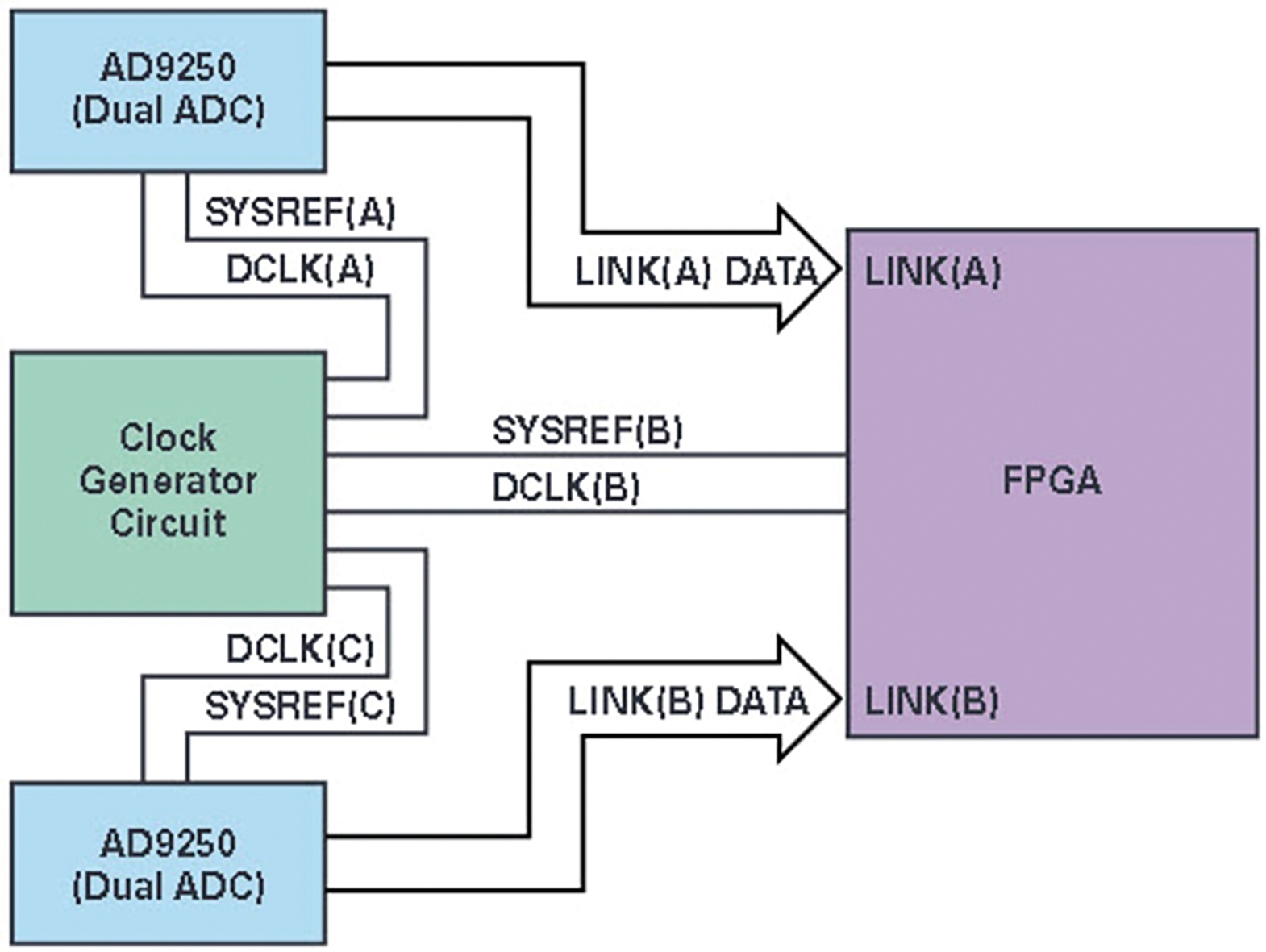

這些最小化DLU的方法如圖3所示。由於JESD204b系統中的每一個元件都有各自的SYSREF/DCLK對,滿足捕捉SYSREF的時序要求與使用源同步時脈的任何系統類似。每個元件的時序裕量都視為與系統中的其他元件無關。

圖3 由3個元件組成的JESD204B系統的SYSREF/DCLK路由

圖3 由3個元件組成的JESD204B系統的SYSREF/DCLK路由

.使用AD9250的SYSREF時序示例

AD9250是一款14位元、250MSPS雙通道類比數位轉換器(ADC),具有JESD204B串列資料輸出能力,額定速率為5Gbps。為了最大程度提升鎖相迴路(PLL)性能,AD9250可支援高達1.5GHz的元件時脈速度。這便為如何在最嚴苛的系統DLU要求下使用布線長度匹配來滿足SYSREF時序提供了一個極佳的展示實例,以下為本例條件:

DCLK = 1.5GHz(667ps週期)

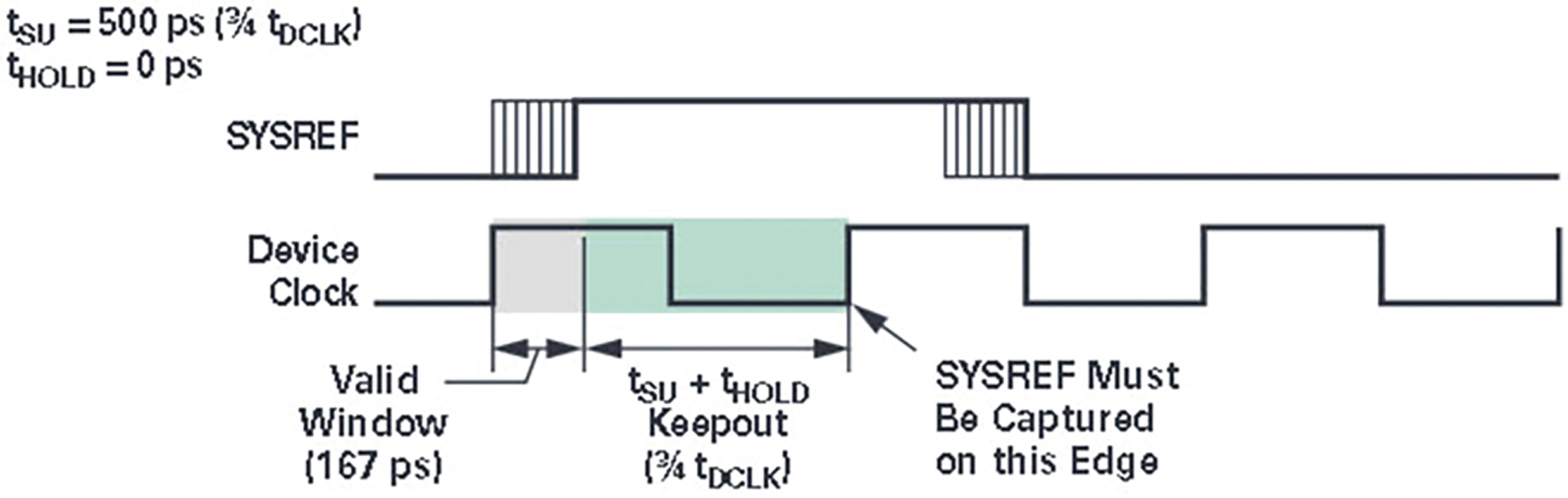

TSU = 500ps和THOLD = 0ps

例如,系統DLUMAX = 1 DCLK(667ps)

滿足SYSREF時序的對內布線長度匹配

根據示例規格,滿足設定與保持時間的「有效視窗」為167ps(667ps TDCLK – 500ps TSU)。傳播時間是訊號離開源電流到達吸電流的時間。SYSREF傳播時間減去DCLK的傳播時間必須低於167ps才能滿足設定時間要求,且必須高於0ps才能滿足保持時間要求。為了大致將此傳播時間的差異轉換為吋(inch)單位,估算在FR-4材料上傳播1吋的時間為167ps。因此,對於系統內的每一對SYSREF/DCLK,須滿足下列路由要求: 滿足此一要求可以保證SYSREF在有效視窗期間進行轉換,如圖4所示。DLU等於元件時脈是滿足SYSREF時序要求的最差情況。

圖4 滿足SYSREF/DCLK時序要求

圖4 滿足SYSREF/DCLK時序要求

滿足DLU限值的對內布線長度匹配

由於DLU限值為667ps,並且已經知道DLU限值和對內(或SYSREF)分布偏斜(DSSYSREF)之間的關係,因此可以直接找出布線長度匹配限值(公式2):

因此,所有SYSREF/DCLK對的對內分布偏斜必須在公式3計算值以內:

...............公式(3)

圖5顯示了此示例的時序。「最佳情況」分布偏斜(DSSYSREF)指的是允許較為寬鬆的布線長度匹配要求。500ps表示SYSREF最差情況下的偏斜,應當用來確定布線長度的匹配限值。

圖5 滿足對內分布偏斜要求

圖5 滿足對內分布偏斜要求

滿足SYSREF時序和DLU限值的先進解決方案

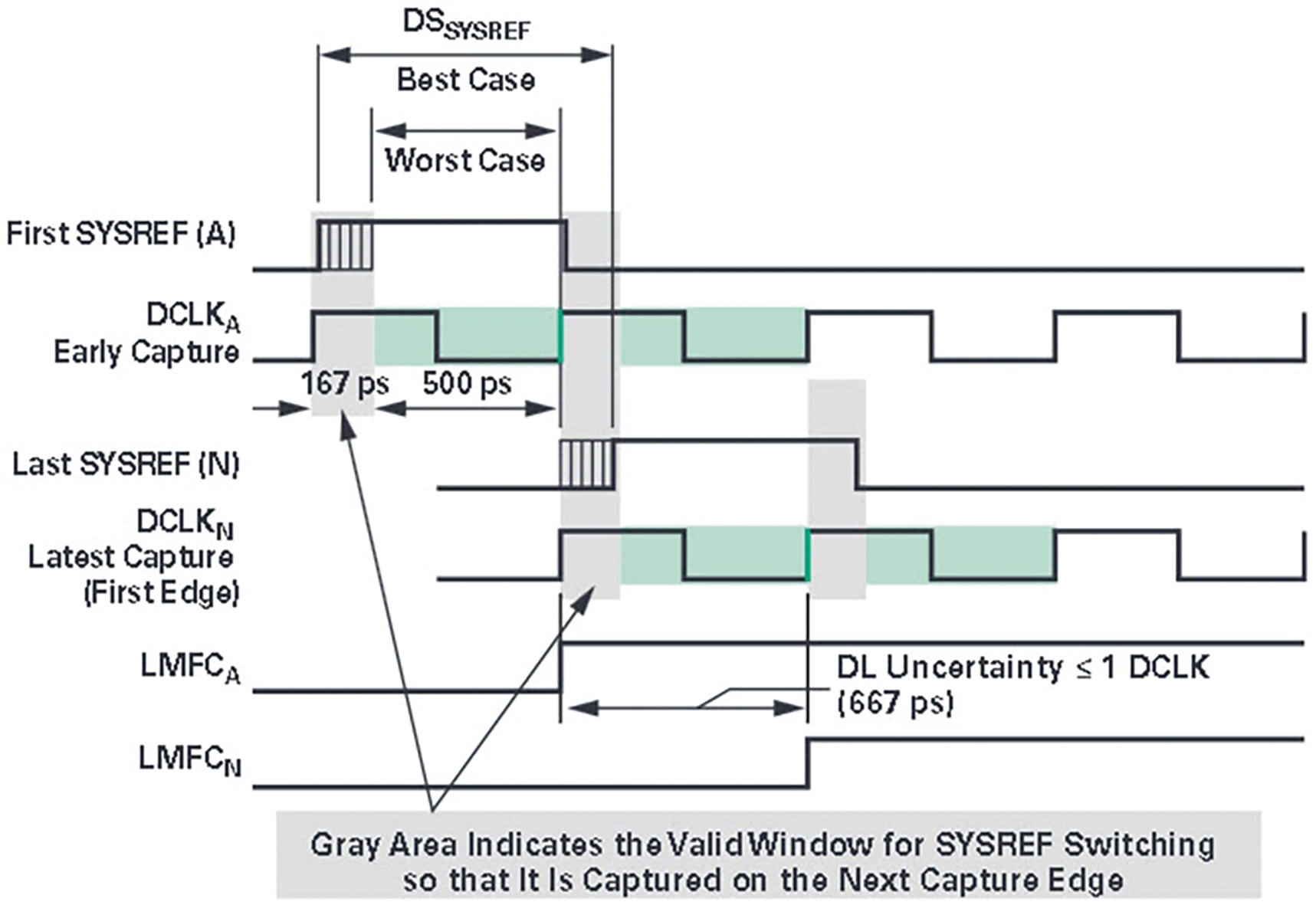

當然,使用較慢的元件時脈可以解決這個問題,使長度匹配變得更容易一些。這樣做會犧牲一些系統相位雜訊性能。與此類似的解決方案是放寬DLU要求;如此可以保留更佳的系統相位雜訊性能優勢。至於DLU要求如何實現則取決於各應用,後文確定性延遲精度相關內容中將討論這些問題。如果需要更高的相位雜訊性能,而DLU要求無法放寬,那可能便無法滿足SYSREF/DCLK元件內偏斜和元件間偏斜的路由要求(就上例而言,分別是1吋和3吋)。這種情況下,需要的是元件時脈和/或SYSREF的可調節相位延遲。根據設定和保持時間,調節解析度必須低於「有效視窗」。示例中的「有效視窗」為167ps。

某些現場可編程閘陣列(FPGA)在滿足較低的調節解析度要求時可能會有困難。然而,AD9528滿足這一要求,因為它能以60ps的步長調節SYSREF相位延遲,且所有輸出的變化低於50ps。圖6顯示如何延遲SYSREF以滿足時序要求,SYSREF以60ps增量進行延遲。建議選擇一個相位設定,將SYSREF邊緣置於靠近有效視窗中央的位置。在圖中,綠色邊緣(2、3)表示相位設置良好,紅色邊緣(0、1、5)表示設置不佳。相位設置為3表示處於有效視窗中央,應在這種情況下使用。

圖6 滿足時序要求的SYSREF可編程相位延遲

圖6 滿足時序要求的SYSREF可編程相位延遲

在SYSREF輸出時不但有60個PS相的級別,而且AD9528裝置時脈輸出有半個時脈週期的延遲。這個特徵對SYSREF的時序要求也是有幫助的。

.SYSREF設定和保持時間監控

亞德諾半導體(ADI)的AD9680可實現SYSEREF設定和保持時間監控電路,協助調節SYSREF和元件時脈之間的相對時序。用戶監控這兩個暫存器,便能確定捕捉SYSREF時是否存在違背時序要求的風險。如果任一暫存器提供時序餘裕不足的指示,用戶就應當調節SYSREF與元件時脈的相對位置。在上例中,透過調節SYSREF相對於元件時脈的相位(例如利用AD9528),或者透過調節SYSREF和/或元件時脈訊號的布線長度,即可實現該操作。

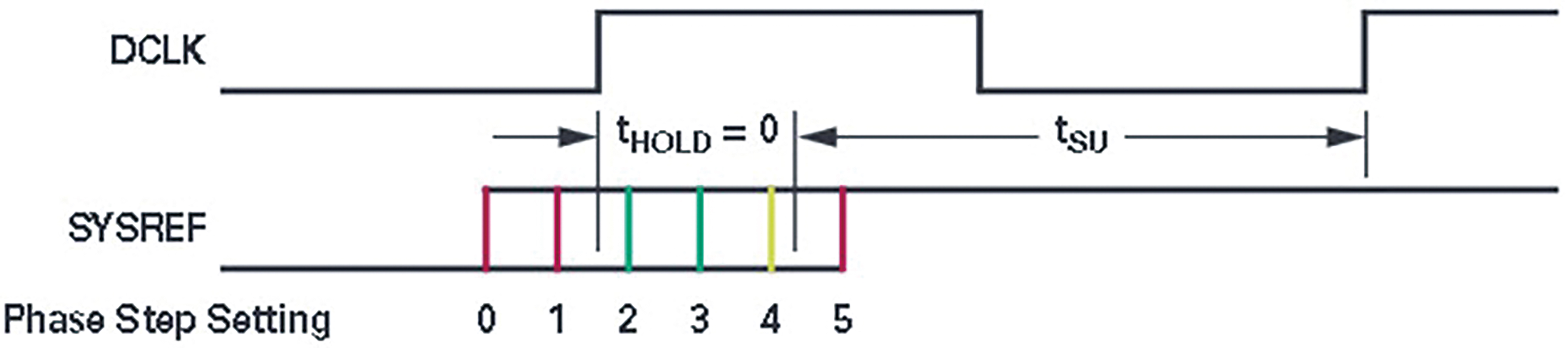

.確定性延遲精度

為了更進一步理解系統的確定性延遲不確定性是如何設定,便須對應用有所瞭解。要求確定性延遲的大部分系統,必須精準知道哪個時間樣本標記目標資料的起始。確定性延遲經常用來同步系統中的多個轉換器,這稱為多晶片同步。在這些系統中,所有轉換器都需要進行樣本對齊。因此,確定性延遲必須具有「樣本精度」。這些系統的DLU應當等於±1/2樣本時脈。元件時脈等於採樣時脈倍數的優勢是,透過樣本精確性來簡化捕捉SYSREF的任務。在採用AD9250的示例中,元件時脈等於採樣時脈的6倍。為了實現樣本精度,±1/2採樣時脈的DLU要求可以轉化為±3元件時脈,如圖7所示。從採用AD9250的示例中可以看到,有了調節每個元件SYSREF相位的能力,則哪怕最嚴苛的DLU要求也能輕鬆得到滿足。當元件時脈為採樣時脈的倍數時,捕捉SYSREF以實現樣本精度將得到極大的簡化。隨著轉換器的採樣速率上升至1Gbps及以上,SYSREF以及元件時脈實現相位延遲的能力將會變得非常重要。

圖7 SYSREF捕捉的「樣本精度」要求

圖7 SYSREF捕捉的「樣本精度」要求

SYSREF捕捉的潛在問題

除了滿足SYSREF設定和保持時間要求以及DUL要求外,還可能存在與SYSREF捕捉相關的其他問題。例如,系統初始上電時,SYSREF可能在系統時脈建立之前就變為有效。使用連續SYSREF訊號時可能會發生這樣的問題。這可以透過在JESD204B介面中引入編程能力來解決;這樣會允許元件在同步時脈以前等待幾個邊緣的時間。另一個編程選項是,讓使用者在預計有效邊緣到達後「配備」SYSREF的捕捉能力。透過這種方法可以控制何時同步連續SYSREF。很多整合JESD204B介面的ADI轉換器(包括AD9625和AD9680)都提供這些功能。

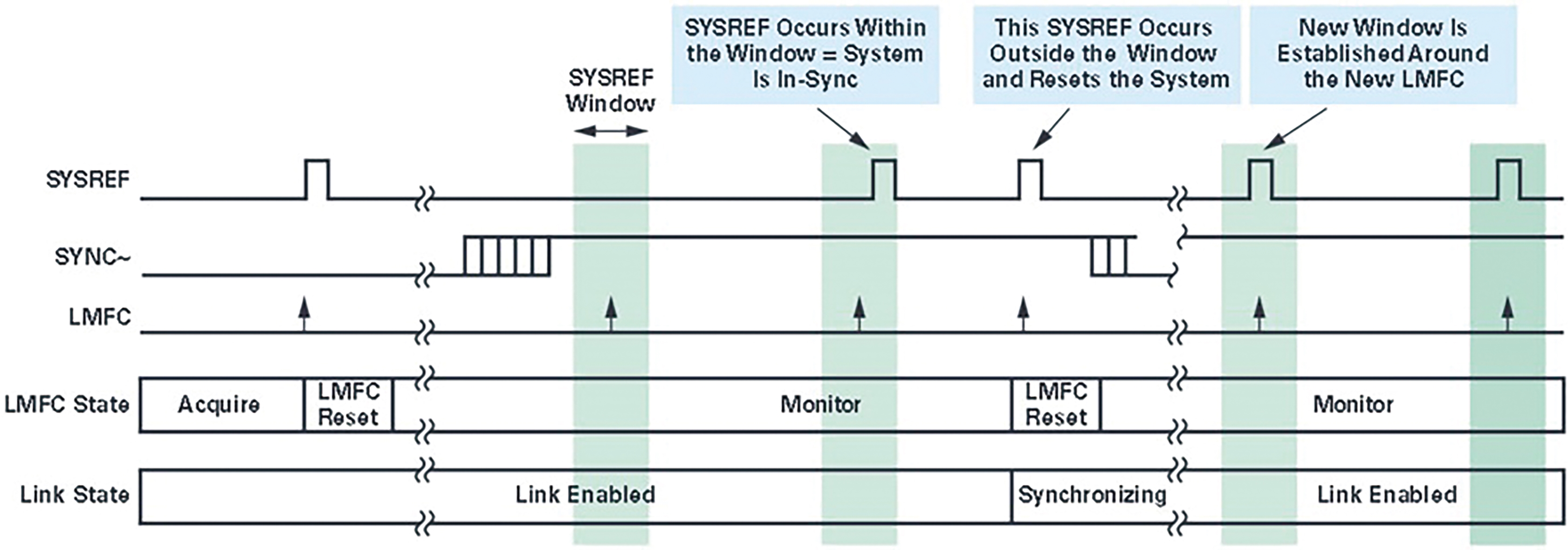

另一個例子是,SYSREF的小幅變動可能會導致不必要的再同步。這可以透過在JESD204B介面中導入編程能力來解決;這樣可以允許用戶為SYSREF邊緣指定LMFC周圍的有效視窗。如果SYSREF出現在此有效視窗內,則系統依然視其為處於同步狀態。這是一個非常有用的功能,因為很多應用監控連續的SYSREF訊號,以確定鏈路狀態。此時,將LMFC邊界與SYSREF進行比較,確定同步狀態。ADI的AD9680整合了此一功能,如圖8所示。

圖8 SYSREF監控視窗

圖8 SYSREF監控視窗

其他有助於SYSREF捕捉的功能包括更改SYSREF捕捉的元件時脈邊緣,以及更改SYSREF用來對齊LMFC的邊緣。很多整合JESD204B介面的ADI轉換器都提供這些功能。

子類2

在子類2系統中,確定性延遲的精度取決於元件時脈和SYNC~訊號之間的時序關係,以及消耗時序預算的各因素;後文將討論這些因素。在子類1中,應用的確定性延遲不確定性容差對於定義該應用的SYNC~以及元件時脈走線長度匹配而言至關重要。

精準捕捉並啟動SYNC~

滿足精確捕捉SYNC~所需時序要求時面臨的挑戰,與子類1的討論中捕捉SYSREF所面臨的挑戰基本相同。然而,由於子類2採用系統同步的時脈方案,因此各捕捉元件無法單獨執行時序分析,並且在多轉換器應用中情況還將變得更為複雜。

不僅如此,還必須考慮到啟動SYNC~訊號後的不確定性。系統中,每一個採用系統同步時脈的元件都將消耗部分時序預算。消耗時序預算的因素有:時脈分布偏斜(DSDCLK)、用於多轉換器系統的SYNC~分布偏斜(DSSYNC~)、SYNC~訊號傳播延遲、每個JESD204B發送器的設定與保持時間要求,以及每個JESD204B接收器SYNC~輸出端的時脈到SYNC~輸出延遲。

子類2中元件時脈上限

JESD204B標準確認採用子類2會限制元件時脈速率,這是因為系統同步時脈方案所導致。標準的附錄B建議此限值為500MHz。 接下來討論一個詳細的時序示例,說明為什麼會有這樣的限制。

子類2多DAC時序示例

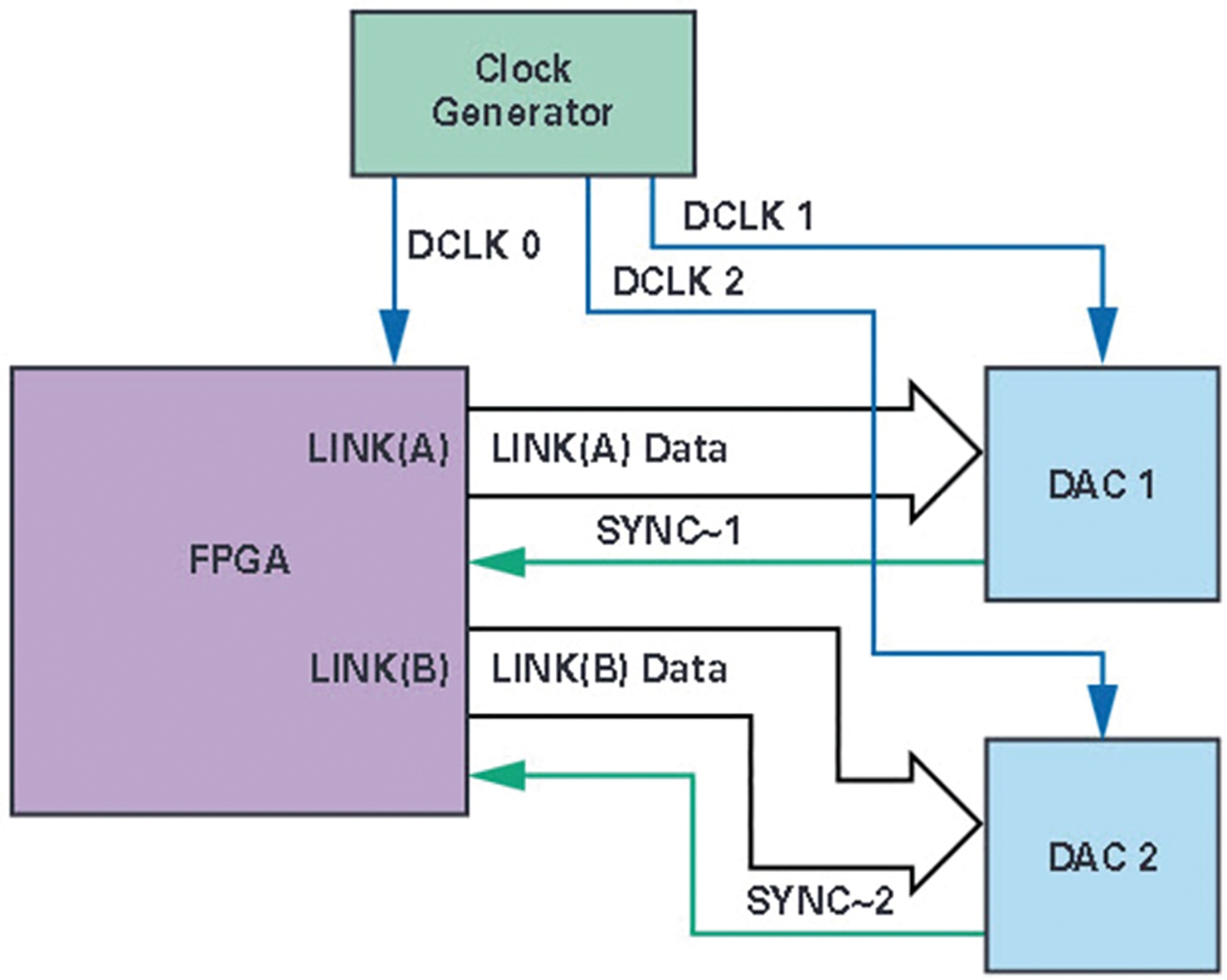

先研究將兩個子類2 DAC元件連接到單一邏輯元件的發送器應用,如圖9所示。

圖9 子類2多DAC應用

圖9 子類2多DAC應用

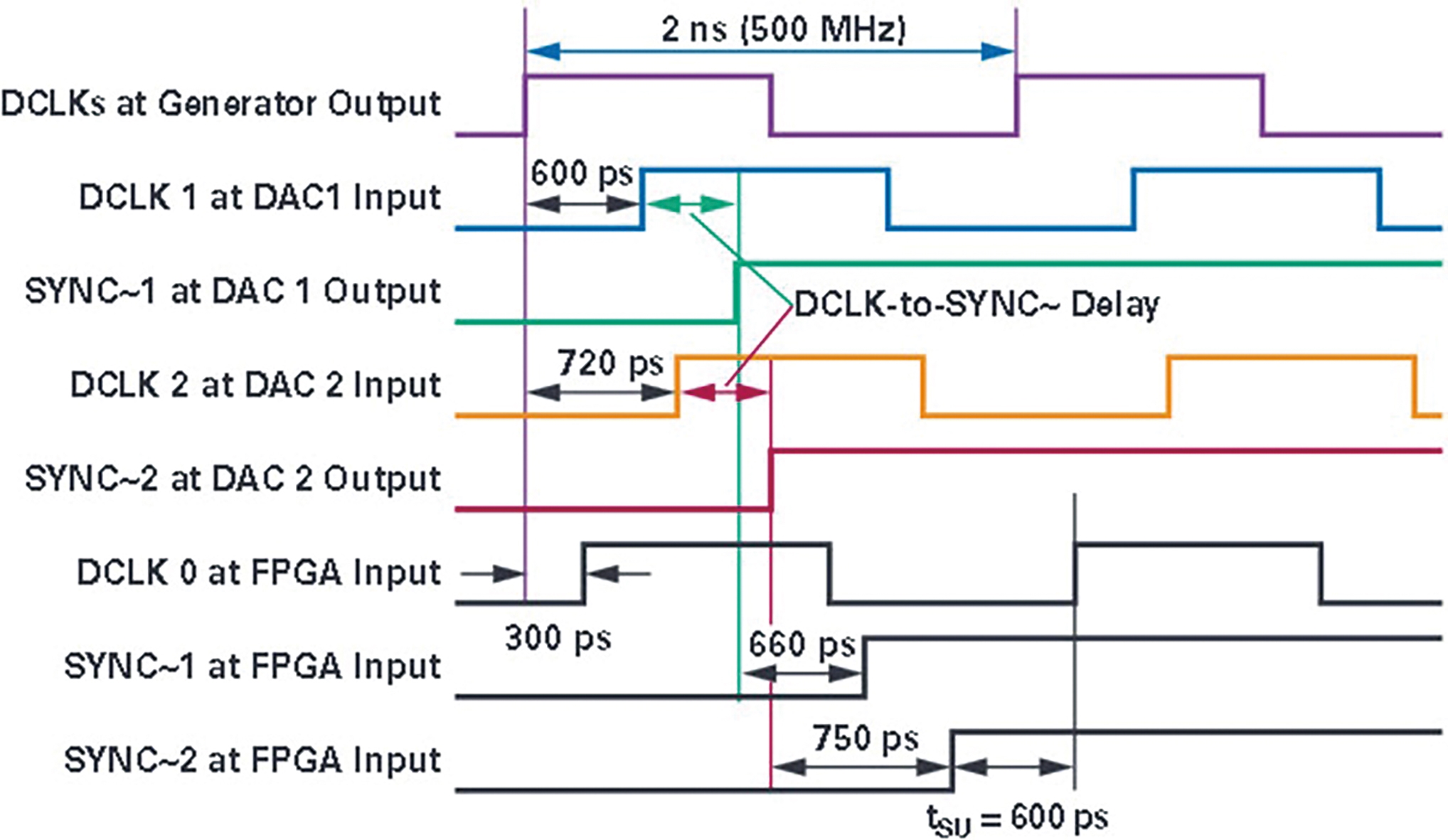

例如,使用500MHz元件時脈。SYNC~和DCLK訊號的PCB偏斜如下所列:

時脈到FPGA = 300 ps

時脈到DAC1 = 600 ps

時脈到DAC2 = 720 ps

SYNC~1到FPGA = 660ps

SYNC~2到FPGA = 750ps

考慮抖動和PVT變化前,時序圖如圖10所示。圖中,最差情況下的時序是在FPGA輸入端捕捉SYNC~2訊號。

圖10 子類2多DAC應用的SYNC~/DCLK時序

圖10 子類2多DAC應用的SYNC~/DCLK時序

在FPGA輸入端捕捉時,DLCK2傳播延遲、SYNC~2傳播延遲以及SYNC~2的時脈到輸出延遲合計產生600ps建立時間。

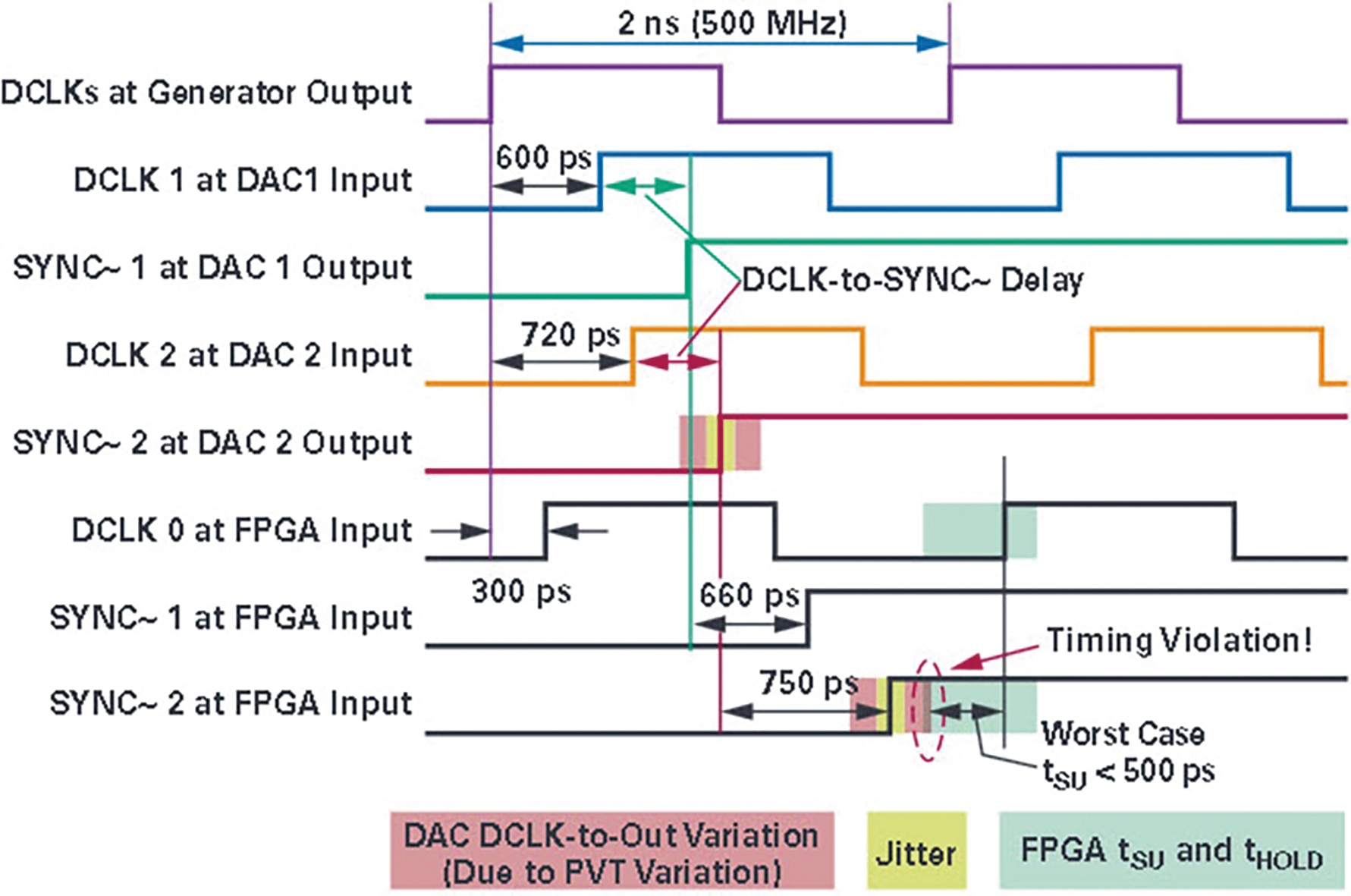

然而,一旦加入設定時間、抖動以及PVT變化,便很容易出現時序衝突,如圖11所示。本例中,設定時間為500ps,PVT變化最多會導入300ps,並且抖動為150ps。在最終到達的SYNC~ (SYNC~ 2)處產生了時序衝突。

圖11 子類2多DAC應用的SYNC~/DCLK時序衝突

圖11 子類2多DAC應用的SYNC~/DCLK時序衝突

在以上示例中,可透過控制布線長度和/或時脈相位調節來解決時序問題。然而,隨著DCLK頻率的增加,滿足時序要求也會變得更困難,難度甚至會超過子類1,因為必須將更多的變數納入考慮範圍。JESD204B標準第6.4部分詳細討論了有關SYNC~捕捉的時序問題。

子類2確定性延遲不確定性

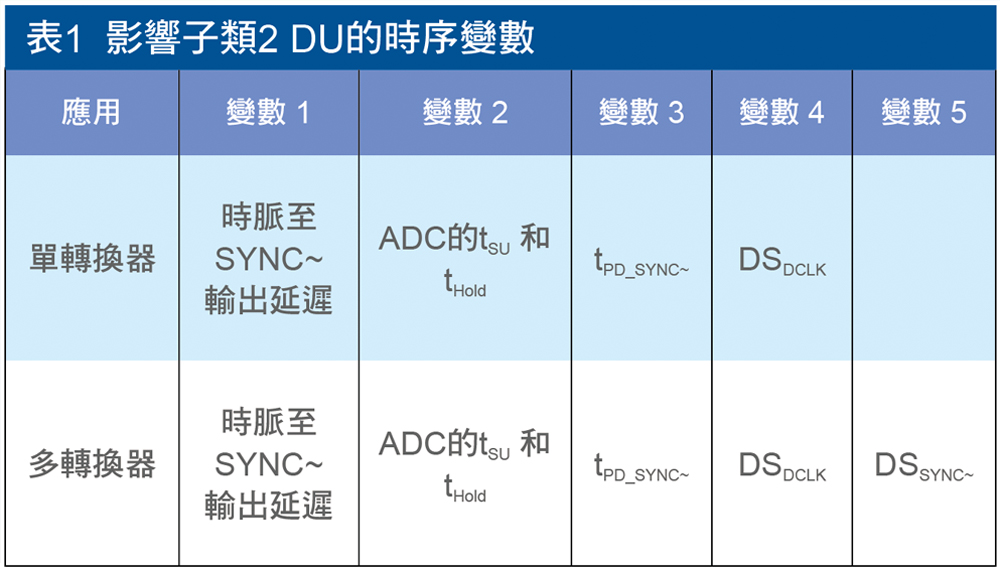

與子類1相同,時序限制將由應用對於確定性延遲不確定性的容差決定。表1總結了系統DLU若要滿足子類2時序要求所須考慮的變數。為保持DLU概念圖示的清晰明瞭,此處未考慮時脈抖動和製程、電壓以及溫度(PVT)的變化。

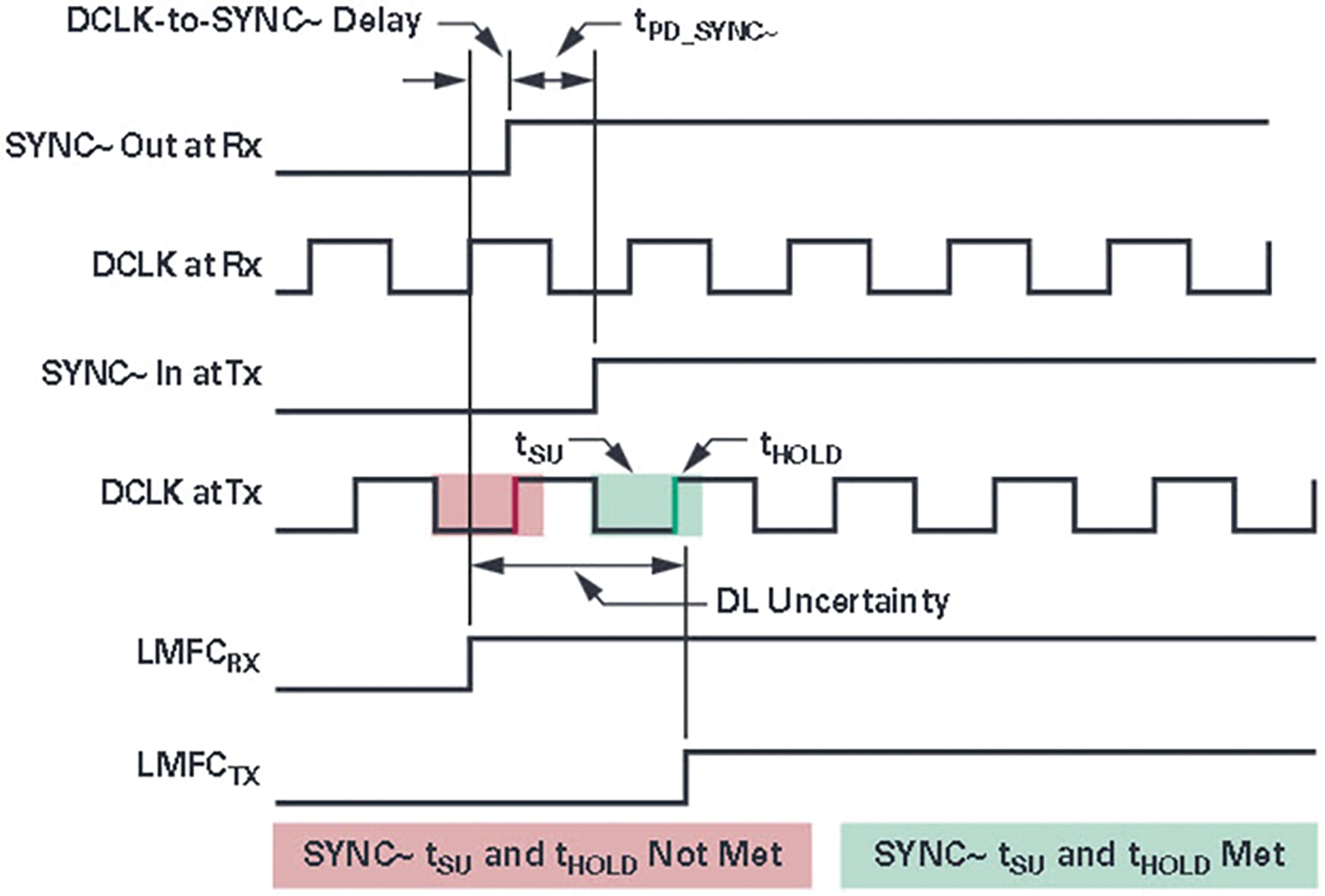

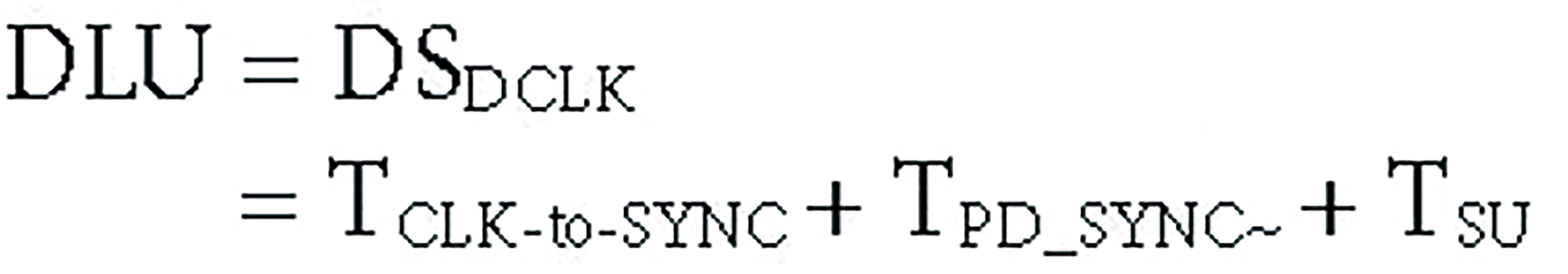

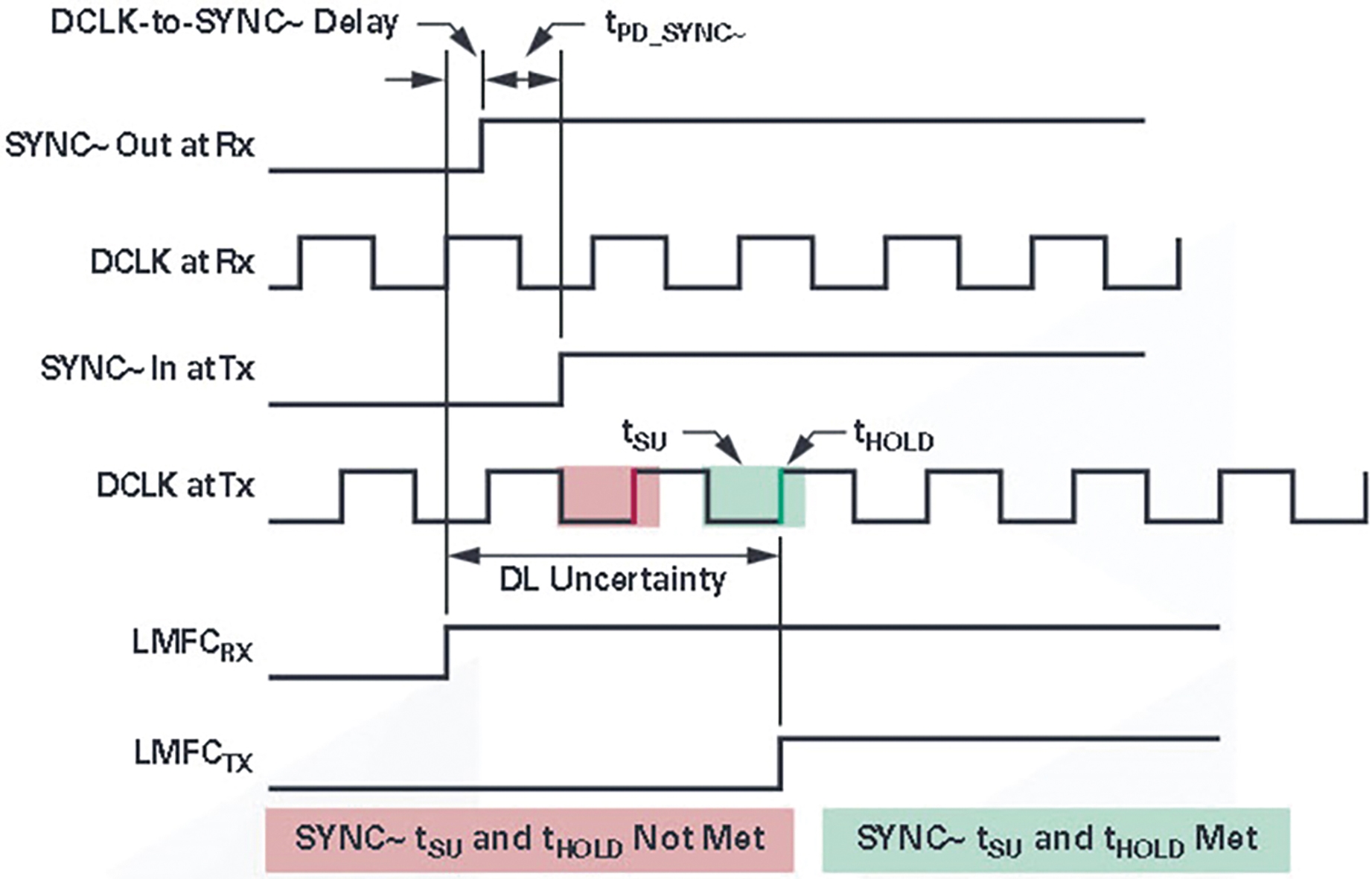

子類2系統中的DLU由TCLK至SYNC、TPD_SYNC~、TSU三者的關係,以及系統中元件時脈的分布偏斜(DSDCLK)所決定。在單轉換器應用中,最佳情況的DLU由公式4提供,並且如圖12所示。

圖12 單轉換器應用的子類2 SYNC~捕捉時序(最佳情況DLU)

圖12 單轉換器應用的子類2 SYNC~捕捉時序(最佳情況DLU)

.....................公式(4)

在圖中,TSU是TDCLK的一半且THOLD是 TDCLK的四分之一。如圖所示,DLCK經偏斜後匹配DCLK至SYNC~延遲和SYNC~傳播延遲,並且剛好滿足設定時間要求。

當發送器的DCLK偏斜不足,且與第一個可用捕捉邊緣的設定時間衝突時,便是單轉換器子類2系統的最差情況DLU,如圖13所示。

圖13 單轉換器應用的子類2 SYNC~捕捉時序(最差情況DLU)

圖13 單轉換器應用的子類2 SYNC~捕捉時序(最差情況DLU)

哪個子類最適合自身的應用

為JESD204B系統選擇哪個子類,取決於是否需要確定性延遲、若需要則精度是多少,以及用於系統中的元件時脈要求。 子類0最容易實現;無需確定性延遲時,可以使用子類0。哪怕目前的多轉換器系統需要同步所有(或部分)轉換器的樣本,也能透過AD9625和AD9680支援的時間戳記功能來實現。

由於子類1支援超高元件時脈速率以及高採樣速率轉換器,對於要求這些高速率的系統來說,子類1是最保險的解決方案。子類1元件也可用於較低的速率。如果元件時脈速率低於500MHz,那麼滿足時序要求便很簡單,無須調節時脈相位。

子類2元件也可用於500MHz以下的應用中。在較低速率下使用子類2的一個小優勢,是它可以減少邏輯元件的IO數,且無須將SYSREF路由至每一個JESD204B元件。

(本文作者為亞德諾應用工程師)