過去幾十年來,電源系統呈指數式增長,其非線性特性引起嚴重的諧波污染。這可能帶來多方面的不利影響,例如電氣設備過熱和過早老化,傳輸線路損耗增加,以及繼電器保護失靈等。

因此,業界越來越關注諧波污染問題,並採取各項措施以實現更好的電網管理。其中,最好的一個方法是在電網內設置更多的觀測和分析點,並且延長監控時間。

用於智慧電表的特殊應用積體電路(ASIC)集電能計量特性與諧波分析功能於一身,可能是最適合的理想解決方案。但考慮到一顆晶片內要嵌入大量數位訊號處理(DSP)資源,同時又必須廉價、尺寸小、功耗低,可想而知頻譜分析絕非易事。本文將討論一種嘗試滿足所有這些需求的DSP架構解決方案。

基頻估算與頻譜成分提取

電網上不斷變化的負載與相對恆定的發電輸出間,存在一種動態的平衡關係,這導致在負載較高時,主電源頻率會略微降低,而在負載較低時,主電源頻率會略微提高。

在電網高度發達並受到密切監控的國家,頻率偏移量相當小,但在電網控制不佳的地區,頻率偏移量可能大到足以影響電氣設備。為此,業界已進行大量研究工作,試圖找到透過優化各種參數如精度、速度、雜訊和諧波抗擾度等,來實現跟蹤頻率的最有效方法。

就電源系統的安全性、穩定性和效率而言,電網的頻率是與電流和電壓同等重要的工作參數。可靠的頻率測量是有效地進行電源控制、負載減輕、負載恢復和系統保護的先決條件。

檢測和估算頻率的方法有許多種。例如,過零方法透過測量兩個相繼過零點之間的時間間隔來檢測頻率,這種方法的優點是非常容易實現,缺點是精度較低,並且易受諧波、雜訊、直流成分等影響。基於離散傅立葉轉換(DFT)的演算法,則可利用採樣序列來估算頻率,但對輸入訊號中的諧波非常敏感。本文所述的DSP架構,採用某種基於數位鎖相迴路(PLL)的方法非常有效,具有高抗擾度,同時還能提供精確的頻率估算。

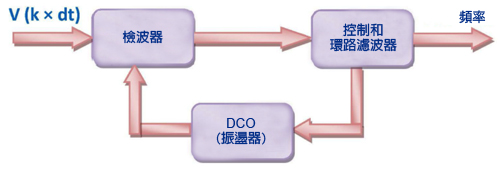

圖1所示為標準數位PLL結構及其三個主要模組。相位誤差檢波器將輸出發送到環路濾波器,環路濾波器進一步控制一個數位振盪器,目的是最大程度地降低相位誤差。因此,最終可以獲得輸入訊號基頻的估算值。控制環路經過優化,在4566Hz的標準電網頻率範圍內可提供最佳的鎖定參數性能。

|

| 圖1 基於數位PLL結構的頻率估算 |

了解須從頻譜中所提取成分的精確頻率後,就可以考察各種用於提取的選項。談到採樣系統的頻譜分析,自然會想到利用DFT這個工具將訊號從時域映射到頻域。有多種數值演算法和處理架構專門用於實現這種變換,快速傅立葉轉換(FFT)是其中最著名的一種。對比考慮提取的訊息量和所需的DSP資源量,每種方法都有其優點和缺點。

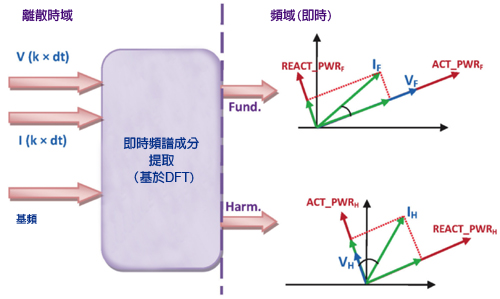

有一種交流電源系統理論使用複平面中的相量(Phasor)來代表電壓和電流,該理論與一種以類似格式提供頻譜成分的DFT變化形式相一致。從根本上說,在目標頻率直接實現DFT公式也能達到同樣的效果。但是,為使測量具有即時性,本文採用一種從DFT公式獲得求和元素的遞迴方法。實作方式有好幾種(取決於可用的DSP資源),但必須最大程度地降低頻譜洩漏和雜訊引起的誤差。圖2以框圖形式說明頻譜成分提取的工作原理。

|

| 圖2 提取基頻和諧波頻譜成分 |

某一相的採樣電壓和電流與基頻頻率值一起通過一個計算模組,該計算模組以相量形式提供計算結果。針對每個基頻頻率和某些使用者可選的諧波頻率,都會提供一對相量(電壓和電流)。有了這些分量後,就可以運用電源理論中的已知方法來提取均方根(RMS)值和功率。RMS值相當於這些相量的幅度,視在功率(Apparent Power)則等於這些幅度的乘積。將電流相量直接投影到電壓上並將兩者相乘,就可以獲得有功功率(Real Power)。分解電流的另一個正交元素與電壓相乘就得到無功功率(Reactive Power)。

接著說明採用即時方法的可能優點(動機),例如這種架構能夠有效地監控變壓器中的浪湧電流。這種電流發生在變壓器通電期間,由磁芯的部分週期飽和引起。初始幅度為額定負載電流的二至五倍(然後慢慢降低),並具有極高的二次諧波,四次和五次諧波也會攜帶有用的資訊。如果只看總RMS電流,浪湧電流可能會被誤認為短路電流,因而可能錯誤地讓變壓器退出服務。為了識別這種情形,必須獲得二次諧波幅度的精確即時值。當只需要幾個諧波的資訊時,運用完整的FFT變換可能不是非常有效。

有選擇地計算幾個諧波成分的方法,可能比FFT方法更有效率,所謂三次諧波序列就是另一個很好的例子。有時須要特別注意三次諧波的奇數倍諧波(3、9、15、21)。在接地Y型系統中,當電流在零線上流動時,這些諧波就會成為一個重要問題。它會引起兩個典型問題:零線超載和電話干擾。有時候,零線的三次諧波序列壓降導致線路到零線電壓嚴重失真,致使某些設備發生故障。本文提出的解決方案可以只監控零線電流以及所有相位電流上的這些諧波。

頂層DSP架構應運而生

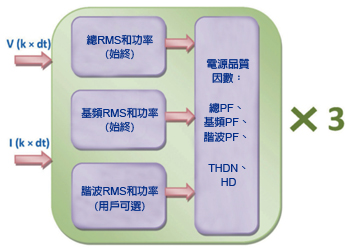

|

| 圖3 頂層DSP架構 |

上述DSP模組已添加到一個根據基本公式計算總RMS值和功率的現有架構。另外,還加入一個用於計算多個電源品質因數的元件。首先,計算諧波失真(HD),以便根據基頻RMS值歸一化所有諧波RMS值。然後,利用總RMS值和基頻RMS值,根據標準定義計算總諧波失真加雜訊(THD+N)。最後,根據有功功率與視在功率的比值,提取所有功率因數。如圖3所示,三個相位並存執行所有的這些訊號處理,但諧波分析模組是例外,任一給定時間只能將該模組分配給某一相位。

透過計算諧波功率因數,可以找出電網中的諧波源。雖然業界仍然對查找主要諧波源的最佳方法存在爭議,但是其中一種傳統方法是基於「有功功率的流動方向」。這相當於確認該特定諧波頻率在系統某一點或多個點上的有功功率符號。在失真電壓下工作時,線性負載會針對每個諧波產生有功功率,而且如果用戶端存在非線性元件,該功率會進入網路。透過測量污染諧波電壓和電流的相位角度,然後計算其差值,可以確定該值。而在此架構中則不必如此,因為諧波功率因數可以提供該資訊。

這種DSP架構已在三相電能計量元件上成功實現,它具有如下硬體資源:單MAC架構、工作時鐘頻率為16MHz、訊號採樣速率為8kHz、具有1k的資料記憶體。所有三相的基頻測量結果連續計算,諧波分析儀則能從給定相位(A、B或C)連續提取三個隨機諧波值。該架構是可擴展的,某些性能參數已根據已知的電網工作條件進行優化。

雖然不能一次性提供所有諧波值看來像是缺點,但電網中的諧波污染最重要的影響還是在於准穩現象。

實際上,對於工業和商用負載,建議分析至少一周內的諧波污染,而應避免任何零星的測量。在上述前提下,憑藉該架構的多功能性,使用者可以透過掃描三相上的所有可用諧波內容來獲取近似FFT的結果。

整合型晶片扮要角

在過去,諧波分析儀不僅非常昂貴,而且難以整合到大規模製造的電表中。因此,對電網進行諧波污染分析是一件非常困難的事情,只能偶爾由專業操作員在某些特定位置進行。將更多訊號處理功能整合到小型且經濟的晶片中,將徹底改變這一現狀,讓電力公司和消費者從中獲益。

(本文作者任職於亞德諾)