在進行電信基礎設施、伺服器和工業應用等產品設計時,工程人員常遇到上電控制、通用輸入/輸出(I/O)擴展、電壓轉換和介面橋接等設計需求。由於市場需求和標準不斷變化,工程人員必須在短時間內調整這些設計,因此有越來越多開發團隊選用可編程邏輯元件(PLD)來實現上述功能。

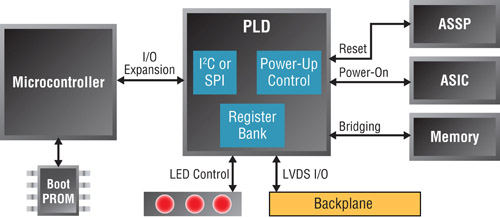

圖1為伺服器中的典型平台管理應用。在這個例子中,可編程邏輯元件扮演平台管理者的角色,負責與微控制器(MCU)、特定應用標準產品(ASSP)、特定應用積體電路(ASIC)、發光二極體(LED)和背板進行通訊。可編程邏輯元件可提供記憶體介面、LED控制、低壓差動訊號(LVDS)I/O等功能,也可對ASSP或ASIC發出系統重設、上電等控制訊號。MCU則利用內部整合電路(I2C)或序列周邊介面(SPI)介面連接到可編程邏輯元件的內建暫存器組,以監測整個系統的狀態。

|

| 圖1 在伺服器應用中使用PLD |

支援多種電壓延伸應用彈性

由於在這類應用中,匯流排橋接和控制邏輯功能必須在系統中其他元件上電之前就進入工作狀態,否則就無法控制其他元件以特定的時序上電,並確保它們能夠正常運行。嵌入式非揮發性快閃記憶體使可編程邏輯元件能在1毫秒內完成上電動作,具備「瞬間啟動」的特性。

值得一提的是,典型的平台管理可編程邏輯元件多半採用輔助電源電壓進行工作,因為這是第一個供電,最後一個關斷的電壓,因此可將PLD的工作時間延至最長。對於許多系統而言,輔助電壓為3.3伏特。用這個電壓直接運行降低了開支,並避免了採用額外穩壓器而增加元件數量。

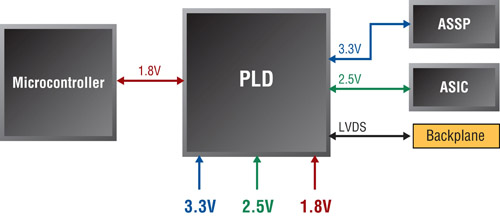

雖然3.3伏特是系統中很常用到的供電電壓,但一個系統內仍有很多仰賴其他電壓提供電源的元件,例如微控制器和其他周邊元件介面,如ASSP、ASIC、記憶體和LED的電壓多半是不同的(圖2)。傳統上,系統設計人員會選用電壓轉換器來執行這一功能,然而,隨著價格不斷探底,可提供3.3~1.2伏特電壓介面的低成本可編程邏輯元件,已經比離散式電壓轉換器更具成本效益。除了成本特性外,可編程邏輯元件還必須很穩定,才能在充滿雜訊的系統環境中工作。這點對於目前的可編程邏輯元件而言,也已經不成問題。

|

| 圖2 使用可編程邏輯元件進行電壓轉換 |

大量I/O與橋接能力有助降低成本

由於電路板上元件數目的增加,提供了不同層次的系統功能,這些元件之間的介面與I/O數目也不斷增加。可編程邏輯元件可用來監測和控制多個元件間的大量訊號。此外,它們還可以與微控制器或ASSP一起使用,增加可用I/O的數量。

在一個系統內,不同I/O介面的元件須互相連接,有時也必須進行轉換。例如I2C與SPI這兩種不同匯流排介面要能互通,就必須使用可編程元件進行介面轉換與橋接。可編程邏輯元件可用於實現流行的介面,如I2C/SPI匯流排控制器、靜態隨機存取記憶體(SRAM)控制器,以及主處理器和其他周邊記憶體的控制器,包括串列電子可擦拭可編程唯讀記憶體(EEPROM)和Compact Flash卡。

可編程邏輯元件可支援各種單端I/O和差動I/O標準。前者如低電壓晶體對晶體邏輯(LVTTL)、低電壓互補金屬氧化物半導體(LVCMOS)介面和運行於3.3/2.5/1.8/1.2伏特的PCI介面;後者如用來與高速介面背板相接的LVDS。目前市面上還有一些可支援類比差動I/O標準,如低電壓正射極耦合邏輯(LVPECL)、縮減擺幅差動訊號(RSDS)和匯流排LVDS的可編程邏輯元件。

為滿足客戶不斷變化的特性和標準的需求,設計人員常常面臨支援高級功能的挑戰,同時還要設法降低總系統成本。整合離散邏輯功能如I/O擴展器、電壓轉換、匯流排橋接轉換器、電壓調節器、時脈產生器和其他配套元件,遂成為許多設計人員降低系統成本的主要手段。可編程邏輯元件可將上述功能都整合在同一元件上,以節省系統尺寸空間,且目前可編程元件已可提供如TQFP和csBGA等極精巧的封裝型態,因此縮小了整體電路板面積,並有助進一步降低系統成本。

遠端現場升級特性漸受青睞

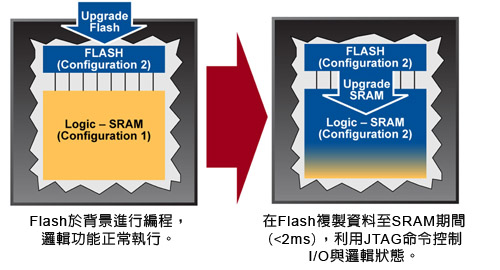

日新月異的標準變化,是驅使設計團隊採用可編程邏輯元件的主因之一。然不可諱言的是,極為緊迫的產品上市時程,也往往壓縮了產品設計人員驗證設計與除錯的時間。有越來越多跡象顯示,終端產品部署到現場後不斷修改版本以進行除錯的狀況已成常態(圖3)。

|

| 圖3 用可編程邏輯元件實現遠端現場升級 |

以往只有軟體能夠用遠端下載更新韌體的方式進行設計除錯,但隨著可編程方案的應用越來越普及,現在硬體開發團隊也可以在產品出貨後針對硬體設計進行現場升級。這是驅動可編程方案普及的另外一大動力。市場上對於已部署到現場的產品進行邏輯更新的需求正不斷增長,因為它使設計人員能夠靈活地應對不斷變化的標準、查找錯誤、對現有設備進行升級,並能盡量減少系統停機時間。一些可編程邏輯元件可透過晶片內建的Flash和SRAM技術來支援這種功能。元件的SRAM控制元件的配置,同時以後台模式更新Flash。元件編程期間通常保持I/O的狀態,以便實現無縫過渡,同時通過從SRAM至快閃記憶體的方式來更新邏輯。

與ASIC和ASSP相比較,可編程邏輯元件提供了能使產品快速上市和設計靈活性的優點,使它們非常適合於平台管理的應用。可編程元件沒有一次性工程(NRE)成本,開發時間也較ASIC更短。ASSP的一次性工程成本較低,因為其使用量龐大,可將成本攤提,但卻限制了設計人員讓產品呈現差異化的能力。

透過可編程邏輯元件,設計人員能夠開發、測試和進行設計更改,而不會帶來任何掩膜成本或設計費用。由於可編程邏輯元件可以重複編程,即使這些元件已經安裝在現場,設計人員仍可在最後一分鐘使用軟體設計工具改變設計和進行產品升級。

完整開發環境不可或缺

為了加速在設計中實施控制和介面橋接功能所需的開發時間,開發工具套件和參考設計為設計人員提供了製作樣機的途徑,並用硬體來實現設計。開發工具套件通常包括擁有可編程邏輯元件及周邊元件的評估板,如記憶體、時脈產生器、編程電纜和設計演示。參考設計為實際的設計提供了一個良好的起點,這些參考設計的代碼用的是硬體描述語言,其中包括可下載的資訊如專案檔和原始碼。

以萊迪思(Lattice)所提供的開發環境為例,該套件可對可編程邏輯元件中的快閃記憶體進行後台編程,同時允許元件繼續工作。新的配置檔可以載入到SRAM邏輯,進行遠端現場升級,並將系統的停機時間減少到最低。

值得一提的是,萊迪思所提供的可編程元件可以採用切換睡眠接腳(SLEEPN)狀態的方式來載入新的配置檔到SRAM邏輯,而不必採用電源迴圈工作方法,因此可實現不停機的更新。在功耗敏感的應用中,睡眠接腳的功能也相當實用,能夠控制關斷電源或使元件處於休眠模式(圖4)。

|

| 圖4 不停機更新概念圖 |

平台管理為低成本PLD主力應用

對實現平台管理功能而言,瞬間啟動、非揮發性可編程邏輯元件是一個理想的選擇,因為這類元件可節省成本、突破ASIC和ASSP的局限性並縮小系統尺寸。

目前業界採用低成本可編程方案來實現平台管理功能的趨勢已經成形,未來在電信基礎設施、伺服器和工業應用等系統產品中,PLD的應用將日漸廣泛。

(本文作者任職於萊迪思)