超寬頻(Ultra Wide Band, UWB)通訊系統的射頻規格制定是相當重要的一項工作,主因是射頻的頻率響應無法理想化,不管是對振幅還是相位而言,其劇烈變化在通帶內(超寬頻第一使用頻段=528×3MHz=4,752MHz-3,168MHz)將會對數位端的數據解譯造成錯誤,這種情況跟無線多路徑通道所造成的頻率振幅與相位劇烈變動其實是很類似的,差別只是一般射頻元件所造成的頻率變化較不劇烈。

為了減輕上述的問題,第一種方式通常是盡可能開出嚴格的射頻規格,但實際上,就算電路成本不高,在互補金屬氧化半導體(CMOS)的介質上,目前射頻製程所能達到的性能是有其局限性。第二種方式就是如何開出合適且可行的射頻規格,並滿足超寬頻通訊系統的要求。相對於第一種方式,後者較適合系統開發工程。下文中,將以中科院電子系統研究所超寬頻實驗室,利用院內系統軟體開發數位與射頻整合模擬初階流程做一研討。

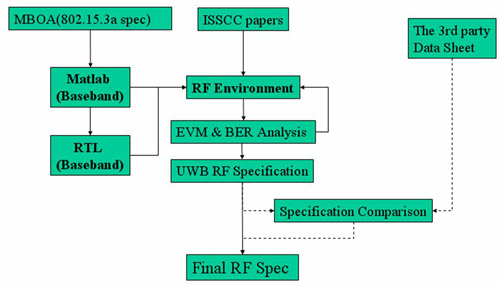

射頻規格制訂發展流程

參考圖1,由IEEE網站下載其802.15.3a規格書,並依據規格書來建構一Matlab環境下的數位發射與接收機。另外也可以採用射頻軟體內的方塊來建構超寬頻的數位發射與接收機。射頻軟體平台主體功能有二:一是作為整合模擬平台,二是提供射頻電路。

|

| 圖1 射頻規格制定發展流程 |

而每年一度在全球IC領域具備指標性地位的國際固態電子電路會議(IEEE International Solid-State Circuits Conference, ISSCC),是國際大廠展示其研發與創新能力的重要場所。該會議所發表的論文重點,除在強調最新商業化晶片的設計突破,也主導整個IC設計產業的方向。若採用知名大廠所發表的ISSCC晶片規格(詳見文末參考資料),作為射頻電路規格的初始狀態,將有利於射頻規格制訂的收斂速度。在系統模擬時所得到的錯誤向量幅度(EVM)和位元錯誤率(BER),與射頻電路的參數設定有關,即越小的接收EVM和接收BER則會有越好的系統性能。故當給定一目標EVM和BER時,射頻電路的規格就可界定。而參數設定的重點在於考慮對各個射頻元件做EVM最適化而非最佳化。最後,若有其他廠商的產品技術資料(Data Sheet),則可拿來做射頻規格比較,可判斷出所制定射頻規格的競爭力。

採用射頻軟體當作系統整合平台,自動引入Matlab的程式碼,再加上利用射頻軟體本身所內建的大量射頻與類比元件庫來建構射頻系統。這種整合模擬方式有幾項優點,首先,Matlab的矩陣運算速度相當快,且內建大量的編碼與數值訊號處理程式,利用Matlab來建構浮點或定點的數位通訊收發器,在系統發展初期,要驗證系統的行為、EVM和BER性能,其所需時間,比利用C語言或System C來開發所需的時間縮減很多。其次,若能採用業界所提供的射頻軟體平台,例如Microwave Office、Ansoft Designer、Advanced Design System,則可與RTL硬體程式整合模擬,提供更好的系統分析。最後,射頻軟體平台呼叫Matlab的模擬引擎,且連接的使用介面相當容易,而其本身也是相當強大的射頻電路開發環境。

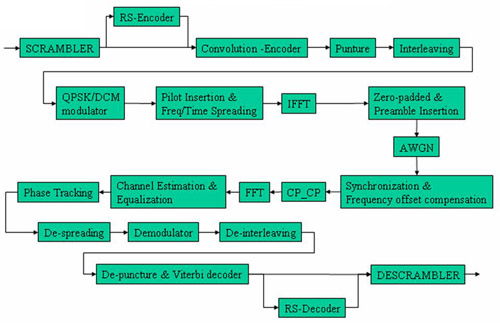

建置超寬頻數位發射機與接收機

Matlab數位接收與發射機的方塊如圖2,每一個模塊會相對應到一段Matlab程式碼,利用數個區塊來將數位收發系統建置完成,並用以模擬射頻元件的EVM貢獻。此方式的優點是每一個訊號處理區塊可用Matlab實現或C程式語言實現,而這樣的切割方式對於在發展RTL數位硬體程式時,可節省許多連接介面定義的時間。

|

| 圖2 超寬頻數位發射機與接收機方塊 |

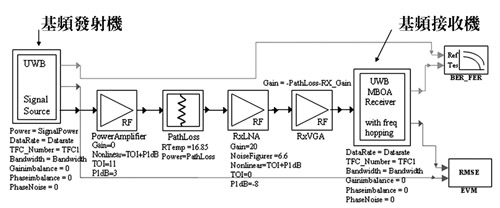

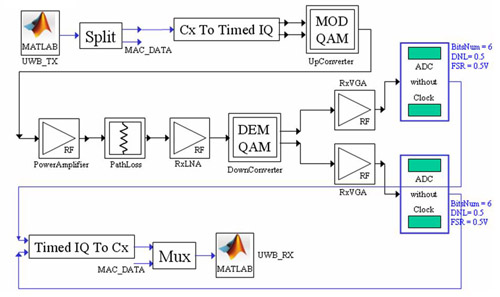

圖3為超寬頻驗證平台的方塊圖,含有數位發射和接收機、射頻電路和無線通道,可作為射頻非理想效應對系統BER及訊框錯誤率(FER)的影響模擬。其中發射端射頻電路的振盪器、IQ升頻器被包含在區塊基頻發射器(Baseband Transmitter)內,而接收端射頻電路的IQ降頻器和振盪器被包在區塊基頻接收器(Baseband Receiver)內,故圖上可視的射頻電路有發射端功率放大器,接收端低雜訊放大器,以及可控增益放大器。

|

| 圖3 超寬頻驗證平台方塊圖 |

在此必須注意的是,原本應該將可控增益放大器放在IQ降頻器的後端,並且I路徑和Q路徑都各需一個可控增益放大器,但因為可控增益放大器在此的作用是補償無線傳輸損耗值,使在類比取樣電路之前的訊號電壓幅度仍落在所需的電壓振幅變化範圍。再者,因IQ降頻器的IQ不匹配效應乃線性方程,故可將IQ降頻器後端的兩個可控增益放大器移到IQ降頻器的前端,並減少至一個即可。這樣的電路架構是為了模擬方便且不影響系統性能,但在實際電路製作時,仍須在IQ降頻器後端置入兩個可控增益放大器,而非放在IQ降頻器的前端。

至於無線通道的熱雜訊和損耗效應則由圖上標示PathLoss的圖塊表示,此圖塊可精準模擬室溫的熱雜訊和無線傳輸損耗。路徑損耗值定義為:PathLoss=-20×log10(4×pi×fc/3e8)-20×log10(d);其中d為距離,fc為射頻載波操作頻率。

因從Baseband Transmitter所送出的功率已經符合超寬頻定義的-10dBm功率,故圖中發射端功率放大器的設定主要著重在P1dB和TOI。增益下降到比線性增益低1dB時的輸出功率值定義為輸出功率的1dB壓縮點,用P1dB表示。三階截點功率是描述放大器線性程度的一個重要指標,用TOI表示,其典型值通常比P1dB高8dB以上。

接收端的低雜訊放大器除了須設定P1dB與TOI以外,還須設定雜訊指數為6.6dB,以符合超寬頻系統規格。至於IQ升頻器和IQ降頻器所需的I與Q兩路徑不匹配設定,則有振幅增益和相位不匹配兩項。而因IQ升頻器與降頻器分別在圖中標示Baseband Transmitter與Baseband Receiver的方塊內,故不匹配的參數設定也就傳遞到此兩個方塊內。最後,圖3右上所用的區塊BER_FER用來得到BER和FER的模擬結果,而右下角的RMSE區塊則用來得到EVM的模擬結果。

超寬頻規格書支援八種資料傳輸速率,分別為53.3M、80M、106.7M、160M、200M、320M、400M及480Mbit/s。不同的傳輸率,會採不同的數位調變、頻率擴展(Frequency Spreading)與時延擴展(Time Spreading)方式。越高速的傳輸率,其對EVM要求也越嚴格。

超寬頻技術資料內有定義發射端在傳輸速率rate 200以下EVM需為-17dB以下,而在rate 320、rate 400、rate 480的EVM則需-19.5dB以下。技術資料內也建議一些設計的考量重點,例如IQ-不匹配、DC偏移和相位雜訊。但一般在設計的時候,都會加一些緩衝值,使得設計規格更嚴謹,用以提高系統穩定度。

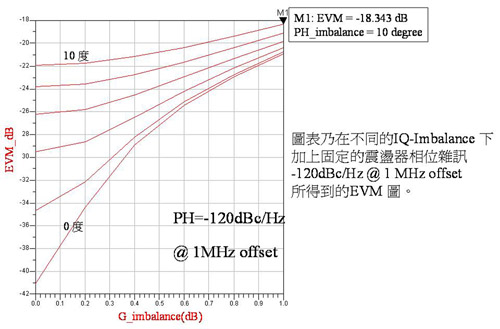

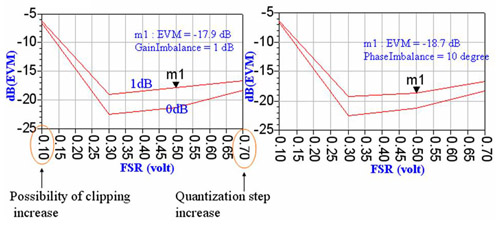

模擬EVM時,先設定數位端操作在rate 200,其他設定為標準模式。而對射頻系統的設定則變化一個射頻元件參數,然後理想化其他射頻參數。所以得到當振盪器的相位雜訊小於-105dBc/Hz@1MHz Offset時,EVM小於-38dB。發射功率放大器的非線性特性P1dB與TOI對系統EMV的影響,可參考圖4。因考慮系統EVM至少要小於-38dB,所以制訂P1dB為3dBm,TOI為11dBm。而升或降頻器的不匹配對EVM影響效果可參考圖5,由圖中所得的最糟狀況乃增益不匹配1dB,且相位不匹配10度時,EVM只比-18dB小一些,算是非常差的系統性能。但因為考慮到升降頻器在實際製作時所面臨的困難,所以仍制定此元件增益不匹配需在1dB以內,相位不匹配10度以內。而後將對升/降頻器做IQ不匹配的校正使EVM至可接收的範圍。目前已知的方法有兩種,一是在射頻上做自動校正,二是在數位發射和接收端來分別做校正。本文後段會介紹對發射端作IQ升頻器不匹配的數位校正結果。

|

| 圖4 發射功率放大器非線性特性對系統EVM的影響 |

|

| 圖5 升/降頻器的不匹配特性對系統EVM的影響 |

圖6描述當系統採用五位元的類比數位轉換器(ADC)時,對ADC的輸入訊號電壓做一動態參數變換。已知降頻後所放大的超寬頻類比訊號,在無回授控制可變增益放大器(AGC)的狀況下,其於取樣電路ADC的輸入端電壓是有一固定變動範圍稱為Vp-p,其值為最大正壓訊號減去最大負壓訊號得之。一般為了避免訊號被截波,維持訊號的線性度,故ADC輸入端的FSR(Full Scale Range)必須大於Vp-p。但又考量到系統效能,故FSR是不可遠大於Vp-p,否則量化雜訊會過大。因此決定ADC的FSR與超寬頻類比訊號Vp-p的比例關係,並用AGC電路來維持此一比例,是系統工程師的重點工作之一。從圖6可觀察到當FSR接近0.1伏特時,Vp-p為0.5伏特,超寬頻時域訊號發生截波的點增加,截波之後的頻譜相當於將超寬頻訊號頻譜與矩形視窗之頻譜做卷積(Convolution),因矩形視窗頻譜緩慢下降之特性,造成超寬頻頻帶增長(Spectrum Regrowth),進而劣化系統的EVM。

|

| 圖6 ADC的輸入FSR對系統EVM的影響 |

圖7是採用Matlab所建構的數位發射機與接收機,再加上射頻電路與類比電路。此驗證模擬速度非常快,因數位發射機與接收機均是在Matlab環境下建構完成,唯一會降低模擬速度乃是射頻軟體平台。在此圖中,所採用的升頻器方塊內有內建操作頻率的設定,但無相位雜訊的設定。因考慮到相位雜訊在約-105dBc/Hz@1MHz偏移時,對系統的EVM性能影響不大,故此模擬方式仍然維持足夠的可信度,且額外的優點是省略模擬相位雜訊效應對模擬速度的提升有很大幫助。發送端的Matlab程式內有數位類比轉換器(DAC)程式,而ADC設定則須注意的有位元數多寡和微分非線性(Differential Nonlinearity, DNL)。DNL Error差值介於實際的步階寬與理想的1最低效位元(Least Significant Bit, LSB;1LSB=2VRef/2NBits)。理想ADC,DNL=0LSB,步階寬等於1LSB。DNL參數設定,用來設定最大的DNL值。DNL Error<1 LSB保證無Missing Codes。

|

| 圖7 Matlab基頻與射頻電路共同模擬環境 |

|

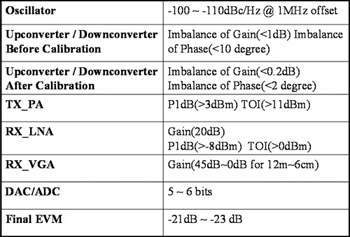

| 表1 超寬頻射頻系統最終規格 |

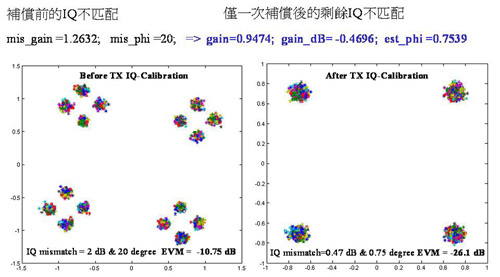

圖8中為超寬頻實驗室利用數位演算法對射頻發射端的升頻器做IQ不匹配補償校正。此方式須將射頻發射端與接收端對接,在此六位元的DAC與ADC下,只用一次校正的性能就已經得到增益不匹配由原來的2dB下降至0.47dB,相位不匹配由20度下降至0.75度,且系統接收端的EVM由原先的-10.75dB改善至-26.1dB。若採用反覆式的校正,補償後的殘餘誤差會更小,而代價是校正的時間會變長。最後,經由第一階段模擬所得到的資料,可歸納出射頻電路規格,列於表1。

|

| 圖8 Constellation of TX Upconverter IQ-Calibration |

射頻規格制定攸關數位電路設計

超寬頻實驗室在開發初期,模擬出射頻元件的非理想效應對超寬頻接收系統EVM的影響,並經由模擬得到的接收端EVM,找出最適合的射頻元件規格參數。模擬的元件參數包含有發射功率放大器的非線性失真(P1dB及TOI),接收低雜訊放大器的雜訊指數(NF)及非線性失真(P1dB及TOI),升降頻器的增益與相位不平坦,接收及發射震盪器的相位雜訊問題,最後還有DAC和ADC的位元數取捨的問題。

模擬得到接收端EVM顯示,當振盪器的1MHz Offset相位雜訊介於-100dBc~-130dBc/Hz時,系統性能劣化不大,所以振盪器的規格有較大的彈性設計範圍;至於升/降頻器的規格,訂為須經數位或類比方式校正至增益不平坦為0.2dB以內,相位不平坦兩度以內;功率放大器的P1dB規格為3dBm,TOI為11dBm,均為國內外廠商所能達到的規格;接收端低雜訊放大器的增益為20dB,P1dB為-8dBm,TOI為0dBm則屬較嚴苛的規格,這是為了防止接收端的輸入過大造成放大器飽和的現象過於嚴重。但若為了電路設計考量,因而必須降低接收端低雜訊放大器的P1dB,則發射端必須做發射功率控制,來減輕接收端的飽和問題。ADC和DAC可接受的位元數為五至六,當選擇六位元或更高時,數位接收端的設計可使用較簡單且面積小的演算法電路來達到系統性能要求;而當選擇五位元或更低位元時,相對的,數位接收端的電路設計,將因上述元件在所引入的失真過大的狀況下,而使數位電路設計與面積過於複雜和龐大,甚而發生解譯崩潰。

綜合上述的分析結果,在射頻規格制定時,因牽涉到實現與量產的問題,故必須要連帶與數位設計端一起考量,而非單獨的切割,彼此分開獨立制定規格參數。藉由整合模擬的幫助,能快速得到最適化的規格選取方式,進而加快系統開發,避免失敗。

(本文作者任職於中山科學研究院電子系統研究所超寬頻實驗室)