了解為當今高解析度、高幀率CMOS圖像感測器設計供電方案的關鍵挑戰,是設計一個滿足每位設計工程師要求,並且含LDO(DC-DC, PMIC)的優化電源系統方案的關鍵要素。

電源系統設計人員需要知道不同應用中的電源配置有何不同,比方說,一個8百萬畫素(MP)的相機與一個50MP的相機的電源配置有何不同,或幀率的不同(30fps、60fps、120fps)如何改變電源設計,多大頻率需要高電源抑制比(PSRR)等。本文強調在為任何圖像感測器確定供電方案之前的基本考量。

CMOS成像系統組成

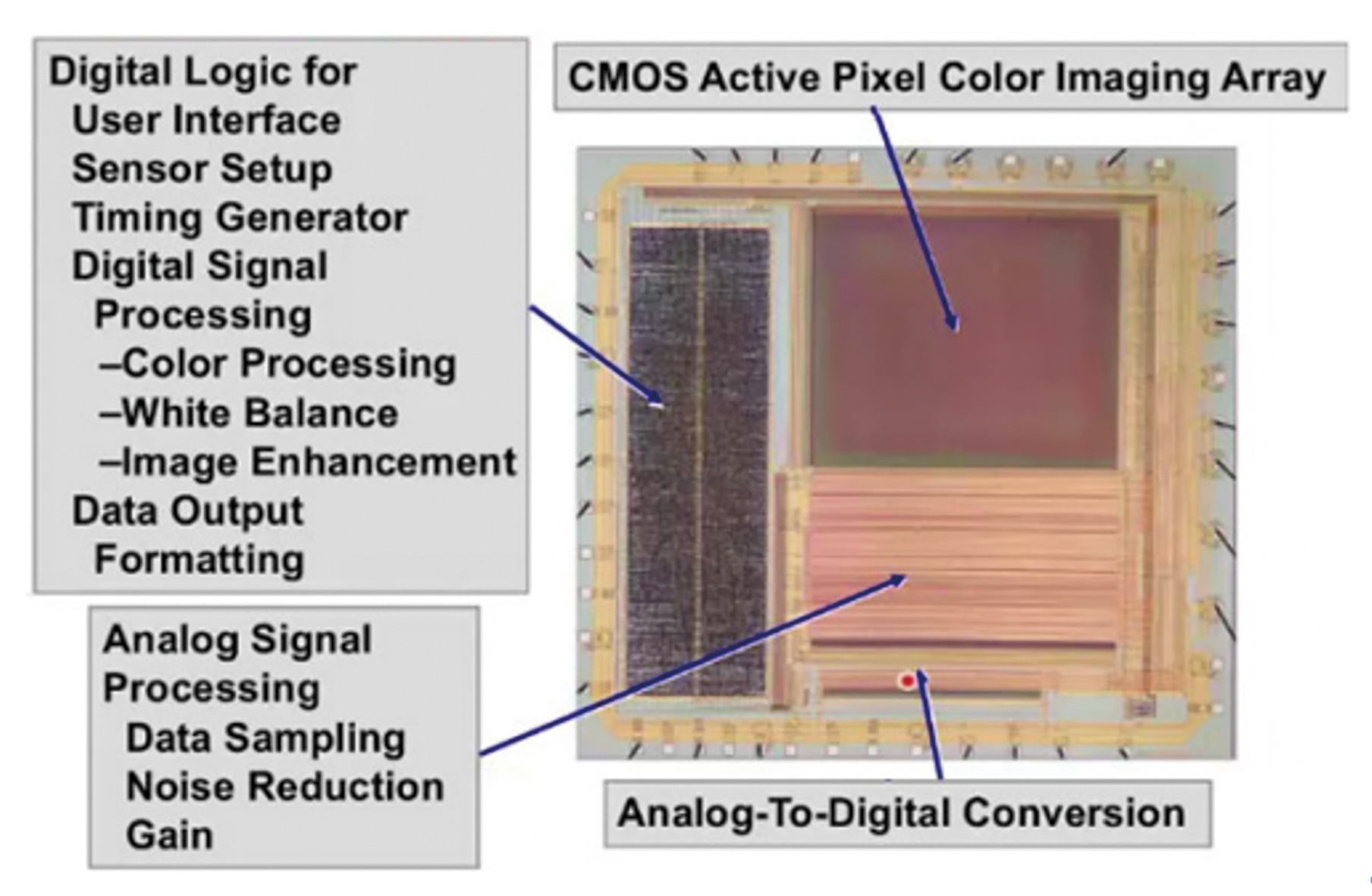

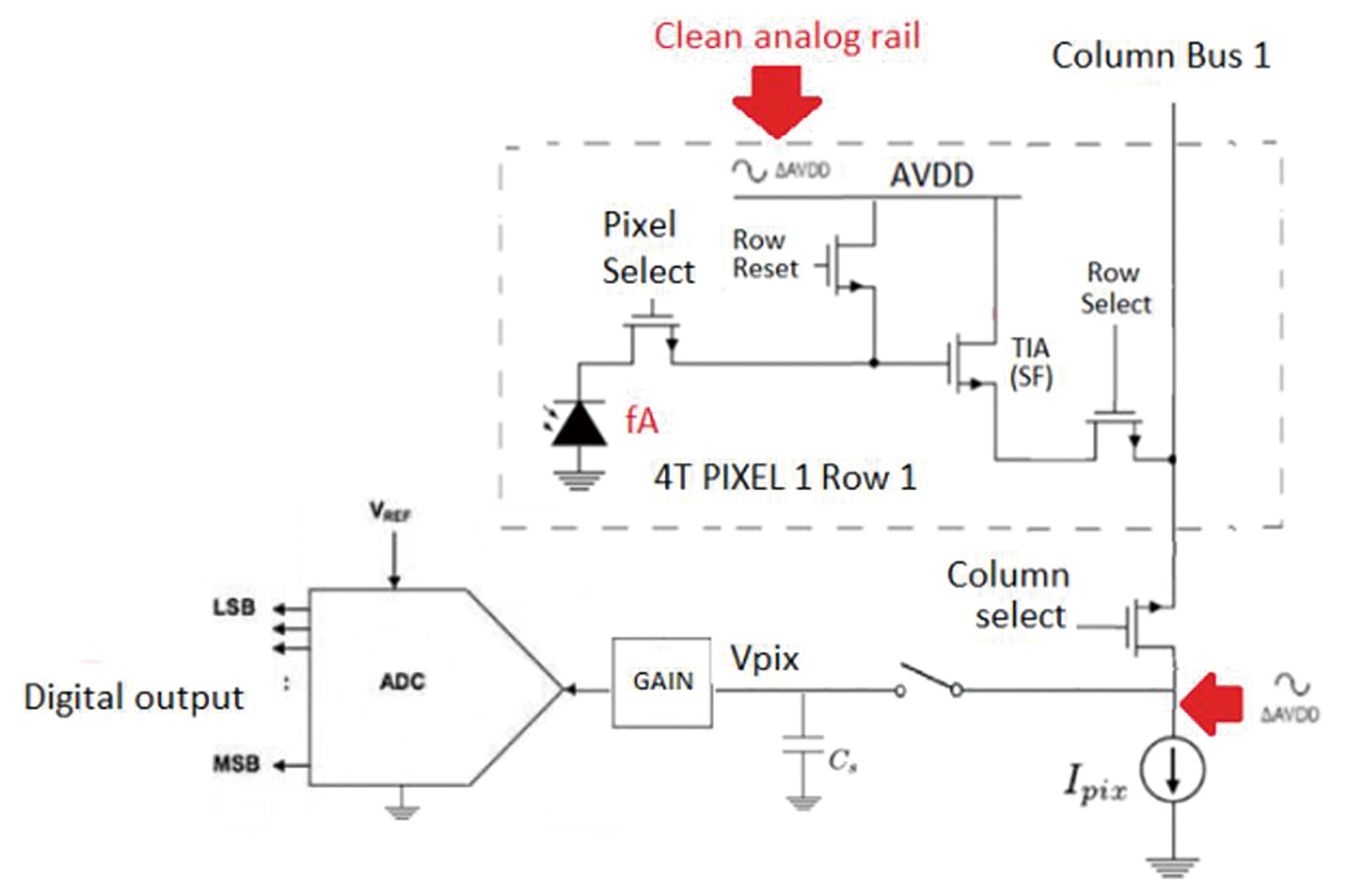

任何CMOS成像系統都含一個主動畫素區和光電探測器,光電探測器用於捕獲光子並將其轉換成非常小的光電流或電子。不同的部分將會讀取資料,包括ADC、類比訊號處理、使用者介面數位邏輯和計時等。在飛安培(Femto Amp,或稱微微安培)範圍內的少量光電二極體電流在曝光時間(打開快門)內整合成少量的電荷,由ADC轉換成可讀的電壓(圖1)。

圖1 典型的CMOS成像儀結構

圖1 典型的CMOS成像儀結構

畫素、解析度和電晶體設計

每個畫素也有一個填充係數,取決於使用的總畫素區域的百分比,並有兩個部分:光敏和非光敏。光敏區捕獲光線;而非光敏區則用於ADC、數位區塊、介面和其他功能;其餘區域用於水平或垂直讀出,其中典型的READ或WRITE序列由主機開始,在匯流排上產生一個啟動條件。

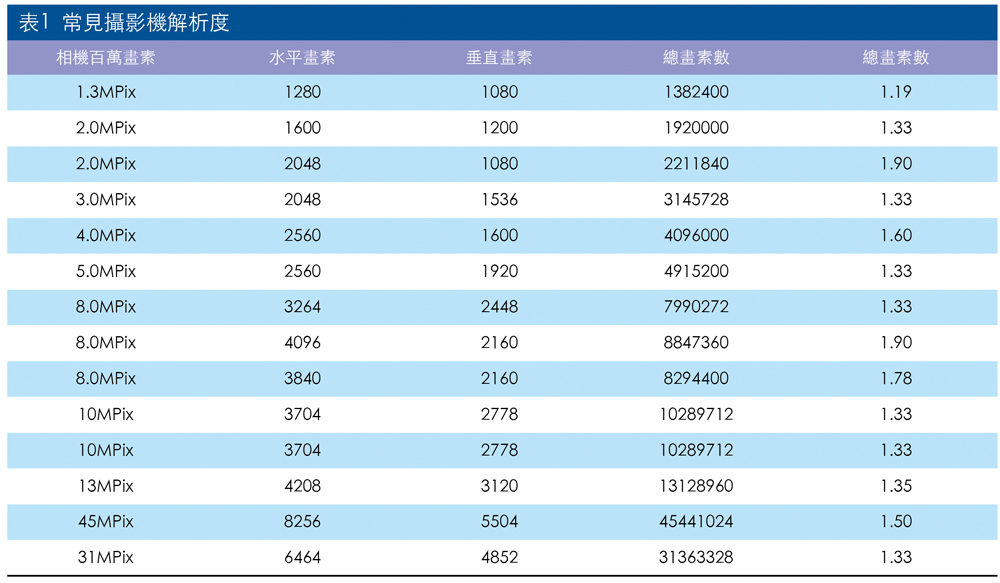

CMOS圖像感測器的解析度是總的畫素陣列數,畫素陣列由許多列和行組成。例如,一個典型的2百萬畫素的相機畫素陣列可能是1,600×1,200(表1)。列和行上的一些畫素稱為暗圖元,在光學上是黑色的,在內部用於黑電平校正或行雜訊校正,這將導致實際主動畫素陣列或陣列中實際有效畫素減少。

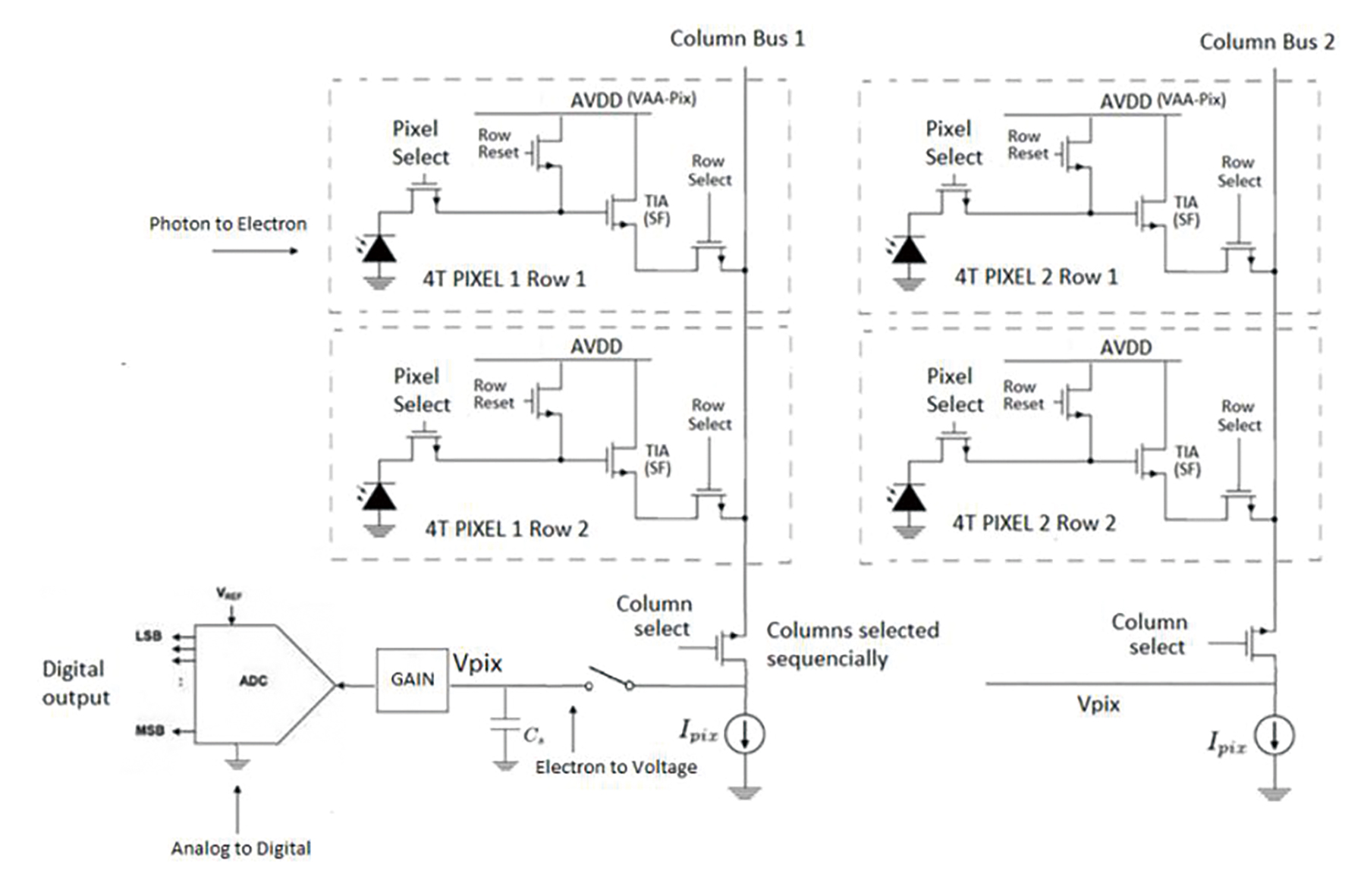

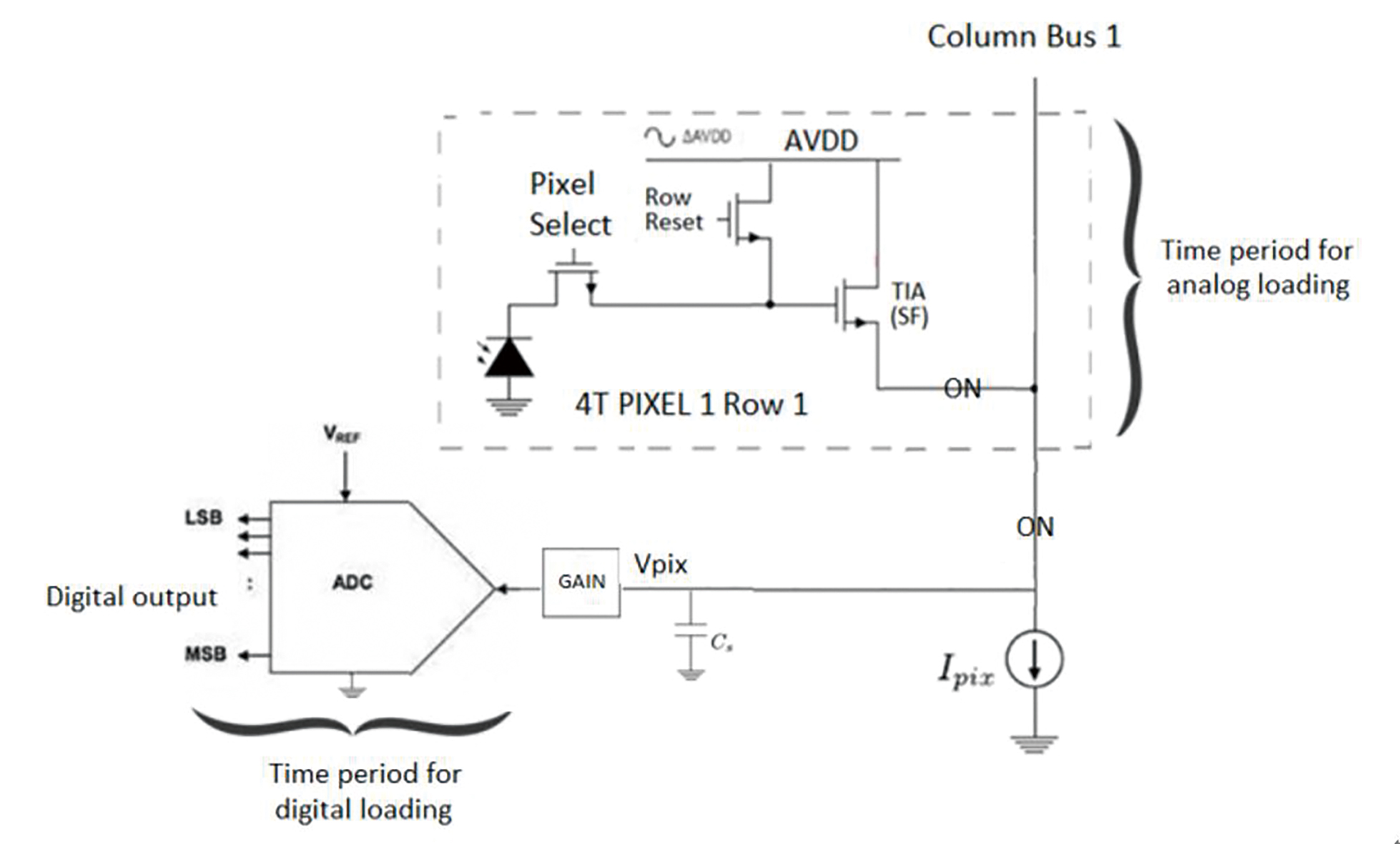

設計工程師可採用許多不同的畫素電晶體設計(3T、4T、5T),如圖2所示的四電晶體(4T)畫素設計。光電二極體將接收到的光子轉化為少量的電荷,有一些開關用於選擇不同的列和行。為了不干擾光電二極體的讀數,光電二極體結點上的高阻抗放大器將作為源極跟隨放大器(TIA/SIA Amp)使用,以便驅動每列匯流排。

圖2 四電晶體設計示例

圖2 四電晶體設計示例

每個畫素電壓一次讀取一行並放入列電容器(Cs),接著使用列解碼器和多工器進行讀取(圖3)。

圖3 選定行和列的示例

圖3 選定行和列的示例

幀和行轉換

幀率衡量的是捕獲一個完整的圖像並讀出陣列以進行處理的速度,典型的頻率範圍是30~120赫茲(Hz)。圖像感測器可以是用於慢動作重播的高幀率元件(>60幀),或用於運動模糊效果的低幀率元件(<60fps)。

速率也可能受到快門速度的限制或影響,快門速度控制著圖像感測器收集光線的時間,或在最後一行用於水平消隱、同步時間或其他目的後發生的、稱作「暗期」的可程式設計時間間隔。

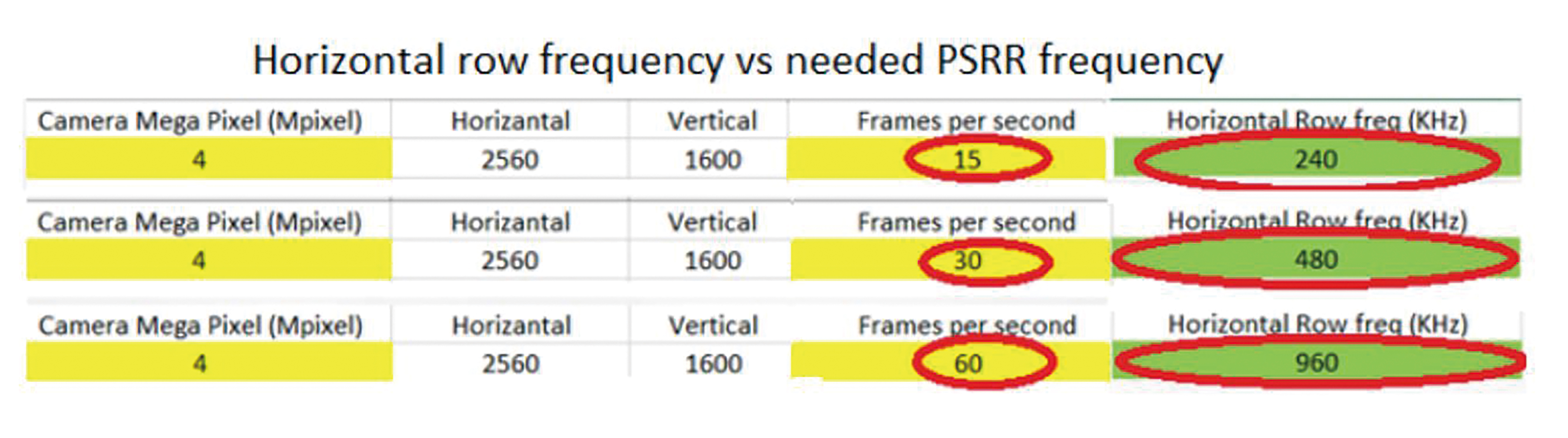

此外,還可以計算出一個給定幀率(15、30或60)所需的最高電源抑制比(Power Supply Rejection Ratio, PSRR)頻率。例如,4百萬畫素相機和設計一個具有所需PSRR的LDO,用於計算頻率(圖4)。

圖4 不同畫面播放速率與水平頻率的影響

圖4 不同畫面播放速率與水平頻率的影響

畫面播放速率約為讀出速率的75%,另外25%作為其他處理的餘裕時間,如改變光圈、曝光時間計算、鏡頭自動對焦(AF)、影像處理、記憶體寫入速度等。對於靜態圖像和影片,幀讀出以行序列方式進行,最後整個幀收集在緩衝區中並呈現出完整的圖像。

圖像感測器電源軌

CMOS圖像感測器通常需要三個不同的電源軌來為類比軌(AVDD)、介面(DOVDD)和數位軌(DVDD)供電。用於類比電源軌的標準電壓是2.8V,介面電源軌是2.8V或1.8V,而數位電源軌是1.8V或1.2V。

為了改善CMOS圖像感測器的雜訊性能,可在電源引腳前放置一個大的旁路電容。減少每個電源軌的波動還可改善CMOS圖像感測器的雜訊性能。一般來說,類比電源軌是對雜訊最敏感的軌道,其次是數位軌,對雜訊也很敏感。

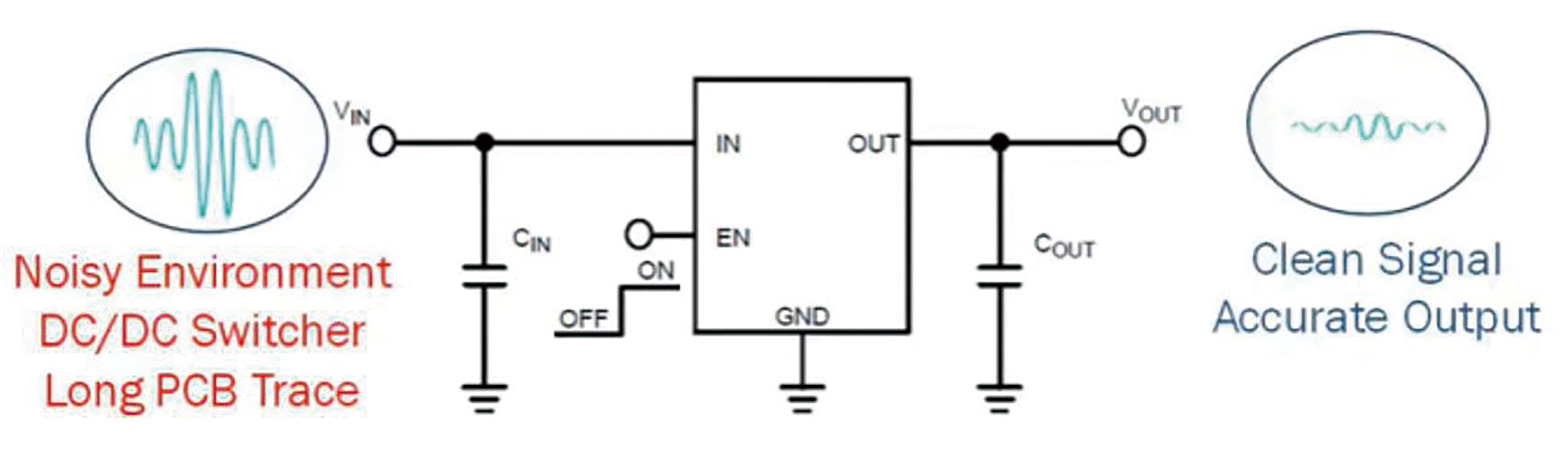

電源抑制比衡量LDO抑制紋波

電源抑制比(PSRR)提供了一個方法來衡量LDO抑制紋波的能力,也提供方法阻斷僅在LDO輸入端由電源軌產生的雜訊。PSRR越高,可阻斷越多的電源雜訊或波紋。這些紋波可能來自50/60Hz紋波的輸入電源,DC-DC的開關頻率,或由於不同電路共用輸入電源而產生的紋波(圖5)。

圖5 從LDO的輸入到輸出的雜訊示例

圖5 從LDO的輸入到輸出的雜訊示例

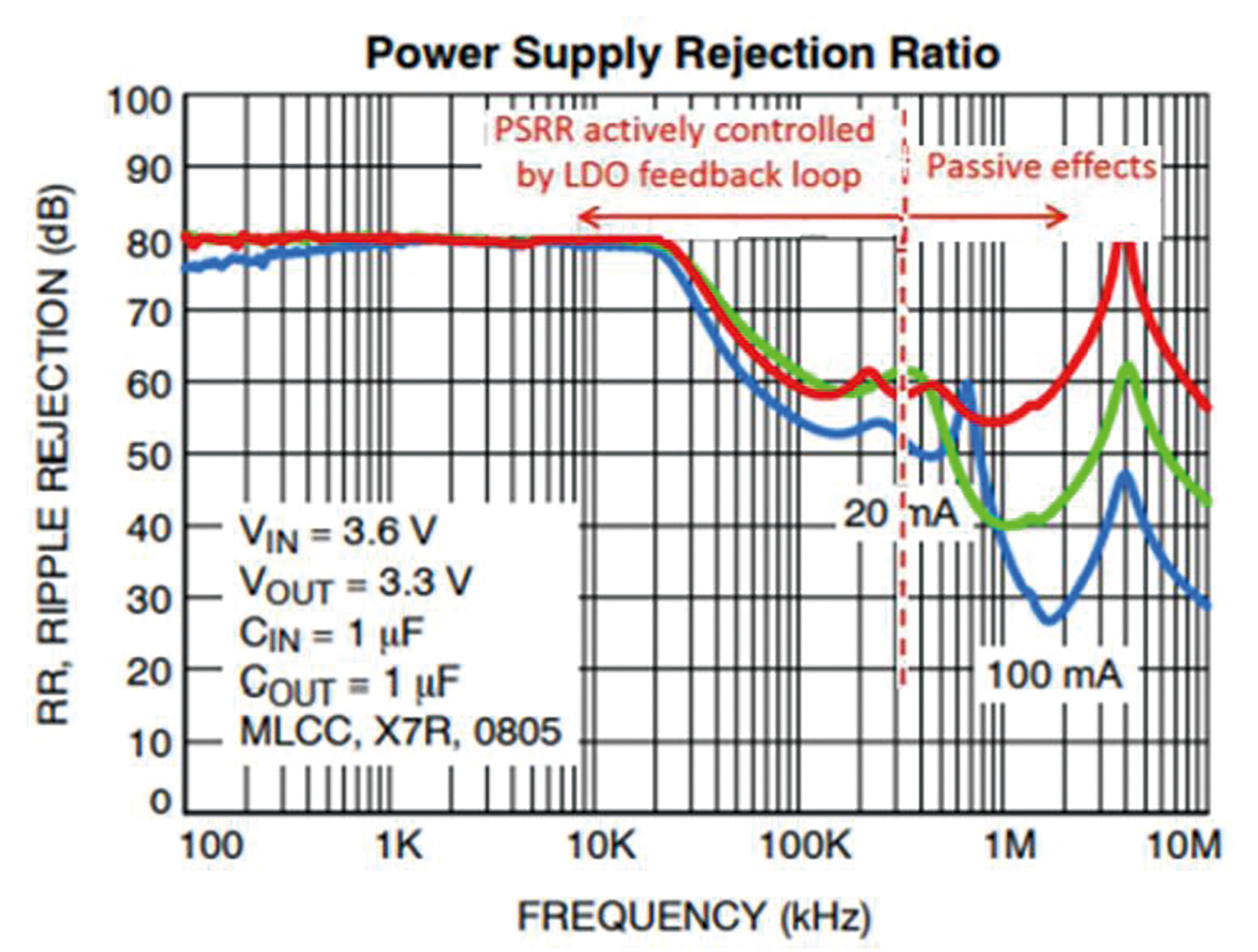

LDO的反饋迴路通常控制著頻率在100kHz以下的系統PSRR,所以要確保選擇一個合適的LDO。對於高於100kHz的頻率,適當選擇的被動元件和PCB布局/位置將控制PSRR(圖6)。

圖6 典型LDO的PSRR行為與頻率的關係

圖6 典型LDO的PSRR行為與頻率的關係

在設計PCB時,應注意電流環路要緊密,以減少寄生電感和電源軌與相機軌之間的紋波。在VIN和VOUT之間使用一個乾淨的偏置或更高的餘量,也可以增加PSRR性能能力。低的PSRR性能或類比軌上的任何雜訊會導致電源軌上的雜訊透過高增益源跟隨器放大器電路進入輸出訊號路徑,導致捕獲的圖像中出現不想要的水平波紋(圖7)。

圖7 類比軌上的雜訊示例

圖7 類比軌上的雜訊示例

普通LDO在高頻下的PSRR較低,這對於普通相機來說應該足夠了,但是對於50~200MP範圍內的高解析度和高幀率圖像感測器,肯定需要特定系列的LDO,在較低頻率範圍達10kHz以下的PSRR大於90dB,在1~3MHz頻率範圍內的PSRR大於45dB,以減少幀和行速率轉換期間的紋波。

感測器幀和行速率與電源負荷之間關係

值得注意的是,幀率(30~120fps)和行速率(22~44kHz)都會給圖像感測器帶來動態負荷,在2.8V的模擬軌上產生下沖和過沖。

在每一個新的幀或新的行轉換過程中,電流的吸取就像一個階梯負載。例如,在一幀或一行的讀取過程中,或者在每一幀或一行的讀取之間,電源配置(LDO)需要在每個幀和行轉換期間處理幾百毫安培的負載變化,但在其輸出電壓軌上無任何大幅度的波動。

對於相機去耦,需要體電容器在行和幀頻率附近具有最低阻抗,以獲得最佳系統性能。

LDO輸出雜訊

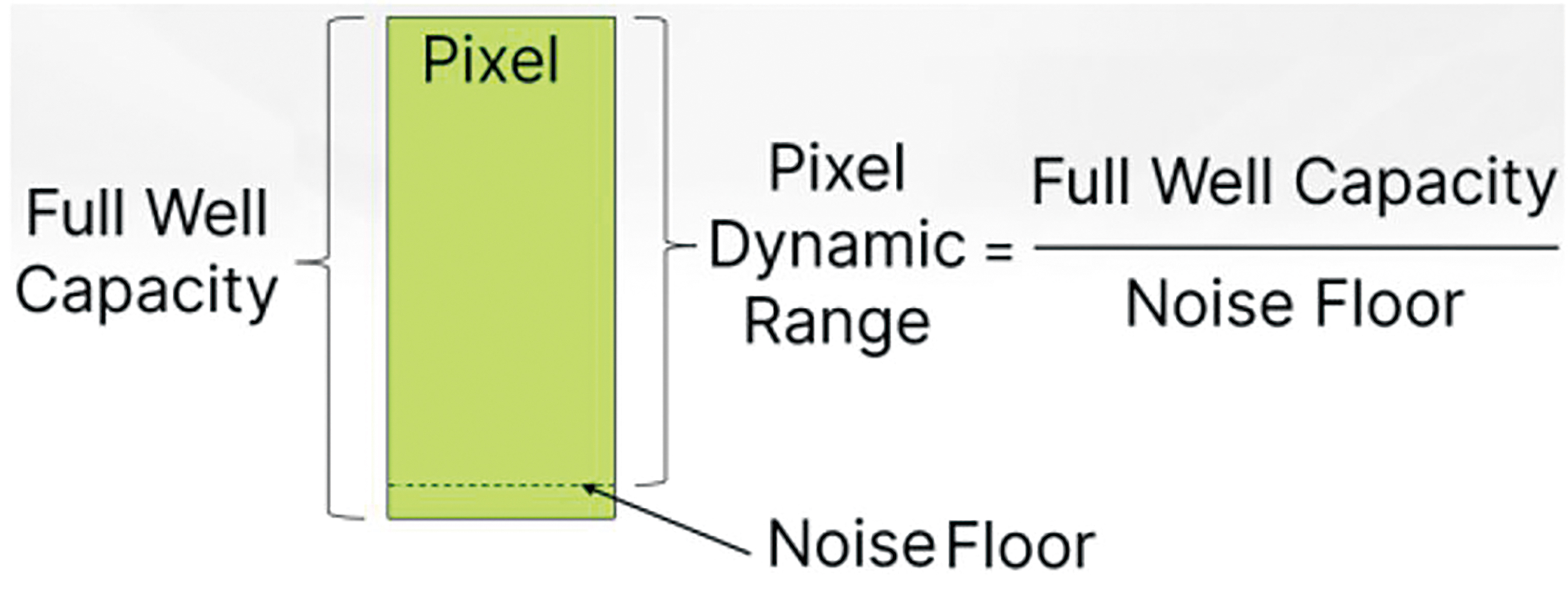

根據圖像感測器的設計,每個畫素都有一個電荷飽和度或滿井容量,亦即一個畫素在飽和前所能容納的電荷量(以電子為單位)。對於任何圖像感測器,動態範圍(dB)定義為圖像中可同時捕獲的最亮和最暗的部分(圖8)。

圖8 圖元容量和本底雜訊示例

圖8 圖元容量和本底雜訊示例

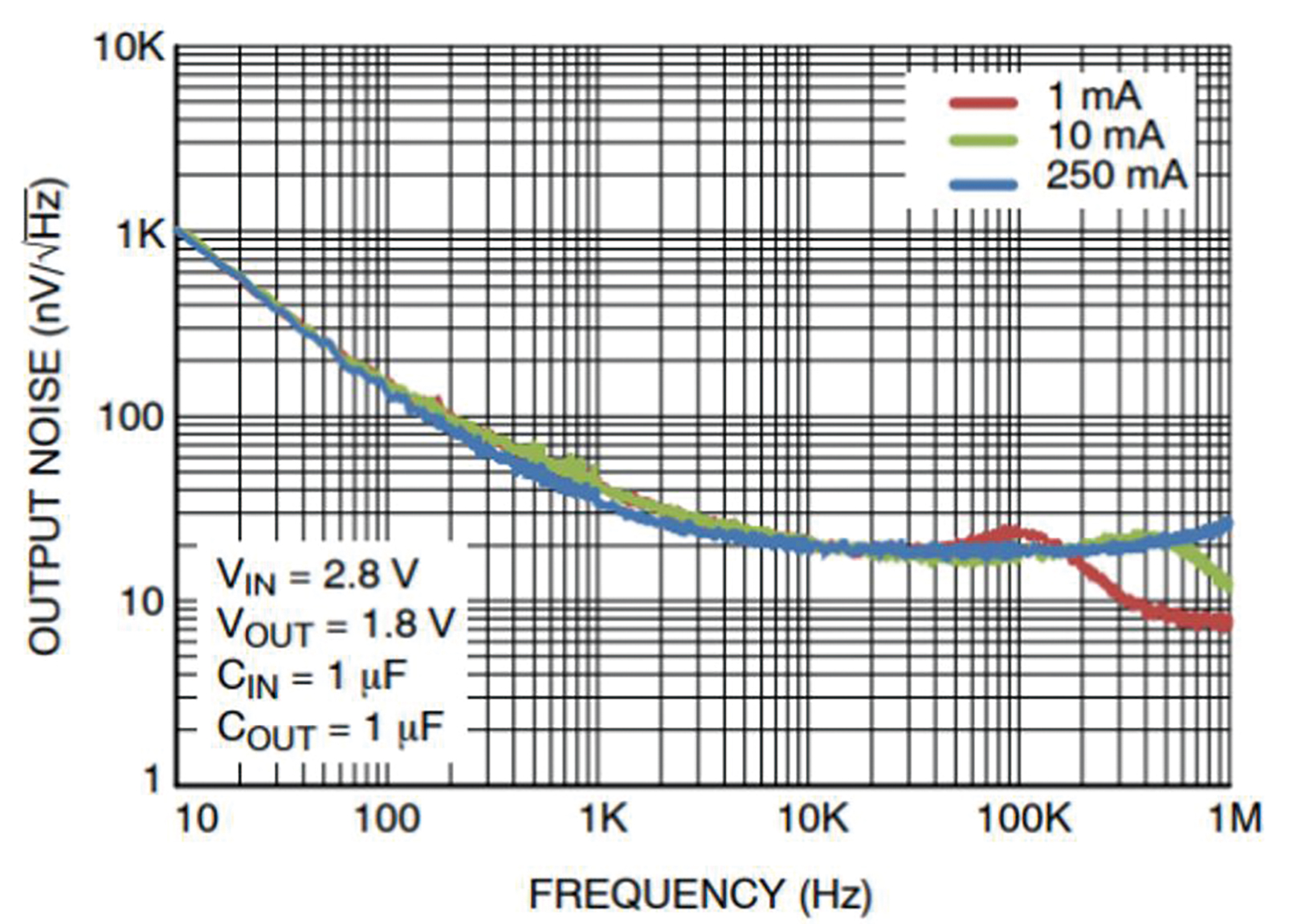

在任何LDO的輸出端,10Hz~1MHz之間的頻譜雜訊密度越低,就越能發揮重要作用,轉移到CMOS圖像感測器中的雜訊就越少,使給定畫素的動態範圍更高(圖9)。

圖9 典型的LDO輸出雜訊密度

圖9 典型的LDO輸出雜訊密度

找到CMOS圖像感測器的訊號噪音比(SNR)資訊並設計系統至關重要,可使整體紋波和雜訊至少比感測器的雜訊臨界值低40dB。

LDO實現高解析度攝影機

為不同規格的圖像感測器設計LDO電源配置時,有不同的問題要解決,比如4百萬畫素不等同於40百萬畫素,30幀不同於120幀的幀率,或高動態範圍不同於低動態範圍等。如今可透過網際網路服務供應商(ISP)提供的最大資料速率能力,和所用的C/D-PHY MIPI通道數量實現高解析度相機的最大允許幀率。考慮到運算出的最高幀率頻率所需的最高PSRR和一個圖像感測器所需的RMS雜訊密度,與已知的SNR,由此可以設計一個優化的電源系統,以滿足當今高解析度和高幀率CMOS圖像感測器的要求。

使用在較高頻率下具有高PSRR、低RMS雜訊的LDO方案,以及提供的垂直和水平頻率下具有特定阻抗的合適的無源元件,可改善CMOS圖像感測器的整體雜訊性能、減少電源波紋,進而使拍攝的圖像減少不想要的水平波紋。

(本文作者為安森美首席現場應用工程師)