低雜訊放大器(Low Noise Amplifier, LNA)設計中最大的障礙為雜訊Γopt與共軛S11匹配點的不重合。基於這個原因,LNA設計過程無可避免地須對雜訊指數的輸入匹配進行取捨。不幸的是,由於天線匹配要求,例如LNA要在-18dB回返耗損的帶通濾波器後,達到14dB的天線不匹配,輸入返回損耗(Input Return Loss, IRL)必須優於-23dB,因此這樣的取捨並不適合行動通訊基礎建設應用。

雖然隔離器可用來解決雜訊匹配放大器中的高反射率,但卻有成本高且重量重的缺點,比隔離器更便宜並且更輕的產品是由貝爾實驗室於60年代所開發出的平衡放大器拓撲結構,它將由一對放大器反射的能量送到正交3dB耦合器,或稱為90

o或混合耦合器進行自我消除。由於連接埠的匹配並不會受到組成放大器實際反射率的影響,因此可達到良好的匹配。

此外,隔離器的平衡組態也擁有比單端結構更好的可靠度、線性度及頻寬,而最令人訝異的是,它本身具有自我穩定功能,也就是即使由兩個可能不穩定放大器構成,還是可確保無論是帶內或帶外的完美穩定性。在缺點方面,平衡式LNA須比單端設計多一倍的電流及零組件,而用來做為訊號分離與組合的正交耦合器,也會增加成本並占用更多的電路板空間,特別是在分散式設計上,同時插入耗損也會影響射頻性能。若使用商用插入式耦合器,則射頻效能基本上會與採用元件的尺寸與價格成正比。受限的行動通訊塔頂空間,例如塔頂放大器(Tower Mounted Amplifier, TMA)會因平衡式LNA是單端設計的兩倍重量與尺寸而傾向於不採用。

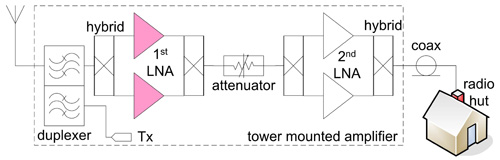

相關文件的研究帶來解決平衡式LNA尺寸問題的兩個方法,分別為縮小耦合器及更高的電路整合度。在此同時,塔頂放大器對於最先進靈敏度與線性度的需求也對微型化帶來阻礙。圖1為平衡式LNA設計架構。

|

| 圖1 平衡式LNA為行動通訊塔頂放大器的低不匹配與低雜訊帶來解答。 |

為改善先前900MHz平衡式LNA設計的尺寸與使用零組件數量,本文以微型化多層耦合器及整合雙放大器、偏壓與關斷功能的毫米波積體電路(MMIC)為基礎進行設計。為強化設計的可用性,MMIC在追平甚至超越先前技術所達成最佳雜訊與線性效能的基礎上,期望能大幅度縮小尺寸。

採用高整合MMIC為LNA設計基礎

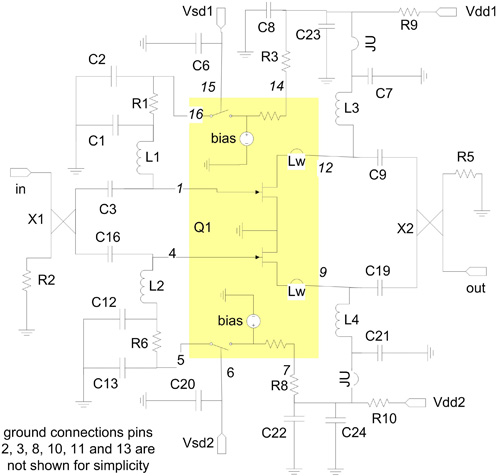

本文範例設計一款整合雙放大器、靜電放電(ESD)保護、主動式偏壓及關斷功能的MMIC產品(圖2),在同一顆晶片上結合偏壓電路與放大器可在閘極臨界電壓與溫度變化情況下穩定工作電流的。

|

| 圖2 MMIC整合雙放大器、主動偏壓以及關斷功能(灰色部分),因此在晶片外只須搭配阻抗匹配與混合耦合器。 |

由於具備最佳的成本與效能平衡,因此晶片使用6吋晶圓製程上的0.25微米(μm)增強模式偽相高電子遷移率電晶體(E-pHEMT)。首先,製程使用單端LNA得到900MHz時0.3dB的雜訊指數(NF),因此在調整耦合器耗損後可達到平衡模式下0.5dB的NF,接著製程大於30GHz相對較高的頻率fT,以及約615mS/mm的最高跨導可降低達到+17.6dB增益的電路級到單一,最後,這個製程的線性度直到Vds低於2伏特(V)時,才會明顯下滑,因此非常適合低電壓運作應用。

主動式偏壓電路透過外部電阻R3與R8連接到電源Vdd1與Vdd2,透過這些電阻,工程師可自由控制閘極偏壓。雖然每個E-pHEMT的標稱吸入電流Idd在4.8V Vdd時為60毫安培(mA),但可在這些電阻的可允許範圍於48~72mA間變化。電感L1與L16以及電阻R1與R6形成閘極偏壓電路,即使晶片內的螺旋電感可執行這個功能,但由於較低耗損及較小晶片的成本較低,因此這個設計傾向使用外部電感,使晶片可應用在不同的頻率上。由於雜訊指數在這個應用中非常重要,因此本文範例特別使用貼片繞線式電感而不使用積層式電感。除偏壓插入外,先前提到的電感加上串列電容C3與C16同時也形成可濾除非所要低頻增益的高通電路,連接汲極到封裝接腳的長接合線LW也可以做為預匹配之用。

關斷功能方塊包含與主動偏壓串接的電晶體開關,關斷動作由加上Vsd1/2的2V高邏輯電位使開關斷開,接著由Vsd1/2500mV的低邏輯電位啟動放大器,若省略0.1微法(μF)的較大去耦合電容C6/8/20/22/23/24,那麼由正常狀態到關斷的時間低於50奈秒(ns),不過,由於這些電容能有助低頻的穩定度並且可對電源電壓變動形成阻尼效應,因此本文建議使用。

|

| 圖3 將內部MMIC間的S11差異以及耦合器隔離縮小,可讓設計達到量產時IRL-21dB的規格要求,其中最差情況為五百個取樣下-21.5dB。 |

平衡式放大器的訊號分離與組合使用已商用的多層耦合器X1與X2,以節省設計工作與電路板空間。在輸入端使用耗損較低的6.4毫米(mm)×5.1毫米較大耦合器,在輸出端則使用2.01毫米×1.3毫米的較小耦合器節省空間與成本。為確保在量產時達成IRL-21dB的要求,這些關鍵參數透過Monte Cario分析找出(圖3)。接著進行兩個控制項,分別為將放大器的輸入匹配到|S11a-S11b|<0.025,且輸入耦合器的隔離必須>23dB,其中第一個控制項可由使用相鄰的晶片達成,第二個控制項則須指定高隔離輸入耦合器,不過輸出耦合器則並非關鍵。

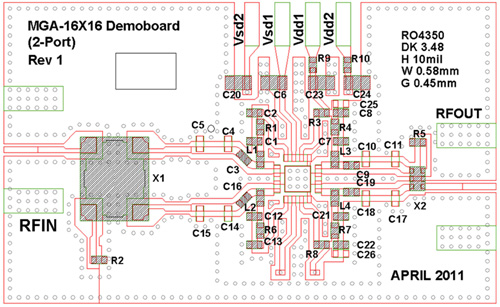

PCB採用成本中等材料

印刷電路板則採用中等成本的Rogers RO4350材料(圖4),走線條寬度盡可能針對50歐姆(Ω)特性阻抗設計,不過,輸入耦合器貼裝接點旁的走線寬度則須依照製造商的建議縮小,以補償接點的寄生電容,對於10mil(0.254毫米)厚的印刷電路板,加入FR4以便將堆疊厚度提高到1.6毫米,輸入與輸出走線使用邊緣SMA連接器轉換成同軸電纜,所有的結果都以同軸端點做為參考。

|

| 圖4 印刷電路板的布局與零件安排圖,元件位置以灰色方塊代表。 |

為在安捷倫(Agilent)ADS2009上模擬,本文範例將電路模型分離為二階結構,包含代表MMIC訊號分離/組合以及阻抗匹配功能的方塊,兩個放大器由相同的二連接埠S參數代表。S參數由相似材料(10mil RO3450)的測試安排取得,接著加入穿透、反射、線段(TRL)校正將參考平面移至封裝邊緣。使用相同的測試安排,元件的雜訊與線性參數可使用自動訊號源與負載調諧器取得,由於容易受到機械調諧器的組合耗損及所需的連接適配器遮蔽,因此約0.2dB的最低雜訊指數特別難以取得,電感與混合耦合器使用製造商的資料建構模型,其他的被動式零組件則使用包含低階寄生的等效電路代表。

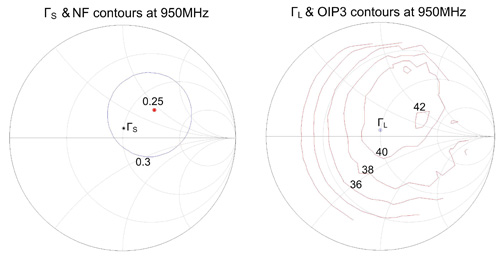

為驗證所設計的輸入與輸出匹配電路,模型化的訊號源(ΓS)與負載(ΓL)阻抗與先前所測得的訊號源與負載比較,其中ΓS與ΓL為使用安捷倫量測儀器的S參數探針取得。使用MMIC容易達到良好的雜訊效能,原因是0.3dB的固定NF圈較大,甚至包含圖形的中心(圖5)。基於這個原因,L1-C3與L2-C16組成的輸入電路在設計上主要以偏壓功能為目的而非阻抗或雜訊匹配,輸入LC電路中缺少阻抗轉換代表頻寬不會受到電路負載Q值的限制,同時插入耗損也較不受零組件Q值的影響。圖5中的ΓS偏移為非故意,主要由零組件的總和寄生效應引起,ΓS的雜訊指數為0.28dB,雖然針對雜訊匹配最佳化的Γopt可大幅度改善雜訊指數約0.03dB,但並非必須。

|

| 圖5 由於史密斯圖的中心點由0.3dB的固定雜訊指數圈環繞(左),輸出端則由40dBm固定IP3圈環繞(右),因此可以在沒有阻抗匹配的情況下達成良好的雜訊與線性效能。 |

在最佳輸出匹配時,MMIC擁有超過42dBm的第三階輸出截點(OIP3),由於偏離圖形中心,由42dB固定線性圈所涵蓋的區域需要某些阻抗轉換達成,請參考圖5右方,位於40dBm的第二個圈已包含圖形的中心,由於40dBm的OIP3對於這個應用已經足夠,因此在設計輸出電路時並未進行阻抗轉換,亦即ΓL=50Ω,不過由於零組件的寄生效應,ΓL會稍微偏離中心點。

與先前的設計比較,印刷電路板可縮小40~110%,零件數則高於內建匹配功能的超薄板上模塑晶片(MCOB)設計,但其所採用的外部匹配方式可帶來較低雜訊指數,同時單裸晶製作成本也較低。此外,MMIC單電源電壓要求也比雙電源電壓的穩壓與濾波節省許多零件成本,且為整合關斷功能的雙放大器MMIC元件。

降低LNA雜訊指數變化

雖然MMIC設計進行大幅度的微型化,但增益與雜訊效能並未受到影響。在900MHz時,實驗所得的增益與雜訊指數分別為0.5dB與18dB,其中實驗得到的雜訊指數可匹敵使用較昂貴製程或封裝的設計,雜訊指數結果也相等於使用較大55%耦合器的最新設計。

專為MMIC設計所發展的電路模型擁有良好的預測值,增益與雜訊指數的最大誤差分別為0.2dB與0.1dB。假設輸入耦合器與匹配電路為理想狀態,那麼平衡式LNA就擁有與組成放大器相近的雜訊指數,由於元件級雜訊指數約為0.3dB,因此可推測加入同軸連接器、混合耦合器及輸入匹配的整合耗損還可達到0.2dB的雜訊指數,在600M~1,050MHz範圍內,雜訊指數的變化低於最小值0.1dB,因此平衡式LNA可用頻寬足夠應付現有及未來的全球3G與4G網路頻帶,超過這個頻率範圍的雜訊指數會因為輸入耦合器的特性而大幅上升。

|

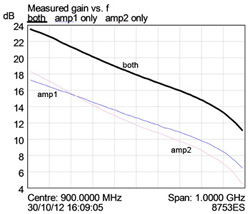

| 圖6 兩個放大器都正常工作及僅其中一個放大器工作時增益相對於頻率的關係。 |

若其中一邊完全失效,平衡式LNA的中間頻帶增益依然會維持在可用的約12dB範圍。要模擬其中一個放大器失效,連接到每個放大器的電源Vdd1與Vdd2會交替斷開,當同一時間只有一個放大器供電時,中間頻帶增益會在11.8~12.7dB中變化(圖6),這個半運作狀態下的增益依理論會由6dB下滑約十分之幾,由於當其中一個放大器完全失效時增益並不會完全損失,因此相較於單端放大器,平衡式放大器更加可靠,這對行動通訊應用是非常重要的優勢。

|

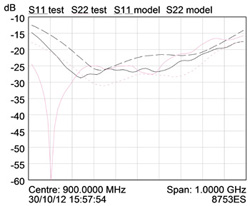

| 圖7 輸入與輸出返回損耗相對於頻率關係的模型與實際測量值。 |

實驗結果,本文提出的平衡式LNA超過塔頂放大器要求的-21dB輸入不匹配,此外,也可在寬廣的頻寬下維持良好的匹配,也就是IRL-20dB時頻寬等於中央頻率fc的83%(圖7)。實驗IRL在輸入耦合器中央頻率附近時最佳,同樣地,輸出耦合器也決定ORL響應,這個模型在大部分的導通頻帶內都能夠符合實驗的結果。

即使組成放大器不穩定,平衡式LNA依舊能夠維持穩定,不管是模型或測量所得的穩定係數mu都能夠在50M~20GHz間超過一單位,因此平衡拓撲的自我穩定功能可得到驗證,原因是單獨放大器在評估範圍內的數個不同頻率可能不穩定(mu<1),計算所得的穩定係數與實驗結果擁有相同的趨勢,但尖峰並無法完全涵蓋,這個誤差可能由被動零組件模型的過度簡化所引起。

|

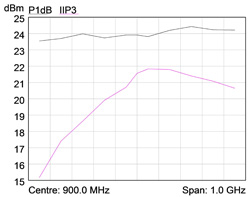

| 圖8 約24dBm的P1dB以及21.6dBm的IIP3為900MHz平衡式LNA中的最佳表現。 |

本文設計範例的增益壓縮與線性效能為同類最佳,其中IIP3高於最接近競爭者5.6dB。1dB增益壓縮點P1dB在中間頻帶時約為24dBm,同時在整個頻率範圍也維持穩定,於1GHz範圍內變化低於1dB(圖8),使用-20dBm以1MHz間隔分離的單音訊號做為測試源,第三階輸入截點IIP3在中間頻帶測量結果約為21.6dBm,不過不似平坦的P1dB響應,IIP3在接近耦合器導通頻帶的近中心點會有一個明顯的21.9dBm尖峰。

以輸出點為參考,第三階截點OIP3在中間頻帶約為39.6dBm,依OPI3相對於直流功率的線性評價值(Figure of Merit)為9.12/0.58,約等於15.7,1dB增益壓縮點以及輸入第三階截點IIP3的較高值代表對於遮蔽與偽混波有較高的忍受力,因此更為適合通常與其他服務相鄰的塔頂放大器應用。

增添LNA放大器關斷狀態匹配

|

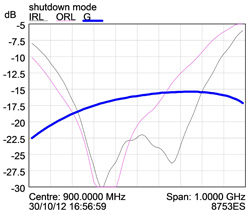

| 圖9 關斷狀態下RL-20dB的良好匹配可消除外部旁路需求。 |

啟動MMIC的關斷功能可將放大器轉換成為無反射衰減器,能用來避免後方電路級發生過載,通過關斷放大器的訊號會在中間頻帶衰減約16dB,同時IRL與ORL的測量值優於-20dB(圖9)。由於反射的能量會在耦合器中自行消除,因此可在關斷狀態下保持良好的匹配,相反的,沒有通電的單端放大器擁有高反射性,因此必須加旁路以避免額外的天線與濾波器失調。

900MHz平衡式LNA設計所占用的尺寸及使用零組件數可透過高整合MMIC降低,塔頂放大器的超低不匹配要求可透過控制放大器S11差異及耦合器的隔離達成。除積極的微型化,MMIC包含更小輸入耦合器可取得最佳的雜訊指數與線性度,關斷模式的良好匹配也能夠節省LNA旁路的需求,可謂MMIC新設計可帶來體積更小且效能更佳的塔頂平衡式LNA。

(本文作者任職於安華高)