感測器中樞可望大幅降低感測子系統的功耗。隨著MEMS感測器中樞參考設計平台,以及先進感測器融合演算法相繼出爐,搭載多軸MEMS感測器的行動裝置將能克服以往採應用處理器運算感測資料,而導致系統耗電量遽增的問題。

近年微機電系統(MEMS)慣性感測器需求出現爆炸式增長,解析這些感測器資料的處理器需求也大幅增加。

然而,在何處進行感測器資料處理則是一個複雜的問題。系統設計人員須確定幾個設計因素的優先次序,包括融合輸出的精確度、功率、區域/空間考量、是否易於整合,以及成本和供應鏈靈活性。

克服處理器耗電問題 感測器中樞快步崛起

|

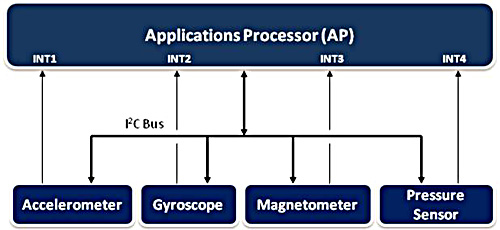

| 圖1 最小分母感測器融合架構圖 |

在白牌裝置市場中,優先考慮的往往是成本和/或供應鏈靈活性。在這種情況下,原始設備廠商經常會依據「最小分母」原則選擇感測器和微控制器(MCU)(圖1),但在手機和平板裝置中,為在應用處理器上直接進行感測器融合(Sensor Fusion),可能會完全忽略MCU。採用單獨感測器(加速度計、陀螺儀、磁力計等)可能是手機廠眾多選項中的一個,為保證最低成本或不間斷的供應鏈,一個廠商的感測器也可能會被另一個取代。

通常,使用者不得不接受更高的功耗和有限功能,並為此支付費用,主因係設計人員直接以應用處理器運算感測器資料,在工作時將消耗大量電力,且切換到低功耗狀態或從低功耗狀態切換回正常狀態,都會花費大量時間。特別在執行各個感測器的單獨中斷指令時,問題更加嚴重。除此之外,應用處理器上運行的作業系統通常不支援即時處理模式,因而限制感測器資料應用。

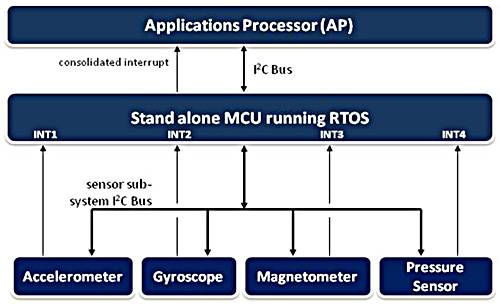

為克服此一桎梏,業界已興起利用感測器中樞(Sensor Hub)搭配感測器融合軟體,從而實現即時處理功能的解決方案,可支援最簡單的感測系統整合應用(圖2)。

|

| 圖2 基本感測器中樞架構圖 |

選擇系統MCU時,開發人員應考量MCU在低功耗狀態下的快速切換和低中斷延遲兩大因素。由於感測器融合軟體在MCU上運行,因此應用處理器可按需要採用資料。如此一來,不僅可節省應用處理器的大量功耗,且省下來的電力對獨立MCU運作將綽綽有餘。不過,這難免會占用更多的印刷電路板(PCB)的空間,且系統成本將隨著MCU和周邊被動元件的成本而增加。

參考設計平台減輕演算法開發負擔

對於想設計包含感測器融合功能的系統設計人員來說,開發圖2所示的系統將是一個艱鉅任務,主因係融合演算法非常複雜,須耗費大量研發時程,如果感測器製造商提供在MCU上運行的融合軟體,透過整合角度來看,系統設計將變得非常簡單,而若感測器業者進一步提供感測子系統原理圖和布局資訊,則會更簡單。

隨著MEMS感測器和晶片封裝技術不斷發展,感測器製造商現在能夠組合圖1、2所示的一些感測器類型。如果成本或電路板空間是最重要的因素,許多感測器採用普通封裝即可;如果精確度是最重要的因素,設計人員可能希望將磁力計與加速度計、陀螺儀分開,單獨進行封裝。通常PCB邊緣的磁干擾最小,而加速度感測器和陀螺儀則須在系統中心時性能最佳;同樣的,壓力感測器的最佳放置地點是可與外界通風的位置(可能在麥克風附近)。

圖2所示系統可進一步在兩個不同方向發展,以功率角度看,最有效的方法可能是在應用處理器中內建一個獨立的MCU,並配備單獨的電源和時鐘管理;但目前廠商通常不提供這種方案,即使(如果)應用處理器製造商提供這種方案,系統業者仍然會有誰為融合子系統提供軟體的疑問。

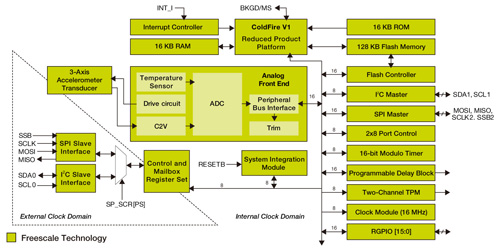

另一種方法是整合MCU與感測器,稱為智慧感測器中樞,包括飛思卡爾(Freescale)、Bosch Seneortec和意法半導體(ST)皆在近期推出相關解決方案。當選擇智慧感測器中樞時,設計人員往往想知道廠商只是將MCU連接到現有感測器上,還是針對感測器融合優化整合子系統,一般來說就是優化功率,如圖3的感測器子系統。

感測器中樞全盤考量系統性能

在記憶體方面,智慧感測器中樞通常從快閃記憶體運行。就晶片面積和成本而言,快閃記憶體和隨機存取記憶體(RAM)都是昂貴的資源,因此工程師須考量是否有足夠的記憶體來完成這項工作?另外,記憶體的成本是否超出預算,以及RAM/快閃記憶體比例適合這個應用的開發嗎?通常融合演算法需要的RAM容量比基礎控制應用還要多,採用1KB的RAM可能較適合融合應用。

快閃記憶體往往是系統中速度最慢的記憶體。快閃記憶體存取是否影響系統性能?或工程師是否有某類Flash Cache或可滿足未來應用所需的暫存器?另外,當感測器中樞處於低功耗狀態時,負責與主系統通訊的從埠介面是否能夠正常運行、功耗要達到多低的水準等問題都須納入考量,而理想情況是能夠關閉中樞上的所有時脈,這意味著序列埠需外部計時。目前大部分標準MCU將序列埠時脈看作資料,以兩倍或四倍的資料速率採樣,雖會消耗功率,但資料穿過中樞內的時脈保證不出現問題。

時脈頻率設計部分,系統從慢時脈速率切換到快時脈速率或切換回慢速率的速度有多快是開發關鍵,MCU經常使用鎖相迴路(PLL)功能執行慢時脈頻率乘法運算,達到可用的範圍。鎖相迴路運行良好,但會消耗大量功率,也須花一些時間來鎖定最終頻率,如圖3使用一個根據需要在兩個頻率之間切換的振盪器。

|

| 圖3 新一代智慧感測器中樞電路布局 |

內部時脈產生器經常會隨著溫度產生1~3%的變化,如果設計人員在乎此一影響,可考慮採用慢外部時基,將其輸入到晶片上的計時器,根據內部時脈週期測量外部時脈,動態調整幀速率。

至於感測器中樞的採樣率方面,如圖3所示系統包含一個定制的幀間隔計數器,可確保恆定幀速率,與高頻/低頻操作模式的時長無關,如果工程師採用的元件有晶體振盪器,就須考量頻率(32kHz)是否適度而不會消耗過多功率。

另外還要確保類比數位轉換器(ADC)的精確度,因轉換結果的解析度有效位元(ENOB),以及轉換精度與轉換速度之間是否平衡。此外,智慧感測器中樞是否可識別主要運動事件?引擎的通用性如何?演算法是否能夠通用,還是僅限採用特定的感測器融合資料庫?而感測器中樞管理其他裝置有沒有限制?是否有足夠頻寬、RAM,以及用於計算的MIPS,都是設計時要注意的重要項目。

最終則是開放性的考量,中樞是否有固定功能,或能定製其上的代碼,且是否有實現這些目的所需的資料庫和開發工具,如果採用Android作業系統,是否須提供驅動程式和定製硬體抽象層(HAL);而採用Windows 8作業系統,中樞製造商是否提供HID/I2C或HID/USB介面等諸多要素。

高整合度感測器中樞加速系統優化

總體而言,感測器中樞設計可從兩方面著手,首先是減少依靠軟體功能來實現融合的感測器數量,其次則是採用感測器製造商打造的高整合感測器子系統和參考設計,實現系統整合和客製化。

(本文作者任職於飛思卡爾半導體)