由於高畫質視訊應用需要多顆元件才能完成所要求的視訊工作,因此如何將這些工作有效區分給多顆高性價比的數位訊號處理器或FPGA,成為近期業界關注的話題。

當視訊已變得無所不在時,消費者多半希望所擁有的產品都能提供支援各式不同畫質標準的視訊功能。儘管今日許多如行動電話和可攜式音訊/視訊播放器等產品,只需一顆數位訊號處理器(DSP)就能應付所有視訊處理作業,並滿足嚴苛的成本要求;但對高畫質電視或視訊會議等高品質應用而言,目前市場還未出現任何單一元件就能滿足其處理需求。

相較之下,多顆DSP或DSP與FPGA共同組成的多晶片系統,則能解決這個難題,並在不過度複雜或合理成本的情形下,滿足高畫質視訊的處理需求。這也讓設計人員在分配工作至不同的處理器時,能夠謹慎考慮元件的可用資源及分析相關演算法,作出最明智的決定。

編解碼器有助高畫質實現

H.264/MPEG-4/AVC是目前業界熱門的視訊編碼解碼器,此視訊編碼解碼器只需約一半的位元數就能產生等同MPEG-2的相同畫質,若使用同樣位元數,則能產生比MPEG-2更高畫質的影像,只不過要達到這些優點,其所需的效能也遠超過MPEG-2編碼解碼器。

另外,由於H.264編碼解碼器標準並未具體規範其運算需求,而是由編解碼器開發商根據許多因素決定,包括解析度與圖框率、輸出位元率、H.264編碼器類別和其他具體要求,如搜尋範圍、搜尋演算法、搜尋分割(Search Partition)、微調和參考圖框數目等,這些參數都會影響視訊畫質。換言之,系統的運算需求會受到視訊畫質需求的影響,就算使用同樣編碼解碼器的系統也可能出現很大差異。

編碼方式極為多元

視訊鏈最常執行的處理作業包括編碼、轉碼、碼率轉換和解碼。因此,就算尚未確定欲使用的DSP,仍有可能找出作業分割方式,以便充分利用多顆元件的效能。

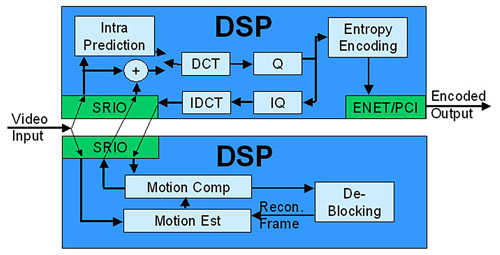

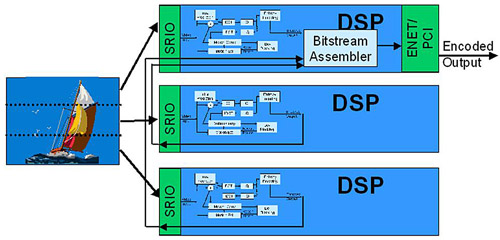

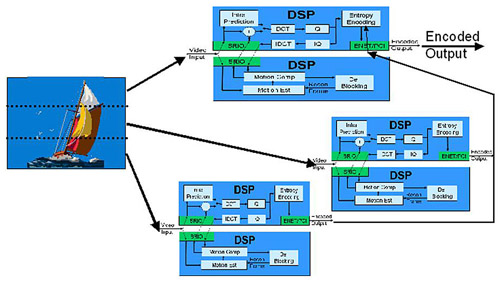

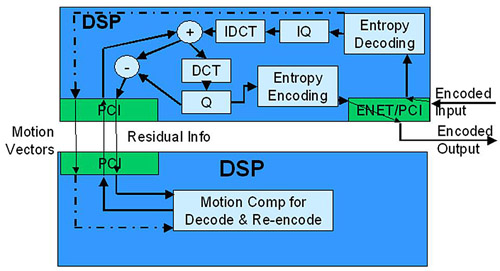

編碼是最需要繁重運算的作業,系統會利用編碼作業將未壓縮的原始數位視訊轉換為壓縮位元流,讓影像畫面更容易透過有限頻寬的通道傳送。不同應用的編碼器如圖1、2、3。從這三種主要的視訊編碼器分割方式來看,根據功能分割的編碼器中,FPGA可取代下層方塊的角色。這些範例元件會利用Serial Rapid IO(SRIO)進行處理器間通訊。

|

|

| |

功能分割是很直接的編碼作業分割方式,其可將編碼器功能分散至多顆元件執行。圖1是採用兩顆DSP的架構,上方的元件負責執行圖框內預測,僅使用畫素區塊內所含的資訊來預測其他畫素、熵編碼(Entropy Encoding)、變換和量化。下方的DSP則負責利用周圍區塊或其他圖框的資訊來處理區塊間的運算;另外,下方的DSP還負責執行迴路內塊狀畫面消除功能(In-loop Deblocking),以便消除畫面重建後出現的塊狀現象。這種功能分割式編碼器會同時處理整個畫面,故可提供較高的視訊畫質,雜訊也較少。

然而,這種透過功能分割提供高畫質的作法也有缺點,其中之一是處理步驟之間的相互依賴性太高,而且必須在不同的功能方塊間移動大量資料。因此,相關元件必須擁有極強大的處理器間通訊能力(IPC),而要為編碼器增加更多的處理器也很困難。舉例而言,設計人員雖可將塊狀畫面消除功能移到其他元件,並讓原來的元件專注執行移動估測功能,但卻會增加I/O需求。這種資料流程會影響實際所能應用的DSP數目,使得這種編碼功能分割方式的擴充性受到很大限制。 |

|

|

| |

另一種減少處理器間通訊需求的作法是將所有處理功能放到一個DSP,但將畫面分割成多個水平方向的片段,進而分開處理這些畫面(圖2)。相較於根據功能進行分割的作法,這種將畫面分為多個片段的方式能減少處理器間通訊,也能較輕易的於系統內擴充更多處理器。這種作法的缺點在於若將畫面分割成太多片段,畫質可能就會受到影響,因為畫面分割得越多,其間的邊界可能也越明顯,熵控制也會變得很難管理。而將畫面分割成六個以上的片段,對高畫質視訊而言是可接受的。 |

|

|

| |

第三種編碼分割方式則把前述兩種作法的優點結合在一起。此類的編碼分割方式會先將畫面分成數目較少、但面積較大的片段,然後如功能分割方式般將每個片段交給兩顆DSP同時處理。這種分割方式的擴充性良好,可隨時增加多顆DSP以處理高畫質視訊。由於熵編碼所能使用的區域較大,邊界數目也較少,因此這種作法對畫質的影響比單純將畫面分為多個片段少。 |

|

| 圖1 根據功能分割的編碼器 |

|

| 圖2 根據畫面片段分割的編碼器 |

|

| 圖3 結合上述兩種做法的分割編碼器 |

設計人員可利用FPGA執行移動估測、移動補償和塊狀畫面消除等步驟,以提升系統效能。這種可客製化的加速方式提供更高效能和良好的擴充性及彈性。FPGA擁有支援平行作業的特性,因此適合用來執行這些演算法;換言之,採用功能分割或綜合分割方式的系統最適合使用DSP與FPGA的架構。若是通用DSP未能提供視訊最佳化的I/O連接埠,設計人員也可在必要時利用FPGA實作視訊I/O功能。

各式標準轉碼特性各異

系統有時還須在視訊串流編碼後執行轉碼,其會將壓縮後的位元串流轉換為另一種視訊壓縮標準,以便使用者在不同的視訊播放裝置上觀看這些內容。轉碼技術是視訊娛樂市場持續進步的關鍵,消費者希望即便是高畫質內容,也能方便傳送且可在各種裝置上播放。應用系統通常需要轉碼功能,才能應付不同的可攜式視訊裝置所提供的各種功能和頻寬。

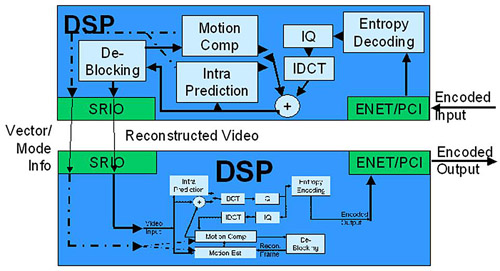

圖4為另一種可行的轉碼作業分割方式,其利用上方的DSP擔任解碼器,負責接受編碼輸入,再將重建後的視訊和殘值資訊傳送至下方的DSP重新執行編碼作業。由於編碼器可利用這些除了原始視訊資料外的額外資訊先進行作業,因此可減少高達兩成的正常運算負擔。然而,這種分割方式需要高效能的處理器間通訊,且圖4下方的方塊會執行功能分割式編碼器的所有工作。雖然該方塊的所有功能可由一顆元件提供,設計人員也能依照圖1方式,利用多顆DSP執行這些編碼作業。

|

| 圖4 轉碼分割:上面的方塊只做為解碼器,下面的方塊 |

碼率轉換運算消耗資源少

視訊串流有時也須要執行碼率轉換(Transrating),這類轉換方式會將壓縮後的位元串流轉換成同樣標準、但位元率較低的另一個串流。編碼速率轉換通常是為了縮小畫面,以便在較低解析度的小型螢幕上顯示;或是在同樣解析度下提高視訊壓縮比,以便減少記憶體需求;或是在傳送畫面時降低位元率,以便將多個視訊串流送至頻寬有限的網路。

碼率轉換比轉碼簡單,只需各半個編/解碼器,還能重複使用原始位元串流所含的許多資訊,因此是視訊鏈中運算最少的工作,且僅需低度的處理器間通訊。

圖5顯示將碼率轉換工作分給兩顆元件的方式。上面的方塊提供解碼器/再編碼器功能,由於不須執行整個編碼作業,所以操作速度比標準編碼快。下面的方塊則執行解碼和再編碼作業所需的移動補償功能。

|

| 圖5 碼率轉換作業分割方式包含半個解碼器和半個編碼器,兩者皆由上方的功能方塊提供。 |

解碼適用功能分割

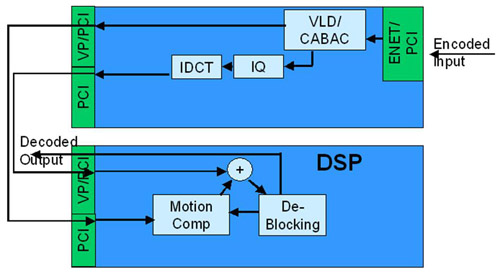

視訊鏈的最後一個步驟是解碼,但只能採用功能分割的作法。H.264位元串流會以複雜方式將其構成部分混合在一起,因此無法簡單將位元串流分為多個部分以便分開處理。功能分割雖會限制這項作業所能使用的處理器數目,但因解碼作業的運算需求不如編碼作業高,因此只須使用較少的DSP,但還是需要良好的處理器間通訊功能。

圖6上方的方塊會執行可變長度解碼(VLD)或使用內容調適二位元演算編解碼(CABAC)方法,下面的方塊只負責移動補償和塊狀畫面消除。

|

| 圖6 解碼作業分割,下面的方塊適合改用FPGA。 |

視應用不同 元件差異大

設計人員為各種分割方式選擇DSP時,必須將DSP的運算能力和價格列入考慮。根據經驗,高效能通用DSP成本通常為100~300美元;視訊專用DSP成本則在40~80美元間;而低成本元件則在10~20美元間。

表1顯示各種DSP可為高階視訊系統提供的功能,其中每項作業還能再增加一個FPGA加速器。

表1 H.264編碼解碼器的硬體平台和建議應用範圍

高效能DSP提供標準產品最強大的運算能力,這些通用元件很有彈性,因此在分割視訊工作、和將演算法客製化,或增加不同功能時,就能選擇許多不同的作法。高效能DSP的彈性還能帶來良好的擴充能力,廠商可利用這些DSP發展從數顆元件到高達六萬四千顆元件的系統。高效能DSP也非常適合編碼和轉碼等運算量龐大的作業,因為其強大運算能力可節省所需要的DSP數目,但這類DSP對碼率轉換等運算量較少的工作就有點大材小用,也可能缺少解碼應用所需的高速視訊I/O能力。

當用於編碼時,兩顆高效能DSP就能滿足720p30主要類別(MP)的視訊要求,即720條垂直行,每秒30格畫面非交錯或循序掃描,使用H.264主要類別;若將六顆處理器組合在一起,就能處理1,080i60交錯式主要類別視訊。轉碼應用只要使用三顆這類元件就能應付730p60基本類別(BP)視訊要求,四顆DSP就能支援1,080i60主要類別視訊。

如前文所述,這些DSP在編解碼器裡必須共用龐大的資料,而且需要強大的處理器間通訊功能,因此在選擇元件時一定要確定其具備這些特點。舉例來說,高效能DSP就包含SRIO高速資料連結功能,這種封包交換式互連技術能在4x鏈路上支援高達10Gbit/s的傳輸速率,這表示一條1x鏈路就足以在不同裝置間傳送原始格式的1,080i高畫質內容,一條4x鏈路則能在裝置間傳送1,080p高畫質原始視訊。

如果結合DSP和FPGA執行720p30主要類別視訊編碼,只要一個DSP就能滿足需求,而1,080i60則需要兩個DSP。若要為這兩種格式進行轉碼,那就需要一個FPGA和兩個DSP。碼率轉換和解碼應用則不須將DSP和FPGA搭配使用,因為這種作法的成本太高且耗電量也過大。

視訊專用DSP有效增加效能

有些工作適合使用視訊專用DSP,因為這類的DSP有特別設計的視訊I/O,還有專門的硬體加速器可以處理部分的視訊演算法。其成本和電力需求都低於通用DSP,而且儘管視訊專用DSP的視訊I/O並不是為了提供高效能的處理器間通訊而設計,但必要時也能作為這項用途。正因如此,通常會將處理器數目限制在兩至五顆之間。

除此之外,這些晶片也是為了單處理器系統應用而設計,因此最適合將畫面分為多個片段處理的編碼器分割方式。其他可能的應用領域包括前面介紹的所有視訊鏈處理步驟,唯一例外是運算量較少的碼率轉換應用,因為這種作法的成本太高。由於視訊專用DSP具有強大的運算能力和加速器,故只要兩顆這類DSP就能執行480p30主要類別視訊編碼,兩顆元件就能支援1,080i60主要類別視訊。轉碼應用同樣只要兩顆元件就能處理480p30主要類別,1,080i60主要類別視訊也只需四顆晶片。這些元件還包含特別設計的I/O,適合解碼應用,只要兩顆視訊DSP就能滿足高畫質解析度需求。

開發人員還能把FPGA加入系統,提供強大的加速器支援,FPGA對採用功能分割或綜合分割方式的編碼設計很有幫助。一個視訊DSP和一個FPGA就能應付720p30主要類別視訊編碼和720p60主要類別視訊轉碼。若是解碼作業,DSP和FPGA搭配的組合就能支援720p30主要類別視訊;若是再增加一個視訊DSP,系統就能支援1,080i60主要類別視訊。不過,對於運算需求不大的碼率轉換而言,這類組合的成本也顯得過高。

低成本DSP仍有舞台 碼率轉換為首例

碼率轉換工作極適合使用低成本DSP,只是這類DSP通常都沒有處理器間通訊功能或視訊連接埠等週邊,所以設計多晶片系統時會較困難。如果系統必須移動大量資料,I/O部分的設計可能太過複雜,反而會消耗晶片本身所節省的成本。

低成本DSP的運算能力雖有限,不適合編碼、轉碼或解碼作業,但對不需要視訊I/O的碼率轉換而言,兩顆低成本DSP就能滿足其需求,而且解析度可高達720p30基本類別。另一種作法是增加一個FPGA,以便保留低成本優勢和增強加速功能。但即便如此,這種組合仍只適合運算需求不高的作業,且無法提供良好的處理器間通訊能力。這種方式也和單純使用DSP的設計一樣,只需兩個DSP和一個FPGA就能滿足720p30基本類別視訊的碼率轉換要求。

總而言之,隨著消費者對高畫質視訊的要求不斷提升,設計人員必須注意畫質對系統的處理能力需求所造成的影響,而智慧型分割方式又能如何滿足這些挑戰。設計人員還必須了解市場出現最新的DSP,以及這些具有特殊和更強大功能的元件所能發揮的作用。

(本文作者任職於德州儀器)