三維晶片整合是一種可提供更高接線密度的嶄新技術,由於能使系統晶片的面積大幅縮小,縮短訊號延遲時間,因此可以提升系統的功能,更被視為讓摩爾定律繼續前進的關鍵。

歸功於過去台灣半導體產業垂直分工的獨特優勢,與世界強勁成長的半導體需求,台灣過去10年來半導體產值有超過十多倍的成長。在擁有資訊產業最完整的製造與價值鏈優勢帶領下,台灣不但有非常多樣化的IC半導體產品,更擁有位居世界第一的晶圓代工及電子構裝產業,及位居第二的記憶體(DRAM)產量及IC電路設計的產業。

但從需求面來看,自2004年以來世界半導體產業市場成長率逐步降低,連帶著台灣的半導體體產業成長也受到影響。筆者相信這是因為過去推動半導體產業發展主要驅動力--元件縮小化已經面臨瓶頸,也因此過去元件縮小化帶動功能性提升以及價格降低,最終刺激市場成長的模式已越難以持續。這對台灣的半導體產業尤為不利,因為台灣資訊產業的產品規格常常受制於國際大廠,台灣若無法持續提升產業技術優勢,隨著產業技術的成熟,半導體產業將面臨後續追隨者的強烈競爭。因此台灣半導體產業急須尋找一條新的出路。

從產品面來看,現今電子產品的功能不斷的提升,手持產品風行,產品必須朝著輕薄短小的趨勢發展,所以將很多不同功能的晶片整合於在一起已經是必然的趨勢,從而創造出對新型態連接導線(Interconnect)技術的需求。

3D IC技術正是這一問題最佳的解決方案:3D IC技術的建立不但將能延續台灣過去分工合作的優越傳統,建立我國半導體產業的獨特產業優勢,也將對於我國半導體產業從大量資本投入的代工製造模式到知識密集的設計轉型提供最大的助力。

TSV為三維晶片整合關鍵技術

3D IC技術是指利用矽晶穿孔(Throught-silicon Via, TSV)的連接與超薄晶圓薄化,將傳統二維晶片轉變成三維的立體堆疊技術。由於3D IC能有效地善用空間並縮短傳輸的距離,提供極低電阻連接,因此3D IC技術能在輕薄短小與價格的要求下提供多功能整合、高效能等許多優點。

3D IC技術之前景與重要性,目前已經廣泛受到肯定,以目前最大數量的處理平台--手機來說,未來要發展多功能整合、高效能低功耗,且能適合於手機輕薄短小之空間限制者,唯有3D IC技術。其他如以目前市場上固態硬碟(Solid State Drive, SSD)、多核心處理器等之發展趨勢與市場需求來看,3D IC技術之來臨已經指日可待。

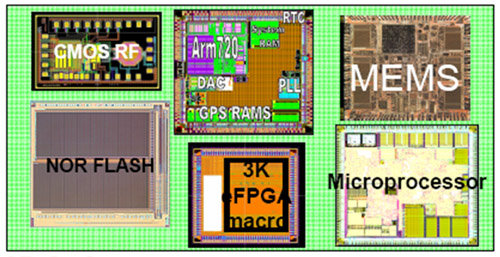

三維晶片整合技術也是認為是超越摩爾定律(More than Moore)的關鍵技術之一。圖1簡單說明從二維的系統單晶片(SoC)進展到三維積體電路時面積會大幅縮小,這是因為可以將系統中所有晶片,如射頻(RF)、快閃記憶體(Flash)、微處理器、微機電系統(MEMS)等晶片利用垂直整合的方式堆疊起來。三維晶片整合技術的優點有以下四點,分別是實現異質晶片整合(Heterogeneous Integration)、縮小晶片面積(Form Factor)、增進電性的效能及降低成本。

|

| 圖1 二維的SOC晶片可以利用垂直整合技術轉變成三維積體電路 |

三維晶片整合主要好處之一,在於實現異質晶片的結合,因為這種技術可以將不同基板與製程的晶片整合堆疊,以達到3D系統單晶片(SoC)的目標。例如可以利用此技術將以砷化鎵(GaAs)為基板的光電或高頻元件與以矽基板為主的邏輯/類比製程元件整合在一起。另外可以使用最合適的製程分別進行晶片的製作,然後再整合堆疊,以達到高品質與低成本的目標。

至於在縮小晶片面積方面,現今產品不僅朝向輕薄短小的趨勢發展,同時也要求產品的功能越來越多且越來越強。所以在較小的面積裡增加更多的功能是業界普遍追求的目標,特別是可攜帶式產品更是如此。三維晶片整合技術中利用導通孔可以增加晶片的金屬導線密度,並且克服傳統封裝的空間限制,使得產品的體積和面積能大幅度的縮小下,產品的功能或密度卻能不斷提升。

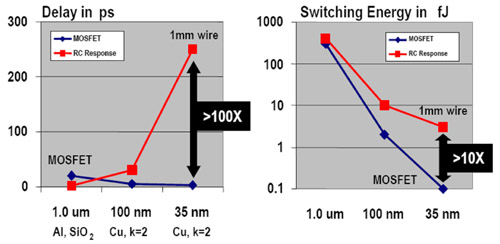

從電路的效能面來看,隨著半導體製程的不斷微縮(Scaling),後段製程中金屬導線的電阻與電容效應所產生的訊號延遲,已經變成影響元件特性的主要原因之一。雖然後段金屬化製程也不斷提出新的材料及技術,例如銅導線取代傳統的鋁導線,而後再將低介電(Low-k)材料與銅金屬導線整合以大幅降低訊號延遲時間,但這些新材料的導入所能帶來的改善跟元件本身的的訊號延遲時間(圖2)相比,猶如九牛之一毛。而三維導線技術能夠解決訊號延遲太久的問題。因為三維導線是利用導通孔以使晶片與晶片間能垂直導通,縮短了導線長度,所以提升了元件的速度,以及減少了訊號延遲時間,並進而降低了晶片的功耗。

|

資料來源:Prof. J.Meindl, Ga Tech, IFC/MARCO

圖2 導線與元件本身的訊號延遲與能量消耗的比較 |

至於在成本面上,根據三星(Samsung)針對NAND快閃記憶體所進行的成本趨勢預估,傳統利用尺寸微縮的方式來降低成本的方法,在元件密度提升到64Gbit時會面臨瓶頸,成本不易再繼續降低。但三星認為三維晶片整合技術可以使成本的降低曲線繼續延續。

國際大廠紛紛搶進布局

根據國際大廠研發狀況(表1)。目前開發的產品集中在動態隨機存取記憶體(DRAM)、快閃記憶體和互補式金屬氧化物半導體影像感測器(CIS)等產品上,且都預估在2009年以後產品會問世,至於邏輯等先進製程的產品則可能會在2012年以後才有產品推出。從表1中可以發現在DRAM產品中,導通孔的尺寸均小於其他的產品,而且大多是填充複晶矽。至於導通孔的蝕刻方式幾乎都是使用DRIE製程,而美光(Micron)使用的雷射製程據推測應該是使用在CIS的製程中。

表1 國際半導體大廠在3D IC領域的研發狀況

有投資才有回報 台灣業界宜積極介入3D IC發展

現今電子產品的功能不斷提升,但是產品仍必須朝著輕薄短小的趨勢發展,所以必須在更小的晶片上容納更多功能的挑戰,三維晶片整合技術是必然的發展方向。目前國際大廠相關開發的產品集中在DRAM、Flash和CIS等產品上,預估在2009年以後產品會問世。如何與相關單位一起努力將導通孔導入電路設計與產品開發之中,將是台灣半導體產業未來最重要、高難度、但將會有極豐碩回報的課題。

(本文作者任職於工研院電光所)

| 參考文獻 |

[1]. Kenji Takahashi, etal, 2004 Electronic Components and Technology Conference, pp.601-609.

[2]. M.Umemoto, etal, 2004 Electronic Components and Technology Conference, pp.616-623.

[3]. K.Hara, etal, IEEE Transactions on Advanced Packaging-B, Vol. 28(3), 2005, pp.367-376.

[4]. Deniz Sabuncuoglu Tezcan, etal, 2007 Electronic Components and Technology Conference, pp.643-647.

|