現階段可攜式裝置的系統越來越複雜,功能也越來越多元,對於電源管理晶片的要求也日漸嚴苛,若非具備高效能、低成本與易於設計等特色將無法受到廠商的青睞。而FPGA擁有易於重新編程設計的優勢,再加上整合微控制器,因此可滿足上述所有的要求。

現今的電源管理必須對功耗和電路板空間最少的影響之下,達成高階的系統電源控制。市面上的智慧型數位電源管理解決方案(IDPM)以低功耗和可組態的單晶片設計,提供高階的電源管理。

該平台不但可模組化也具有延展性,包含一個可容易擴展到控制多達三十二個數位負載點(DPOL)電源供應的基本解決方案。另外,廠商的現場可編程閘陣列(FPGA)工具集讓硬體和軟體都很容易修改,所以可進行快速的整合並迅速地打入市場。

電源管理解決方案需功能強大、小型化,且易於重複使用。IDPM解決方案在單一晶片上提供一個功能齊全的電源管理器,易於修改以支援不同印刷電路板(PCB)的功率需求。由於這個設計提供數位負載點的電源供應,並使用Fusion FPGA的嵌入式快閃記憶體儲存資料,只需很少的成本就可重新加以利用。新的設計只須將所需的DPOL加到基本的電源管理設計,並將與設計相關的特定功率參數存入FPGA內部的快閃記憶體(Flash Memory)。

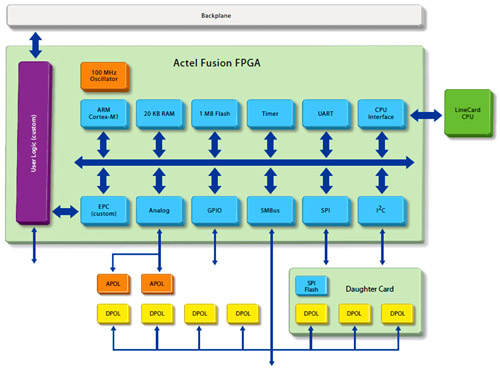

圖1顯示一個典型的IDPM系統,這系統包含FPGA及最多可達三十二個連接到標準系統管理匯流排(SMBus)的DPOL。其中的FPGA內具有一個基於Cortex-M1的微處理器(MPU),以及連接到安謀國際(ARM)區域匯流排的支援周邊,FPGA內達1MB的非揮發性快閃記憶體可用來儲存ARM程式碼,以及與設計相關的特定功率參數。與設計相關的特定參數是根據電路板上的電源設計決定,包括DPOL元件的數目、DPOL在SMBus上的位址、DPOL配置數據、時序資訊及其他設計相關的數據。當ARM處理器開機時,元件將讀取設計相關的特定參數,並透過SMBus決定POL裝置時序,一旦該卡供電完成,IDPM將監控所有的功率軌道,報告並記錄任何異常情況,執行任何綠色節能措施,並回應系統處理器有關對電源系統的控制和狀態查詢。在這架構下,支援子卡很容易。只要將SMBus布線到子卡上,子卡就可視為機板設計的延伸。另一方面,也可藉由小型Fusion元件,作為精簡版的機板電源管理器,建構成為一個獨立的子卡架構。

|

| 圖1 典型的IDPM系統 |

此電源管理器包括一個簡單的狀態機,根據儲存在快閃記憶體內的設計相關特定參數,決定子板上DPOL時序,一旦決定時序後,機板電源管理器就可以監測和控制子卡的電源。由於並非所有的電源管理解決方案皆可完全數位化,FPGA包含一個專屬的類比區塊,可以用來控制任何類比負載點(APOL)或超低壓降穩壓器(LDO)。此外,FPGA的類比區塊完全支援類比電源的裕度調整與修整功能,廠商也提供可執行這些功能的矽智財(IP)。

作為一個真正的單晶片解決方案,FPGA擁有所需的額外元件,包括供程式執行的內部SRAM、一個內建的振盪器及基於鎖相迴路(PLL)的時脈管理系統,可自定功能的FPGA空間,和內部1.5伏特(V)穩壓控制器用以供電給FPGA核心。本文範例的解決方案,是基於廠商的快閃記憶體技術達成穩定性和可靠度,並具有真正的瞬間啟動能力。不像基於SRAM的解決方案在開機時須進行組態設定,FPGA元件開機時即可開始作業,因此具有可靠的電源循環特性。另一個額外好處是內在的單一事件擾亂(SEU)容錯技術,FPGA元件在地面的應用不受SEU影響,因此具有非常高的可靠度。IDPM設計的諸多特點都可提升可靠度,包括足夠的快閃記憶體可儲存多份程式碼和資料的鏡像備分,提供由錯誤更正碼(ECC)保護的SRAM IP,具監控計時器並可重新啟動的微處理器,所有這些特點都將使電源管理解決方案穩如基石。

IDPM子系統設計簡易

從IDPM子系統可獲得許多的好處,其涵蓋整個產品生命週期的每個領域,包括簡化工程設計、原型機除錯和品質認證測試、降低生產成本、減少不良品分析及增添許多產品特點。

將設計相關的功率參數儲存在板載快閃記憶體的概念,讓重複使用變得非常容易。完全不須要將硬體重新設計。要設計一個新的電源子系統相當簡單,只要把IDPM模組加入Schematic電路圖,添加所需的DPOL到SMBus,並建立一個描述電源子系統的相關數據文件既可。

原型機除錯也很容易,只要連接到ARM通用異步收發器(UART),就可輕鬆讀取所有POL的狀態,包括實際電壓和功耗。透過UART即時訊息或修改儲存在快閃記憶體內的電路板相關參數,就 可改變電源供應參數或時序,藉此可減少在電源工程上的成本。當電路板須變更被動元件或增加測試掛鉤,只要透過UART指令或是修改快閃記憶體資料,就可全方位的監測或改變電源設計,因此幾乎可避免掉關機時間。而品質認證測試人員只要透過UART,或是透過其他能存取IDPM的處理器,就可用簡單的軟體指令,輕鬆進行電壓裕度測試和監控系統狀態。

現今許多設計都利用DPOL元件的可編程性,然而,製程上DPOL被當成和可編程邏輯元件(PLD)一樣,一經燒錄,就被標上不同的原始設備製造商(OEM)零件編號作為區分,隨製程不同,這個步驟將增加管理上的成本,而且也可能增加庫存成本。此外,燒錄這些元件將額外付出昂貴的生產成本。IDPM解決方案將所有DPOL鏡像儲存在FPGA快閃記憶體,空白的元件可先安裝在卡上,當IDPM電路首次被啟動時,可自動燒錄所有的DPOL,這個方式解決以上所有的問題,同時讓更換損壞的DPOL也變得容易,只要用一個全新空白的元件替換損毀的DPOL晶片,當IDPM啟動時,將偵測到空白的DPOL並加以燒錄。

元件內的嵌入式快閃記憶體也可以用來記錄板上發生的任何異常事件,包括超出額定的電壓和溫度,電路板重置和關機再開週期,系統中央處理器(CPU)的不可遮罩中斷事件(NMI),以及其他異常事件。許多系統雖有事件記錄系統,但通常須協調多個處理器和裝置。將系統監測處理器與快閃記憶體記錄緊密結合在同一封裝內,使得事件記錄變得簡單又可靠。同時,以微處理器為基礎的IDPM可專屬存取所有系統關鍵裝置,提高錯誤涵蓋率。

透過JTAG埠進行重新燒錄

FPGA內的IDPM設計讓現場重新燒錄變得相當簡單且具有彈性。通常只要對儲存在快閃記憶體內的參數檔案加以修改,即可修改電源時序和控制。重新燒錄快閃記憶體有幾個方法,包括新檔案可從UART下載、從ARM處理器支援的線卡CPU,或從透過JTAG埠的傳統ISP。如圖1所示的典型設計之中,1MB的嵌入式快閃記憶體邏輯上分為兩個相等的分割,第一個分割包含電源供應參數檔案和應用程式碼;第二個分割則可作為現場升級這些檔案之用。當開機時,ARM的開機程序會檢查最新有效的電源供應參數檔和應用程序代碼,並加以執行,這個二分割措施可確保總有一個有效的參數檔和應用程式碼可供使用,經由下載新的應用程式碼,很容易可添加系統功能與滿足客製化的需求。

IDPM同時也支援由JTAG現場重新燒錄FPGA鏡像,FPGA元件具有輸入/輸出(I/O)取樣保持功能支援FPGA鏡像的重新燒錄,所有FPGA的I/O都可以透過JTAG取樣保持目前的狀態,這將維持線卡的供電狀態並凍結目前的電力系統狀態。接著透過JTAG重新燒錄FPGA,燒錄完成後,FPGA的I/O將被釋放,同時FPGA內部進行重新開機,這個重置的動作也讓線卡關機再開,並促使FPGA的改變生效。廠商的Libero IDE整合設計環境支援對I/O取樣保持設定、內部重開機,以及將這些資料嵌入在JTAG燒錄檔案中。新式特定應用積體電路(ASIC)設計為增加良率,容許電壓隨製程做少許變動。若以ASIC的核心電壓來看,於正常值加上或減去幾個百分點(取決於良率曲線何處開始下降),將可修復更多的晶粒供使用,且IPDM可從每個ASIC讀取製程資訊並設定合適的核心工作電壓。最後,由於客戶要求更多的特性和功能,基於微處理器的IDPM可透過軟體更新滿足客戶的需求,IDPM擁有所有的功能,包括先進系統監測與控制、事件記錄和綠色節能控制,使其適用於新式電源系統的設計。

現今要設計複雜的系統,需要有高效能的電源管理,來滿足客戶特別的需求,智慧型電源管理在綠色節能和減少功耗上將不可或缺。

(本文作者任職於愛特)