隨著萬物皆可聯網與寬頻通訊無所不在的趨勢日益顯著,雲端運算也因而受到重視。看好雲端通訊基礎建設市場商機,FPGA廠商藉由高整合、低功耗的產品全力搶攻,已成功在雲端應用市場站穩一席之地。

現場可編程閘陣列(FPGA)廠商通吃雲與端市場商機。近期物聯網(Internet of Things)機器對機器(M2M)應用蓬勃發展,促使無處不在的寬頻網路世界逐漸成型,也加深雲端運算(Cloud Computing)的發展與落實。

瞄準雲端商機,FGPA廠商分別以先進製程、新的封裝方式,以及高整合度的產品,全力布局雲與端。並希冀透過更完整的參考設計與開發工具,讓通訊相關工程師擴大採用FPGA,從而取代更多特定應用標準產品(ASSP)與特定應用積體電路(ASIC)方案。

雲端商機誘人 FPGA廠商群起攻之

雲端商機包含遠端的通訊設備,以及用戶端的行動裝置等。市調機構IDC預期,由於雲端的發展持續火熱,預估從20122015年這段期間,全球將新增將近一千四百萬個雲端運算相關工作,其中大約有半數是落在中國大陸、印度;而2015年雲端相關設備年度銷售額將達到1兆1,000億美元。

如此龐大的商機,吸引FPGA廠商積極投入,其中賽靈思(Xilinx)與Altera專注於遠端雲如網通設備、寬頻網路骨幹等領域;萊迪思(Lattice)則專攻行動裝置終端市場;而美高森美(Microsemi)則是著重在微波與航太領域。由此可見,在通訊領域中,FPGA業者各自分工,通包雲端商機,而通訊領域也為FPGA業者創造相當大的營收來源。

|

| 圖1 賽靈思亞太區銷售及市場副總裁楊飛表示,在無線通訊設備的設計架構上,採用高整合度FPGA也可簡化設計架構,同時節省功耗與成本。 |

賽靈思亞太區銷售及市場副總裁楊飛(圖1)表示,具聯網功能的智慧型手機、平板裝置(Tablet Device)與物聯網越來越普及的態勢下,無所不在的寬頻通訊和巨量資料的傳輸,驅動整體IT產業轉朝網際網路發展,不僅帶動長程演進計畫(LTE)此一行動寬頻通訊技術的商機,也讓相關網通設備對更高效能及傳輸速率、更小尺寸和低成本的元件需求逐一顯現。

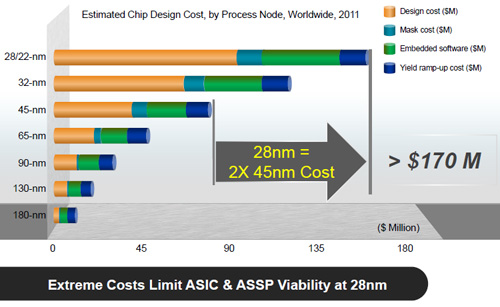

然而目前ASIC與ASSP已無法依循摩爾定律(Moore's Law)透過先進製程達到節省成本的目的。根據Gartner統計資料顯示,28奈米(nm)製程的ASIC與ASSP研發成本,是45奈米的兩倍(圖2),對於許多公司而言,將無法承受翻倍成長的製程費用;再加上通訊標準日新月異,元件在設計過程中無法重複修改,又是額外的成本支出,不過FPGA卻可解決上述問題。

|

資料來源:Gartner

圖2 各製程節點所須花費的成本比較 |

因此FPGA在通訊領域已展露頭角,且網通設備導入的FPGA元件數量正持續攀升。楊飛指出,雖然無法進一步精算各類網通設備中採用的FPGA顆數,但各種網通設備對於FPGA的需求量確實不斷升高,從賽靈思總體營收來看,有線與無線通訊領域無疑是貢獻該公司營收最大的來源,約占4347%。

Altera於7月剛公布的財報則指出,該公司第二季包括40奈米和28奈米新產品的銷售繼續增長,約在30%以上。以28奈米高性能旗艦產品Stratix V來看,其連續增長高達190%,主要來自於通訊領域的需求。

值得注意的是,為強化通訊領域的市場範疇,提供功耗與價格更易接受的FPGA元件,各家FPGA廠商亦進行一連串的技術演進,以期可站穩一席之地。

不再是配角 FPGA SoC躍升系統等級

為打破FPGA僅能擔任整體通訊系統中增加邏輯角色的現況,提升FPGA處理的效能,並整合FPGA與處理器硬體核心已成大勢所趨。包括賽靈思與Altera近期相繼推出FPGA系統單晶片(SoC)的產品。

楊飛表示,在FPGA中整合處理器核心,增加處理的效能後,再融合周邊的數位與類比電路,可讓FPGA元件躍升為通訊設備中電子系統的核心,而不再只是輔助處理器的配角。業者即可利用FPGA SoC進行系統整體設計與編程,且更具成本優勢,對於推展FPGA於通訊市場的發展,將有一定的助力。

|

| 圖3 Altera亞太區高級市場經理羅嘉鸞表示,未來將處理器放入FPGA會成為未來一大發展趨勢,且FPGA會占晶片面積不到50%。 |

Altera亞太區高級市場經理羅嘉鸞(圖3)表示,該公司於2011年啟動的OpenCL計畫,為矽晶片融合的技術。由於工程師需要高速運算功能開發系統,然而單核心或者多核心中央處理器(CPU)無法實現其需求,因此OpenCL標準受到系統規畫、工程管理、演算法設計和軟體工程師的歡迎。

透過OpenCL開發專案,OpenCL的優勢已不僅實現在繪圖處理器(GPU)上,而是進入FPGA大量的平行功能中,提高異質架構系統的加速功能,並降低功耗,且讓產品能夠更迅速上市。

OpenCL帶給FPGA設計人員的優勢包括更快的性能,亦即使用GPU或者FPGA加速設計或應用;透過使用標準模型,包括語言、應用程式介面(API)、記憶體層次等進行設計。換句話說,對現有FPGA用戶而言,可在目前的C語言中對演算法進行模型建立,然後轉換到HDL中,加速產品上市。更重要的是,與採用GPU的異質架構系統相比,FPGA SoC功率消耗為五分之一。

羅嘉鸞認為,FPGA在經過從上世紀90年代到2000年的快速發展、隨後短期的泡沫破裂,以及近幾年的平穩增長的發展階段,未來矽晶片融合將是大勢所趨。

事實上,通用處理器同樣可透過軟體編寫程式實現不同的應用,使用非常靈活但同時功效較低;ASSP和ASIC等專用晶片透過固定化硬體針對專門應用,無法進行程式設計,功率效益高但靈活性差。

羅嘉鸞指出,矽晶片融合的FPGA在「微處理器+數位訊號處理器(DSP)+專用IP+可程式設計」的混合系統架構下,可以解決上述的兩難問題,又能兼顧靈活性和效率。

透過先進製程技術,FPGA得以從配角轉為主角,但這並不表示FPGA將取代CPU或處理器。楊飛強調,FPGA與處理器應用的環境仍大不相同,FPGA SoC是將周邊子系統進一步整合,簡化整體設計架構,不過在要求小型化與低功耗的嵌入式系統(Embedded System)中,具備成本優勢和提升至系統等級的FPGA將有更大發揮空間。

3D IC/28奈米先進製程扮推手

分析FPGA SoC可具備高效能、低功耗與小尺寸特性的原因,先進製程技術實為關鍵。楊飛表示,FPGA在製程技術的發展已較ASIC與ASSP快速,目前包括賽靈思與Altera等FPGA業者已導入28奈米製程並陸續進入量產,且也開始採用三維IC(3D IC)技術將異質晶片整合為SoC。

據了解,賽靈思與Altera皆與台積電合作,研發並生產28奈米FPGA。其中賽靈思採用28奈米高效能低功耗(HPL)製程進行3D IC產品的研發;Altera則利用台積電晶片-晶圓-基底(CoWoS)整合製程,開發異質混合3D IC測試平台,包括前端製程技術,以及後端裝配和測試解決方案,用以確保產品的良率和效能。

透過3D IC與28奈米技術,賽靈思與Altera將可提供效能更高,系統功耗、成本更低,尺寸更小的產品予客戶,進而滿足通訊市場的要求。

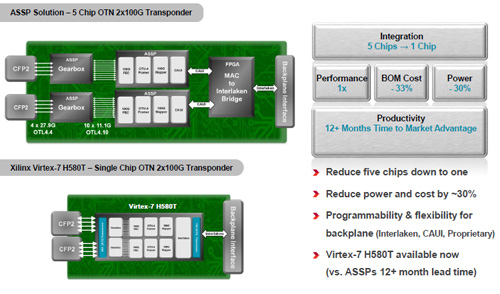

楊飛舉例說明,行動寬頻網路的發展直接帶動後端骨幹網路頻寬需求提升,目前光傳輸網路(OTN)設備中,傳統CFP裝置為10G×10G收發器接口,最多能做到四個CFP的400G密度,功耗為600瓦(W)。若以現有的架構進行設計,需要包括ASSP、接口控制晶片、FPGA與媒體存取控制(MAC)共五顆晶片,才能完成。

不過,採用賽靈思8月甫供樣的Virtex-7 H580T高整合、利用3D IC技術的單晶片方案,僅須一顆FPGA SoC產品即可達到相同效能,但功耗與成本僅須三分之一,還可節省1年開發時間(圖4)。但為滿足通訊業界對頻寬的需求,新一代CFP 2規格則須將串列與解串列器(SerDes)提升至4×25G,密度將從既有的400G提升一倍至800G,則須兩顆H580T FPGA。

|

資料來源:賽靈思

圖4 透過高整合度FPGA簡化4×25G OTN系統設計 |

楊飛並透露,賽靈思2013年第一季將發布的下一代產品Virtex-7 H870T,擁有28G十六路與13G七十二路的SerDes兩種規格,將可更加簡化系統設計,以因應20142015年CFP 2 800G OTN規範的龐大市場需求。

市場策略重新定調 萊迪思轉攻消費性電子

相較於賽靈思與Altera專攻網通設備,布局遠端「雲」市場,萊迪思則鎖定消費性電子,亦即「端」的部分做為未來主要發展重心。在購併矽藍(SiliconBlue)後,萊迪思將市場發展重心自過去著重的通訊領域,調整為消費性電子;而矽藍iCE產品也將成為日後主要推展重點,以避免在通訊領域與Altera、賽靈思正面衝突。此外,萊迪思近期也與聯電於40和28奈米(nm)製程進一步合作,以提供更具低功耗與低成本特性的FPGA。

|

| 圖5 萊迪思企業行銷副總裁Doug Hunter表示,為強化消費性電子市場地位,萊迪思與應用處理器廠商如高通,維持密切的關係,讓FPGA產品可有效輔助處理器。 |

事實上,過去萊迪思在通訊、影音視訊、汽車與消費性電子,皆投入不少資源耕耘;但隨著矽藍的加入,該公司在消費性電子領域的產品陣容已更為厚實。萊迪思企業行銷副總裁Doug Hunter(圖5)表示,在合併矽藍後,萊迪思的產品方案可較其他FPGA廠商產品,更能滿足消費性電子領域日益嚴苛的低功耗、小尺寸與低成本要求,因而萊迪思毅然決定轉而將更多的發展資源放到消費性電子,與其他FPGA廠商進一步區隔。

除收購矽藍外,為提供消費性電子市場更低功耗與更小尺寸的產品,萊迪思下一代產品也將挺進28奈米製程。Hunter坦言,矽藍特有的互補式金屬氧化物半導體(CMOS)製程技術相當成熟,萊迪思既有的FPGA雖整合嵌入式快閃記憶體,擁有較高的效能,但記憶體的製程演進無法如CMOS快速,因此在降低成本與尺寸上,限制較大。有鑑於此,未來萊迪思將善用矽藍CMOS製程技術,發展更小、更低功耗與成本的產品。

值得注意的是,先前矽藍40奈米iCE產品是由台積電代工,不過,未來萊迪思將把現有台積電生產的產品全數轉由聯電製造。Hunter強調,由於矽藍製程技術可更加滿足消費性電子所需,未來萊迪思與聯電的合作將聚焦40奈米和下一代的28奈米的iCE系列產品;而轉由聯電代工的新產品,也將廣泛應用到萊迪思各目標市場。至於萊迪思現有的產品,也將持續給予客戶支援。

構建全可編程時代 參考設計為另一關鍵

為擴大FPGA應用範疇,加速取代ASIC與ASSP,進一步落實全可編程時代,FPGA廠商不僅在FPGA中整合處理器、採用更先進製程,更持續降低FPGA元件的成本與功耗,並推出更易用的參考設計與開發套件。

Hunter指出,萊迪思將開發更多低功耗、成本的產品,以及參考設計、開發套件等產品,讓工程師更易接受並轉用FPGA。此外,為強化FPGA處理效能與控制能力,未來,萊迪思亦計畫將產品整合8051或32位元微控制器(MCU)。

羅嘉鸞則表示,設計軟體是實現FPGA中硬體可程式設計功能的關鍵工具,因此FPGA廠商皆大量投入研發,讓軟體工具效率更高、更可靠,且讓用戶體驗更好。更何況,工程師一般並不希望投入太多時間學習新工具,而是能以很短的準備時間就可開始進行設計工作,因此熟悉的工具將是保持客戶忠誠度的關鍵。

相較於其他FPGA業者積極布局雲端市場,美高森美則持續在航太領域發布可符合適用於嚴苛環境的FPGA與可客製化系統單晶片(cSoC)。該公司表示,可在極熱和極冷的溫度下能可靠運行的FPGA,對石油勘探應用、航空航太和國防設備,以及其他用於嚴苛工作環境的產品來說,是不可或缺的特性,而此特性亦為美高森美產品發展的主要方向,藉此與其他FPGA廠商做出市場區隔。

總的來說,隨著FPGA的效能不斷提高,可預見未來雲端通訊設備中,FPGA將被大量導入。而FPGA廠商為掌握雲端商機,不僅領先傳統半導體產業,致力於先進製程節點與封裝技術的發展,進一步推出尺寸、功耗與整合度皆具備競爭優勢的產品,並發布更多易用的參考設計與開發套件,加速設計工程師以FPGA取代ASSP與ASIC。