電磁干擾一直是許多系統設計工程師最頭痛的問題,SiP方案由於先天具備低EMI優勢,因此在許多對EMI要求嚴苛的應用中,SiP均可提供理想的解決之道。 特別是在類比電路設計部分,要針對電路的EMI進行設計最佳化,需要相當的專業能力,因此在這類元件中採用SiP封裝,不僅可降低EMI,更可協助設計人員更輕鬆地完成其任務。

最近有一組系統設計師在因應微創手術(MIS)而開發醫療成像設備上,因未仔細為該應用選擇切換式直流對直流(DC-DC)穩壓器而碰到了雜訊問題,切換尖峰的高能量顯現成雜訊,並透過視訊放大器的電源輸入饋送,出現在運算放大器的輸出,因而大幅降低了高解析度監視器上的圖像品質。該放大器的電源抑制比無法抑制DC-DC切換穩壓器的高頻雜訊,而設計師又不想透過在印刷電路板(PCB)上增加濾波器和遮罩,以解決此一問題,因為這將使設計更加複雜化。

這是一個非常詭異的現象,一個價值10,000美元的系統,其性能卻因為便宜得多的電路元件性能影響而大打折扣。最後,這個設計小組決定從頭開始進行重新設計,並仔細選擇一個替代的DC-DC解決方案。但是,線路板重複設計非常昂貴和費時,若當初選擇一個合適的穩壓器和電路板布局,就可避免這個窘境。

EMI問題為工程師長期惡夢

任何變化的電流或電壓都會以電磁(EM)形式產生能量。它在蜂巢式手機、PC、醫療掃描器、汽車、發射器、螢光燈、電源線等中以不同的強度出現。這種能量有一個在一定頻率範圍內定義的強度級,強度級隨距離不同而變化。所謂「雜訊」,儘管不是一個科學定義的術語,但是當EM能量干擾、中斷或禁止其他電子設備或元件工作時,雜訊就用來表示這種能量。這種情況也稱為電磁干擾(EMI)。

濾波器則是用來透過衰減某個頻率上或一個頻率範圍內的EMI強度來降低EMI。在空間中傳播的輻射能量可透過增加金屬和磁遮罩來衰減;跨在PCB線路上的傳導雜訊則可藉由增設鐵氧體磁珠和其他濾波器來加以抑制。EMI無法被消除,但是可以抑制到一個可以被其他通訊和數位元件接受的水準。此外,幾個管理機構也執行特定標準來確保EMI符合要求。

EMI是令許多工程師聞之色變的燙手山芋。很多設計工程師長時間不分晝夜地在EMI實驗室中,奮力用鋁箔、帶狀銅線、箝式濾波器和割傷的手指解決一個去不掉的設計問題,即使是經驗老到的工程師,對處理EMI問題也會感到恐懼。

大致而言,設計師最擔心的EMI類型為輻射。除了極少的例外,大多數系統都工作在一個要求每個產品的輻射都不得超過某些預先定義好的水準環境。理論上,如果每個產品都符合這些輻射水準要求,那麼整個系統的雜訊水準就足夠低,以致不必擔心易受影響的問題。

雜訊可以透過兩種線路傳導和無線輻射這兩種輻射管道對系統造成影響。傳導輻射發生在連接到一個產品的導線和布線上。由於雜訊集中到設計中的一個具體終端或連接器上,因此常可在開發過程中早期因應,以良好的布局或濾波器設計來保證符合傳導輻射要求。

無線輻射則是另一回事。電路板上攜帶電流的所有東西都會產生一個電磁場。電路板上的所有布線都是天線,所有銅片都是諧振器。除了純正弦波或DC電壓外,任何訊號都會在整個訊號頻譜範圍內產生雜訊,即使經過仔細設計,也沒有人在系統獲得測試之前就能掌握輻射的真實情況,且通常直到設計基本完成時,才能正式進行輻射測試。對此,設計工程師可透過採用經測試合格的元件和已知具有低輻射特性的元件,來增加設計成功的機會。

在美國,輻射和測試由聯邦通訊委員會(Federal Communications Commission, FCC)管理。最常遇到的規範是Federal Code of Regulation(CFR) FCC Part 15。該規範將無意輻射數位設備分成AB兩類,其中B類規範較為嚴格,定義的限值約比A類低10dB。

若工程師要開發B類設備產品,一個元件的輻射雜訊應比規定的限值低。究竟多低則取決於組成該系統的其他元件。如果該設備的輻射超過了B類的限定值,那麼必須設計某些方法來降低雜訊,如遮罩或轉換率限制。

歐洲所容許的電磁輻射一般由EN55022定義。另一個常用的規範是CISPR 22,這是來自國際機構 Comite International Special des Perturbantions Radioelectriques。這兩個規範類似於FCC Part 15,定義類似(但不是完全相同)的限定值,並將它們畫分成A和B兩個輻射類別。

DC-DC穩壓器SiP化有助克服EMI難題

為了協助設計人員克服EMI難題,凌力爾特(Linear Technology)提出DC-DC穩壓器微型模組化的構想,並將之轉化成實際產品。其所採取的方法,是對電源(即DC-DC穩壓器本身)上的傳導和輻射能量進行抑制。一個DC-DC微型模組是一個完整的DC-DC系統級封裝(SiP)。該封裝內部整合了電感、控制器晶片、金屬氧化物半導體場效電晶體(MOSFET)或開關元件、輸入和輸出電容器、以及建立在基板上的補償電路,並採用一個密封式表面黏著塑膠封裝,外觀看來就像一般的晶片元件。

一個切換穩壓器的雜訊主要是由接通和斷開時電流(和電壓)的快速開關行為所引起。本文以凌力爾特所推出的SiP化DC-DC穩壓器LTM4606和LTM4612作為範例,來說明完整且經過最佳化的SiP系統設計所能實現的低輸入和輸出雜訊,同時提供所有切換穩壓器電路的優點。

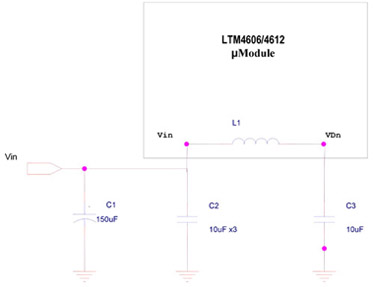

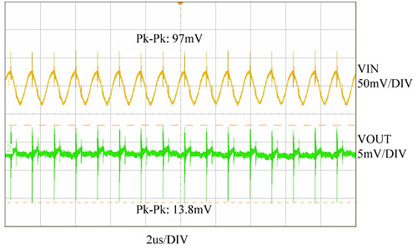

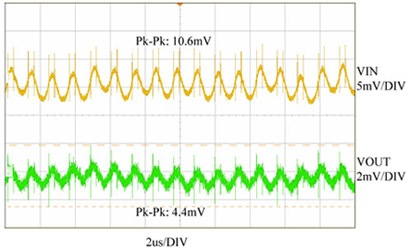

在本文範例方案中,模組內整合了一組輸入高頻電感於輸入端,以抑制輸入雜訊(圖1)。為了進一步地衰減低輸出雜訊,該模組更內建用於MOSFET的最佳化閘極驅動器和雜訊消除網路,以減少雜訊耦合。圖2與圖3則分別為未經雜訊最佳化的方案與該範例方案的輸入/輸出雜訊情況,由此即可看出,在完全相同的條件下(註),經過最佳化的SiP模組在抑制雜訊方面顯著高於未經最佳化的方案。

|

| 圖1 LTM4606中的π型輸入濾波器 |

|

| 圖2 一個類似模組的輸入和輸出雜訊(沒有低雜訊特性) |

|

| 圖3 本文範例方案的輸入和輸出雜訊 |

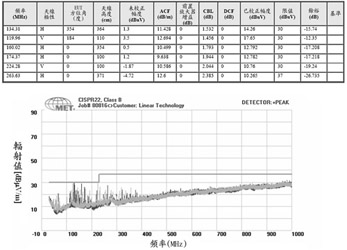

經過最佳化的SiP設計除可降低輸入與輸出雜訊外,也可抑制輻射型態的雜訊。凌力爾特在一個10公尺大小的微波暗室(圖4)中完成輻射掃描測試。為了確保低基線輻射雜訊,採用一個用於輸入的線性DC電源,並在輸出端上布設了一個阻性負載。基線雜訊利用負責直接向阻性負載提供一個直流電流的電源來檢查。

|

| 圖4 在微波暗室中所進行的測試配置 |

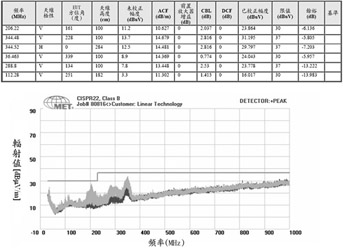

本文範例方案在接受測試時安裝在一個標準展示板上。圖5顯示了峰值掃描結果。這些結果顯示,該元件在CISPR 22(准峰值)輻射限值B級之下有超過 12dBuV的餘裕(Margin)。圖6顯示另一款本文範例方案從24伏特輸入到12伏特/5安培輸出的掃描結果。

|

| 圖5 從 12Vin 到 2.5Vout/6A 低雜訊 LTM4606 模組的峰值掃描結果 |

|

| 圖6 從 24Vin至 12Vout/5A 低雜訊 LTM4612 模組的峰值掃描結果 |

SiP化方案可兼顧易用性與雜訊性能

在現場可編程閘陣列(FPGA)和特定應用積體電路(ASIC)中向輸入/輸出(I/O)線路供電時,線性穩壓器仍是可行和簡單的解決方案,但隨著這類元件紛紛內建傳輸速率高達8Gbit/s,甚至10Gbit/s的串列/解串列(SERDES)收發器,線性穩壓器勢必提供比過去更大的功率。在提供高輸出功率時,線性穩壓器耗散更多熱量。熱耗散增加的結果是元件變得更熱,導致熱量管理方案不是變得更昂貴、更具挑戰性,就是讓解決方案變得不切實際。

另外,由於線性穩壓器的電源抑制比(PSRR)在100kHz以上將大幅降低,因此線性穩壓器對濾除高頻切換穩壓器(500kHz以上)的雜訊就變得無效。由於這個原因,會給線性穩壓器電路增加鐵氧體磁珠和高頻雜訊。

一個仔細設計的切換穩壓器解決方案(諸如新的低雜訊微型模組穩壓器系列),不僅能以相當於線性穩壓器一小部分的熱損來提供同樣的輸出功率,而且能以非常低的雜訊提供功率,因此它能夠用於FPGA或ASIC系統中的高速收發器。

為了測試DC-DC微型模組穩壓器的相容性,賽靈思(Xilinx)在其實驗室裡運用6.25Gbit/s線路速率和PRBS-15資料圖形,對包括本文範例在內的不同電源解決方案進行測試。該測試的目的是透過測量發送器上的抖動發生和接收器上的抖動容限(當採用一個DC-DC微型模組穩壓器來給電路供電時)來評價收發器的性能。測試了一系列不同的DC-DC微型模組穩壓器。對每個穩壓器都根據已定義的輸入和輸出電壓以及輸出功率能力做出了具體規定。然後,每個DC-DC微型模組的測試結果都與賽靈思先前所使用的低雜訊線性穩壓器LTC3026進行比較。

用這個超低雜訊DC-DC穩壓器系列來降低雜訊已經顯示出非常好的結果。現在,這些結果必須透過幾次測試轉換到數位域。以如前所述的賽靈思測試設置為基礎,可以得出幾個結論。

|

|

| |

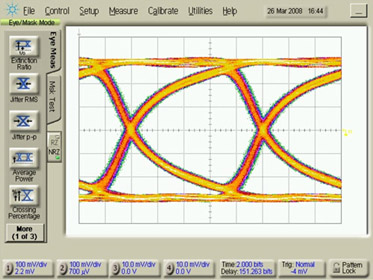

用來測量收發器眼圖張開度的眼圖掃描顯示了良好的品質。如圖7a所示,眼圖張開度保證這個DC-DC微型模組穩壓器系列提供大電流(能提供高達6A的電流)而不會降低眼圖的品質。

|

| 圖7a 眼圖掃描顯示採用新的超低雜訊微型模組穩壓器所引入的失真可被忽略 |

|

|

|

| |

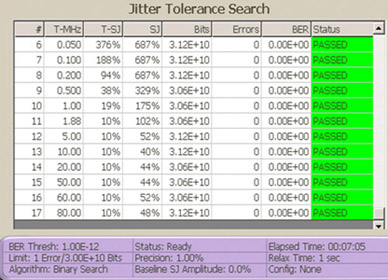

收發器的性能取決於發送器上的抖動發生和接收器上的抖動容限。包含本文範例方案在內的四款方案皆顯示出與線性穩壓器不相上下(在某些場合中甚至更好)的性能值。換句話說,微型模組對抖動的影響是可以忽略的。表1提供了一個總結。另外,圖7b是在線路板上進行抖動測試的結果。

| 表1 賽靈思所進行的DC/DC方案性能測試比較結果 |

| 元件 \ 性能 |

電源纹波(mVpp) |

TJ(ps) |

抖動容限(UI)

20MHz |

抖動容限(UI)

80MHz |

眼圖掃苗(UI)

6CH(平均) |

| 1.0V |

1.2V |

| LDO(LTC3026) |

7.0 |

3.0 |

58.3 |

0.44 |

0.53 |

0.44 |

| LTM8023(2A) |

6.4 |

1.8 |

57.6 |

0.44 |

0.46 |

0.44 |

| LTM4604(4A) |

7.1 |

1.8 |

57.0 |

0.47 |

0.47 |

0.44 |

| LTM4606(6A) |

6.2 |

3.9 |

57.5 |

0.44 |

0.48 |

0.44 |

| LTM4616(2×8A) |

6.2 |

1.9 |

57.0 |

0.41 |

0.47 |

0.44 |

|

|

| 圖7b 本文範例方案經賽靈思抖動容限測試後的結果 |

|

|

| |

此外,就高速I/O電源而言,系統設計師測量的指標還有電源紋波。更合意的是較低的紋波。還是在表2中,顯示了每個DC-DC 微型模組在1.0V和1.2V時的輸出紋波。與線性穩壓器(LDO)相比,結果是可比較,並且有時更好(圖2中顯示)。 |

簡單易用/雜訊抑制優勢 SiP嶄露頭角

從本文介紹可知,DC-DC微型模組穩壓器系列已證實可適用於在高速資料傳送對EMI和/或碼錯誤率(BER)敏感的電子系統。這些微型模組穩壓器提供了超低雜訊性能和高效率、精小封裝和類似於使用線性穩壓器的簡單設計,可讓設計工程師在堅固雜訊抑制效能的前提下,更輕鬆完成設計。

(本文作者任職於凌力爾特)

| 註: |

| 兩款方案的輸入電壓均為5伏特、輸出電壓與電流均為1.2伏特與5安培;輸入電容部分,兩款方案均採用3x10μF/25V陶瓷和1x150μF/25V電解電容;輸出電容則同為1枚100μF/6.3V和3枚22μF/25V陶瓷電容;量測示波器的頻寬為300MHz。 |