目前的視訊監視市場在發展過程中遇到包括從類比到數位攝影機的過渡、轉換到高畫質視訊、應用WDR感測器,以及實現進行資料傳輸和控制的IP連結等技術難題要解。透過導入FPGA元件,IP監視攝影機將可以低成本建構完整的智慧監控系統。

在視訊監視產品朝向更高品質視訊、高解析度以及靈活性和功能的趨勢推動下,數位攝影機正快速取代類比攝影機成為市場主流。由於高畫質(HD)視訊必須是數位,因此,採用HD標準也就意味著數位感測器所扮演的角色將更加吃重,尤其是此一標準支援更高的畫面播放速率和解析度,將需要如H.264之類的新壓縮技術,促使攝影機能具有更強的影像處理能力。

在強光、暗光和高對比度等各種照明條件下,數位攝影機都要能提取出所有影像內容,因此,數位攝影機採用了新一類寬動態(WDR)感測器,並要求在數位領域中實現動態範圍壓縮。此外,數位攝影機中另一優點是可以在攝影機內部進行「智慧分析」處理,這也是過去類比攝影機無法實現的功能。

搭橋HD WDR感測器與ISP 高效能FPGA元件大展身手

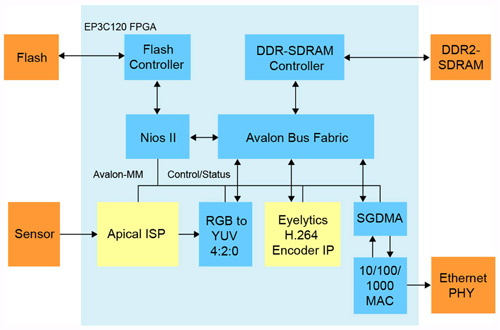

如圖1所示,此為IP監視攝影機參考設計的頂層結構圖和硬體,並包含專為新一代HD WDR感測器效能所需而建構的現場可編程閘陣列(FPGA)元件,此IP監視攝影機參考設計結合了Altera以及多家合作夥伴的硬體和軟體矽智財(IP)。

|

| 圖1 監視攝影機參考設計結構圖 |

|

| 圖2 IP監視攝影機參考設計硬體 |

圖2為參考設計的硬體平台,本文以Cyclone III EP3C120開發板為例。Aptina WDR感測器圖像資料被送入Apical的影像感測器管線。輸出資料是YUV 4:2:0格式,寫入到外部DDR2 SDRAM的圖幀緩衝中,並導入FPGA元件,然後使用EyeLytics提供的核心,以H.264格式對視訊資料進行編碼,支援三級基線/主要類視訊串流,透過乙太網路在遠端主機上觀看。

分散收集直接記憶體存取(SGDMA)控制器支援Altera三速乙太網路(TSE)MegaCore功能,將編碼後的視訊串流透過乙太網路直接傳送到遠端用戶端。

Aptina MT9M033是720p WDR互補式金屬氧化物半導體(CMOS)感測器,主要用於監視攝影機市場。感測器和鏡頭組合安裝在「頂板」上,透過I/O轉換板將其連接至Cyclone III EP3C120開發板。由於CMOS WDR感測器沒有晶片內影像管線處理功能,因此以RAW/Bayer格式輸出影像資料,每圖元為20位元,並可以採用下列公式1計算感測器輸出的大量原始資料。

20位元/圖元×(1280×720)圖元/幀×60幀/s=>1Gbit/s ................公式1

由於高畫質影像訊號將帶來過大的資料量,很難將新一代WDR感測器連接至監視解決方案中經常使用的特定應用標準產品(ASSP),因此,透過FPGA元件是高效率處理資料的理想選擇。

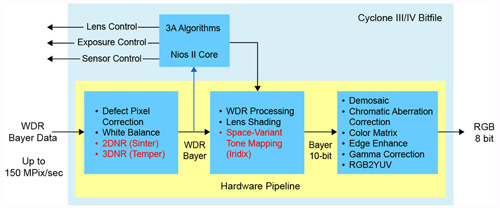

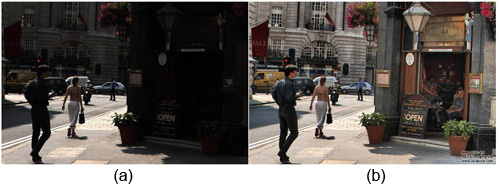

如圖3所示,Apical的影像訊號處理器(ISP)包括去除熱點圖元、抑制雜訊、使用Apical專利Iridix IP核心實現單位圖元高階色調映射功能與高階去馬賽克和顏色校正等功能,與圖4a未處理的圖像相比,圖4b顯示了Iridix核心如何從高對比度場景中盡可能多的提取出細節內容,尤其是較暗的區域並沒有受到較亮區域過度感光的影響。ISP輸出可做為參考設計的一個選項,透過Bitec DVI輸出電路板連接至Cyclone EP3C120開發板的第二個HSMC連接器。

|

| 圖3 Apical ISP結構圖 |

|

| 圖4 Apical ISP高對比度場景效應,(a)為未處理圖像;(b)為經過ISP處理的圖像。 |

加速色度採樣與編碼轉換 視訊影像處理器立大功

Altera視訊影像處理(VIP)套件整合了MegaCore功能,設計人員可利用它便捷的開發訂製視訊和影像處理設計,加速系統設計時程。VIP套件含有MegaCore功能,從顏色空間轉換等簡單的建構模組功能,到可程式設計多相縮放等複雜的視訊縮放功能。這些功能適合用在多種影像處理和顯示應用中,例如視訊監視、廣播、視訊會議、醫療以及軍事等。

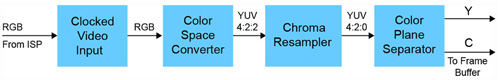

在IP監視攝影機參考設計中,採用了多種VIP核心進行顏色空間轉換,採用色度重新採樣功能將ISP的RGB編碼視訊轉換為H.264編碼器要求的YUV 4:2:0編碼輸入。如圖5所示,核心連接至應用了Avalon-ST視訊通訊協定的Avalon串流(Avalon-ST)介面。使用Avalon記憶體映射(Avalon-MM)介面,Y和C視訊分量被寫入外部DDR2記憶體的圖幀緩衝。

|

| 圖5 處理過的感測器影像轉換和重新採樣流程。 |

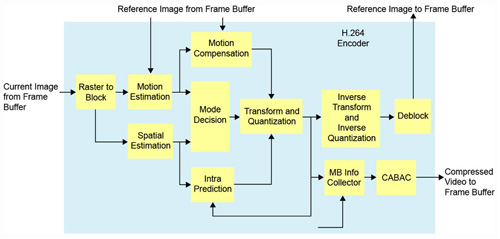

在H.264編碼之前,跳過視訊間隔圖幀,在圖幀緩衝寫入器中,720p60感測器畫面播放速率被轉換為720p30,而不是將其寫入圖幀緩衝中。如圖6所示,此為H.264編碼器架構,採用EyeLytics提供的IP核心,它針對監視應用進行了最佳化。這一個核心具有很多監視功能,包括多通道支援、恆定品質速率控制、幀內/幀間模式、QPEL、前後關係自我調整二進位演算法編碼(CABAC)/前後關係自我調整長度可變編碼(CAVLC),並使用較少的邏輯閘,且核心同時支援主要類和基線類。

|

| 圖6 H.264編碼器架構 |

IP攝影機設備商若採用FPGA元件,其產品架構可非常靈活,且完全能在工程師都了解的標準硬體平台上實現功能。透過此一靈活性,可增強和修改攝影機系統的架構,以適應不同的系統需求。由於採用了標準HDL來實現設計,因此,很容易提高攝影機解析度,增加訂製視訊處理功能或者視訊分析引擎,且還可透過乙太網路進行遠端更新。例如,把新的FPGA程式設計檔案發送至Nios II嵌入式處理器,然後將檔案寫入快閃記憶體,進而重新配置系統或者改變感測器和ISP設置。

高整合度FPGA不僅可減少IP監視攝影機參考設計的晶片數量,還可節省PCB空間,且不需要與外部元件進行通訊,進而減少了I/O連結,降低動態功率消耗、解決散熱問題。針對客製化需求,則可使用不同的FPGA映像檔(如解析度、畫面播放速率和壓縮選項),在一個系統設計中便能夠支援多種客製化攝影機。透過縱向移植,可以在同一個封裝中使用不同邏輯密度的元件。此外,採用開放設計方案讓設計人員能夠針對最新的FPGA進行設計,有了更新的FPGA系列後,可以進一步提高性能,降低成本和功率消耗。

低成本、高效能的FPGA解決了目前IP監視系統設計人員所面臨的技術難題。監視器設備商透過FPGA晶片供應商及其合作夥伴提供從影像採集到IP封裝的全面解決方案,並使用整合各種功能的元件,即可輕鬆加速產品上市時程,且實現清晰銳利的高解析度監控影像。

(本文作者皆任職於Altera)