隨著市場對行動裝置的功能需求持續成長,對半導體封裝解決方案的需求亦隨著水漲船高,而理想的解決方案必須滿足在效能、微型以及降低成本等方面日趨複雜的需求。覆晶封裝則被視為最能符合以上需求的關鍵解決方案,並可望提升行動裝置之效能。

若以手機出貨量比重來看,智慧型手機無疑是成長最快速的市場,其在2009年的市占率高達15%,而2013年的比重更將成長至35%。事實上,在未來4年,所有手機的銷售力道都將來自智慧型手機。此外,在電腦產品方面亦呈現類似的現象,幾乎所有成長動能都由筆記型電腦(NB)與小筆電(Netbook)而來,桌上型電腦的銷售量則持續下滑。

行動裝置推升覆晶封裝需求

許多因素帶動市場對覆晶封裝(Flip Chip Packaging)的需求,其中有許多和要求更高的輸入/輸出(I/O)介面有直接關連。由於諸如網路、全球衛星定位系統(GPS)、MP3、加速度計、觸控螢幕等越來越多功能被加入手機中,基頻(Basband)與應用處理器的I/O數量也隨之增加。此外,記憶體控制器整合至CPU後,也會增加這些元件的I/O作業數量。多核心中央處理器(CPU)與多通道記憶體,亦進一步推動這股趨勢。高畫質(HD)影片則讓包括智慧型手機、小筆電、遊戲機等產品增加對繪圖處理器的需求,而這向來都屬於高I/O需求的裝置。

於此同時,全球的局勢轉變亦助長了覆晶封裝的發展。首先,引線搭接元件使用的黃金原料成本不斷攀升,使覆晶成為比引線搭接更經濟的封裝技術。其次,新型覆晶基板的產能持續開出,有效紓解供應鏈的瓶頸。

覆晶互連技術有待突破

然而,覆晶互連的成長,卻也突顯出許多技術問題。舉例來說,更高的I/O數就導致系統必須減少凸塊間距。但在低於180奈米的間距下,要控制封裝基板銲墊的焊料量,不僅難度極高而且會導致基板與覆晶組裝良率下滑。而若晶片與封裝上的銲墊尺寸縮小至更緊密的間距,將會產生電流推擠(Current Crowding)現象,使得電致遷移效應(Electro-migration)的風險也會提高。在微間距環境中使用無鉛焊料時,若焊點崩潰,不僅會導致應力增加,還會降低熱循環的可靠度,讓充填底膠製程更具挑戰性。

另一種新方法是在晶片上使用銅柱來取代焊錫凸塊,但這種製程成本昂貴,且銅柱結構會增加脆弱的低介電係數材料層破裂的風險。不巧的是,現今許多高效能半導體元件都採用這種材料。

新型態基板有助克服可靠度挑戰

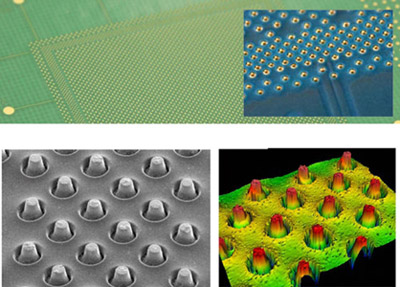

解決這些問題的其中一項方法就是在晶片銲墊上採用傳統的無鉛焊錫凸塊,以及在基板上使用銅柱接觸點。如PILR基板(圖1)可帶來擁有眾多優點的高可靠度結構。由於銅柱是由蝕刻所製成,故此製程能延伸至極細的間距,讓接點具備極佳的共面性。

|

| 圖1 PILR覆晶基板具有高共面性的細間距銅柱,從厚度極均勻的銅片進行蝕刻所製成 |

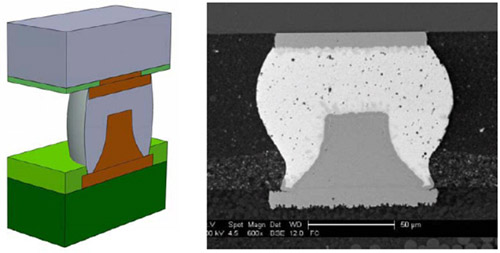

圖2的結構,去除了基板銲墊上問題重重的焊錫,並提供厚度可預測的充填底膠,甚至加上了一旦沒有支撐物即會崩解的無鉛銲錫。由於基板銅柱提供一個垂直的潤溼表面,能在極小的間距下進行均勻的蝕刻,因此晶片上銲墊的間距縮減就不必透過縮小銲墊尺寸,以避免短路的方式來達成,可有效降低電流推擠以及電致遷移效應的發生機率。

|

| 圖2 PILR在基板上的覆晶銅柱,運用充填底膠製程,並在低介電係數介電層上提供比晶片銅柱更低的應力 |

基於過去的經驗,業界為因應各種變化的需求,將陸續採用新的封裝技術。在需求由消費性行動應用所帶動的現在,解決方案必須支援高接腳數、微型化、簡化組裝流程等需求,並在行動環境提供可靠的性能。新型解決方案如PILR這類基板覆晶的銅柱結構,不但能有效滿足市場需求,更具備許多不同的特長與優點。若能有效運用,必能為行動運算帶來新的前景。

(本文作者為Tessera台灣區總經理暨東亞區總監)