2022年1月PCIe 6.0問世,其轉為PAM4架構雖可實現更高的傳輸速率,卻也為產品設計帶來新的挑戰。為加快PCIe 6.0產品上市步伐,量測業者、IP業者紛紛祭出相關解決方案,盼能儘早攻克PAM4難題。

主導PCI標準制定的PCI-SIG組織,在2022年1月發表了PCIe 6.0規格,正式完成了PCIe 6.0的標準化作業。在標準釋出後,業者無不摩拳擦掌地準備搶占這個新興市場,然而為了實現更高的頻寬,和過往標準不同,PCIe 6.0揮別了NRZ,全面改用四階脈衝振幅調變(PAM4)的編碼方式,而這也為產品開發帶來全新的挑戰。

改為PAM4提升速率又降低通道損耗

PCI-SIG表示,PAM4訊號使數據速率加倍,但同時又使用與NRZ相同的奈奎斯特頻率(Nyquist Frequency),如此一來可以提升速率但又能減少通道損耗。舉例來說,PCIe 5.0架構使用16GHz的奈奎斯特頻率;而使用PAM4的PCIe 6.0架構同樣也採用16GHz奈奎斯特頻率,但數據速率卻翻倍至64GT/s,且透過x16配置可提供高達256GB/s的雙向頻寬。

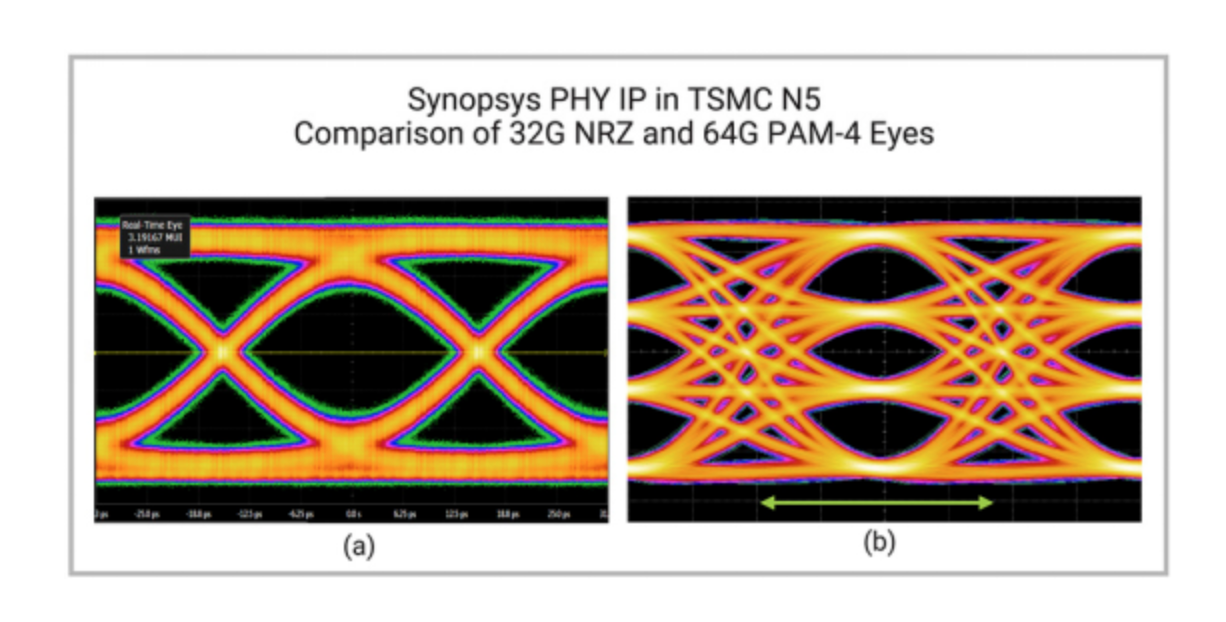

而根據新思科技於電子發燒友網發表的文章解釋,當數據速率從16GT/s加倍到32GT/s時,奈奎斯特頻率也從8GHz加倍到16GHz,使得PCIe 5.0的頻率相關損耗比PCIe 4.0嚴重得多。再加上電容耦合(噪聲和串擾)的增加,使得PCIe 5.0通道成為最難處理的NRZ通道。如果PCIe 6.0仍然保留NRZ訊號,則奈奎斯特頻率將增加到32GHz,通道損耗大於60dB,這對於實際系統而言太大了,因此需要從NRZ更改為PAM4訊號。這一變化意味著發射和接收的訊號現在有四個不同的電壓電平,而不是兩個(如圖1)。

圖1 PCIe 6.0採用PAM4架構,眼圖也轉為三個 圖片來源:新思科技

圖1 PCIe 6.0採用PAM4架構,眼圖也轉為三個 圖片來源:新思科技

文章進一步提到,圖1(a)顯示了使用NRZ訊號的PCIe 5.0眼圖,包含兩個電壓電平和單眼,圖(b)則顯示了使用PAM4訊號的PCIe 6.0眼圖(包含四個電壓電平和三眼)。圖1中的兩個訊號具有相同的16GHz奈奎斯特頻率和相同的單位間隔(UI),這意味著它們基本上可以使用相同的PCIe 5.0通道,而不會讓頻率相關損耗變得更糟糕,如果使用64GT/s的NRZ訊號,奈奎斯特頻率為32GHz。

這也是56G和112G乙太網轉換到PAM4訊號的原因,也是PCIe 6.0現在轉換到PAM4的因素,可以降低訊號損耗,但是PAM4四個電壓電平在一個UI中使用2bit編碼,而NRZ是1bit編碼,因而使數據速率提高了一倍。值得一提的是,為了降低誤碼率,PCIe 6.0還導入了向前糾錯機制(FEC),以降低PAM4訊號在傳輸過程中出現訊號錯誤的頻率,確保訊號完整度。另外,PCIe 6.0也加入流量控制單元(FLIT)技術改善訊號延遲情況,以在大資料量高速傳輸時可以更穩定。

業者紛紛出招克服PAM4挑戰

PCIe 6.0雖然可帶來更快速的傳輸體驗,但改為PAM4後卻也為生產、研發部門帶來新的挑戰。是德科技技術部門技術專案經理劉宗琪表示(圖2右),PCIe 6.0最大的轉變就是從NRZ變成PAM4。NRZ原先是用0、1兩個電平來形成一個眼圖,而PAM4會有0、1、2、3共四個電平,以形成三個眼圖。

劉宗琪進一步說明,由於PAM4有著三個眼圖,與原先NRZ一個眼圖相比,PAM4的眼寬和眼高明顯縮小,這也意味著PAM4在訊號傳輸過程中對於雜訊(Noise)更敏感,這使得確保PCIe 6.0訊號完整性挑戰更大,因為對於訊噪比的要求更高。也因此,相較於PCIe 5.0,PCIe 6.0還需進行訊噪比和失真比(SNDR)等新的量測。

因應此一情況,是德科技備有M8040A高效能BERT,可提供高達64 Gbaud的純淨NRZ和PAM4訊號,以及快速轉換和低固有抖動等特性,並提出遠端頭端的概念,並使用長度僅1.85mm的纜線,以提供接近於待測裝置的效能,並將損耗過大的通道造成的訊號衰減降到最低;協助研發、測試工程師分析晶片、元件、收發器模組和子元件、電路板及系統的特性。

不僅如此,由於PCIe 6.0的眼圖高度從原本PCIe 5.0的15mV縮小到只有6mV,為了能更準確量測眼圖高度,對於示波器的雜訊效能要求也更高。是德科技行銷處資深專案經理吳哲樂表示(圖2左),PCIe6.0眼高變得更低,若是示波器雜訊效能不佳,訊號很容易就會被儀器本身的雜訊蓋過,那麼測量到的訊號完整性一定非常差。

圖2 右為是德科技技術部門技術專案經理劉宗琪,左為是德科技行銷處資深專案經理吳哲樂

圖2 右為是德科技技術部門技術專案經理劉宗琪,左為是德科技行銷處資深專案經理吳哲樂

吳哲樂指出,所以在這樣的情況下,示波器的底噪一定要非常好,不能讓雜訊高過眼圖的高度,否則在訊號完整性的測試上,一定會呈現Fail。為此,是德科技也備有Infiniium UXR系列示波器,其特色包括具有5~110GHz頻寬,且本底噪聲更低,在110GHz 的垂直噪聲不到1mVrms,確保測量更準確。

與此同時,另一量測大廠太克科技也針對PCIe 6.0推出全新解決方案,包括PCIe 6.0(64G T/s)自動基本發射器解決方案,PAMJET應用程式以及專為PCIe 6.0開發的SNDR、RLM、不相關抖動和脈衝寬度抖動量測功能。而為了提高量測結果的準確性,太克亦針對儀器量身打造出雜訊補償功能,且自動基本發射器可以在頻寬50GHz及以上的Tektronix DPO70000SX系列即時示波器上執行,PAMJET應用程式則可增強PAM4 DSP功能。

太克東南亞/台灣行銷經理陳川迅表示,從PCIe 5.0遷移到PCIe 6.0遭逢了挑戰,因為從NRZ過渡到PAM4,後者對通道中的串擾(Crosstalk)更加敏感。為此,太克開發新的測量方法和儀器噪聲補償技術,以確保在電氣驗證和驗證階段準確識別本質上較小的運行裕度。

新思科技資深產品市場經理張小林則指出,PAM4的確是目前PCIe 6.0產品開發的主要挑戰。如同前面所述,更改為四個電平訊號會導致訊噪比損失9.6dB,因此需要更注重雜訊管理,串擾、誤碼率提升等挑戰,而這也會影響封裝和電路板設計。

為了協助產業加快PCIe 6.0產品開發進度,新思發表全新IP解決方案,除了支援PCIe 6.0相關規範外,其最大改變在於,為了實現最低延遲並盡可能提高所有傳輸規模的吞吐量,該方案的DesignWare控制器採用MultiStream架構,可提供相當於傳統Single-Stream設計兩倍的性能。不僅如此,新推出的DesignWare PHY IP還可提供獨特的自適應DSP算法,可在晶片對晶片、轉接卡和背板接口上節省20%功耗,以大幅提高功耗效率,而不受通道影響。

張小林解釋,為了協助客戶開發,新思的PCIe 6.0解決方案重新調整了架構,也就是改為使用MultiStream,同時再加上獨特模擬和DSP演算法,以降低通道變化的影響、封裝串擾等。

總之,隨著AI、資料中心及高效能運算(HPC)等新興應用不斷成長,導致資料量大增,為滿足市場需求,PCIe規格也持續進化, 朝著每三年傳輸速度翻倍的目標邁進;而在PCIe 6.0規格問世後,量測、IP業者也積極布局,期能儘早克服PAM4架構挑戰,推動相關產品儘早問世。