人工智慧/機器學習(AI/ML)走進各式應用,帶來高速低延遲的資料傳輸需求。PCIe 5.0標準自2019年發布後,經過四年多的時間,現在已可陸續看到相關產品上市。本文旨在介紹PCIe 5.0的裝置市場現況,並說明產品設計須要注意的重點。

從社群媒體到自動駕駛汽車和家用電器,人工智慧(AI)和機器學習(ML)運算在日常生活中的應用更加廣泛,目前AI/ML市場已達1,000億美元,並預計在2030年之前成長20倍達到2兆美元,而推動此龐大市場的技術,便是促進高頻寬和低延遲資料傳輸通道的PCI Express(PCIe)5.0架構。

PCIe 5.0架構有哪些新功能?

PCIe 5.0於2019年5月發布,提供前版PCIe 4.0兩倍的資料傳輸能量。這使得圖形適配器卡、網路介面卡(NIC)、儲存加速器裝置、固態硬碟(SSD),甚至是圖形處理單元(GPU)等PCIe周邊裝置能夠擁有更優秀的性能表現。

在了解PCIe 5.0對ML和AI應用如此關鍵的原因之前,首先得知道下一代技術應用的要求:

- 需要能連接上多數運算晶片和網路裝置。這種通用性也是PCIe等廣泛互連協定經常用於實現加速器解決方案的原因。

- 標準軟體和常用程式設計模型,方便裝置發現、程式設計和管理。

- 軟體必須易於開發。獲得廣泛採用的PCIe使所有裝置幾乎都可以立即部署。

除此之外,PCIe 5.0也可透過低延遲、非歸零的實體層承載更多協定,讓CPU能夠跟上隨著AI和ML裝置高速成長而急遽增加的資料量。

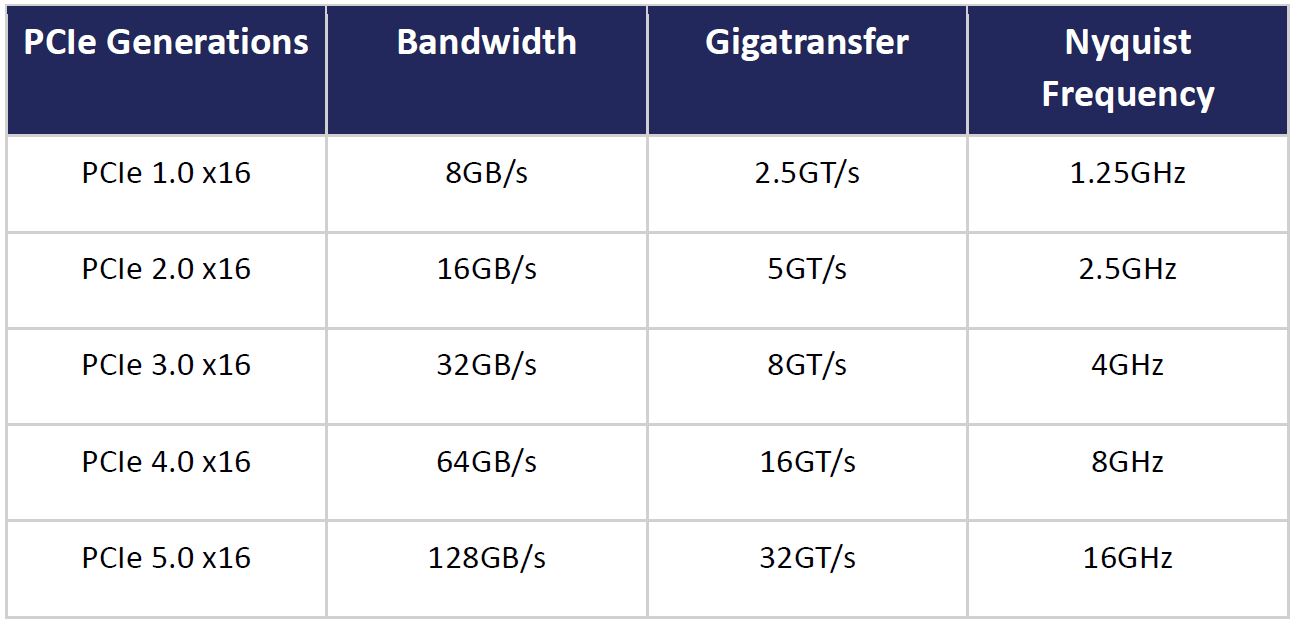

PCIe 5.0能支援多快的資料傳輸?目前,多數處理器和主機板皆支援PCIe 4.0。該標準在2017年首次發布時具有劃時代的意義。然而,許多用戶開始遇到性能瓶頸。例如,採用M.2 NVMe外型的固態硬碟只能在四條通道(Lane)上實現8GB/s的持續資料傳輸,而PCIe 5.0 SSD的速度則翻了一番,達到16GB/s,32通道裝置的頻寬為128GB/s(表1)。

表1 PCIe前五代標準傳輸速度比較

表1 PCIe前五代標準傳輸速度比較

截至本文撰寫時,觀察市場相關元件產品,AMD的AM5和Intel的LGA 1700主機板等產品已經開始支援PCIe 5.0,預計在近期將有更多新產品推出。需要注意的是,只有在連線的兩端都支援PCIe 5.0的情況下,才能實現更高的資料傳輸速度。理論上來說,與PCIe Gen 4主機板配對的PCIe 5.0 SSD能夠以最大Gen 4頻寬(16GT/s)運作。因此,能夠在x16鏈路寬度上以64GB/s的速度傳輸資料。

PCIe 5.0如何影響裝置開發?

不可否認的是,PCIe 5.0是開發更快裝置的必要條件。然而,其存在本身並無法提高GPU或SSD的效能,對於已經有足夠頻寬的裝置來說尤其如此。事實上,儘管PCIe 5.0標準已發布四年,目前在市場上流通的PCIe 5.0裝置仍並不多。(編按:本文原發表於2023年12月)

不過,PCIe 5.0肯定會在加快循序(Sequential)讀寫速度以提高傳輸速度等方面發揮關鍵作用,尤其是在需要傳輸較大文件的應用情況中。Crucial T700和SEAgate FireCuda 540等Gen 5固態硬碟已經比Gen 4固態硬碟有了顯著的改進。PCIe Gen 5固態硬碟開始浮出水面,不過在PCIe 5.0真正成為主流之前,還需要有更多經濟實惠的元件。

成本是升級至PCIe 5.0的主要障礙。在大多數情況下,主機板、CPU甚至是記憶體都需要經過升級,才能相容於PCIe 5.0裝置。不同的主機板對PCIe 5.0的支援程度也有所差異,因此使用者更難以判斷是否值得投資相關成本進行升級。

此外,市面上較新的PCIe Gen 5固態硬碟需要散熱片,甚至是像Corsair MP700 Pro固態硬碟的主動冷卻解決方案。儘管散熱片並非必要選項,其對於硬體維護來說還是不可忽略的重要考慮因素。

PCIe 5.0設計挑戰

通道插入損耗(Insertion Loss, IL)造成的訊號衰減,是PCIe 5.0技術系統設計的最大挑戰。為此,PCIe 5.0選擇沿用非歸零(NRZ)訊號方案,而非轉而採用PAM4。PAM4常用於速度超過30GT/s的資料傳輸標準,有助將訊號的奈奎斯特頻率(Nyquist Frequency)降低至資料速率的四分之一,代價是9.5dB的訊號雜訊比(SNR)。PCIe 5.0不選擇PAM4,而是繼續使用NRZ訊號方案,代表訊號的奈奎斯特頻率為資料速率的二分之一。

PCIe 5.0於規範中列有上述挑戰的應對方針,對訊號在傳輸過程中可削弱的程度設定限制(32GT/s時為36dB),並且誤碼率(BER)須小於10~12。為了解決訊號減弱或衰減問題,PCIe 5.0對參考接收器進行定義,以確保連續時間線性均衡器(CTLE)模型包括一個-15dB的ADC(可調直流增益),而16GT/s的參考接收器僅設定為-12dB。

當資料傳輸速率達到32GT/s,誤差頻率會越來越高,而DFE電路在接收器的整體平衡中,扮演著至關重要的角色。PCIe 5.0架構中的預編碼(Precoding)有助於消除此風險。在發送端啟用預編碼,在接收端進行解碼,將大大降低突發錯誤的風險,並保障PCIe 5.0規範32 GT/s連結的穩健性。

PCIe 4.0和PCIe 5.0架構的插入損耗預算分別為16GT/s和32GT/s。扣除CPU封裝的9dB後,剩餘的預算分別為AIC的9.5dB、CEM連接器的1.5dB 和系統基板的16dB。

除了插入損耗預算,工程師在設計PCIe 5.0時還需要考慮以下因素:

- PCB線路的插入損耗將隨著溫度升高而增加。

- 印刷電路板製造過程中的異變將為插入損耗帶來影響,特別是在線寬不一致的情況下。

- 由於反射、串擾(Crosstalk)和電源雜訊都會導致SNR退化,必須為接收器留出額外的插入損耗餘裕。

在正常的情況下,硬體工程師和系統設計師會留出大約10~20%的整體通道插入損耗預算,即36dB預算中約4~7dB。隨著AI和ML需求增加,預計將出現更多的系統拓撲。因此,工程師必須熟悉PCB材料和PCIe 5.0重計時器(Retimer),以確保順利升級至PCIe 5.0架構。

具備PCIe測試經驗的實驗室有助產品開發,例如Granite River Labs(GRL)便可幫助業者掌握AI和ML趨勢下的產品設計技巧,確保產品能夠持續革新,以滿足變化中的市場需求。

(本文作者任職於Granite River Labs)