通用序列匯流排(USB)規格的最新世代版本USB 3.1第2代有望改變IT、消費性、工業及通用嵌入式電子設備交換資料和供電的方式。再加上Type-C連接器,它就能代替許多其它形式的有線連接,而且它已經在攜帶式消費裝置領域呈現迅速增長的趨勢。這可能與該規格的供電(PD)方面最為相關。隨著Type-C連接器用於更多設備,使用者對供電潛能的意識也將增加。

短期內,預計USB-PD將在離線電源配接器中得以實施,且最有可能用於高階筆記型電腦,這也符合提供更高電源轉換能效的趨勢。預計至2020年,約半數筆記型電腦配接器都將採用USB-PD。製造商還希望能將電器的電源配接器最佳化,這可能意味著輸出功率在27~100W之間,也將影響設計。因此若製造商要生產各種不同輸出功率水準的配接器,能夠提供設計靈活性的單一方案將成為首選。

電源轉換挑戰

從交流(AC)轉到直流(DC)涉及到轉換,且不可避免地會造成相關損耗,半導體產業一直在努力減少這樣的損耗。當前存在許多電源轉換拓撲結構,一般而言,當將成本視為主要問題且能效並不太重要時,可採用一次側穩壓(Primary Side Regulation)返馳拓撲結構,特別是當輸出功率要求較低且無需嚴格的輸出電壓穩壓時。當需要更高輸出功率時,為獲得更高的能效和更佳的性能,通常首選二次側穩壓(Secondary Side Regulation)準共振(Quasi-Resonant)返馳拓撲結構。

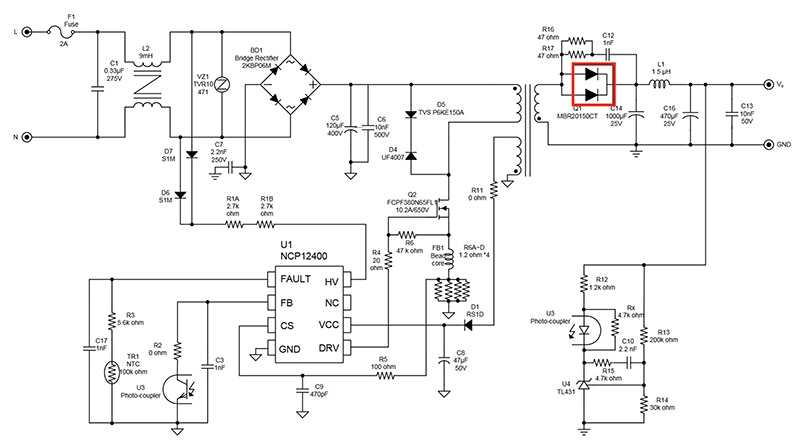

在主電源變壓器之後進行的此形式的輸出整流,一直用二極體作為開關(圖1),然而這也有能效問題,主要是由於在二極體的PN結上經歷了正向壓降。這通常約為0.7V,儘管通常採用肖特基二極體(Schottky Diode)可將壓降降至更接近0.3V,但這仍是損耗。

圖1 二次側採用二極體整流的經典返馳式固定輸出電壓電源轉換方案。

圖1 二次側採用二極體整流的經典返馳式固定輸出電壓電源轉換方案。

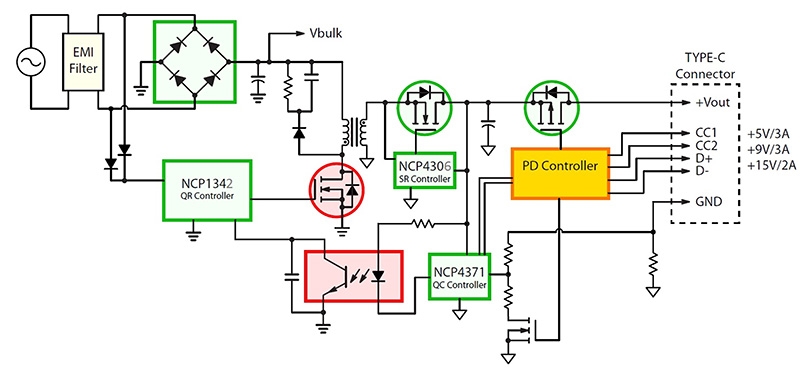

現代高功率密度USB-PD配接器如今透過採用低導通電阻MOSFET來避免二極體相關損耗(圖2)。

圖2 基於使用MOSFET作為輸出開關的二次側同步整流的USB-PD電源配接器。

圖2 基於使用MOSFET作為輸出開關的二次側同步整流的USB-PD電源配接器。

雖然這提供了能效增益,但複雜性也隨之增加。使用電晶體而非二極體的做法稱為二次側同步整流,為了從這種拓撲結構中獲益,設計人員需要加上一個控制器,在正確的時間導通和關斷電晶體。更複雜的是,各種同步整流(SR)控制器都可用,可基於應用程式提供不同的特性與優勢。

SR控制器設計最關鍵 打造優質USB-PD

相較於採用肖特基二極體,使用一個低RDS(on)(約5至10mΩ)MOSFET也能顯著提高二次側輸出整流的能效,從而有望實現高於93%的峰值能效。

MOSFET的開關時序現已成為關鍵參數,導通和關斷延遲會直接影響整體能效。由於控制器決定了MOSFET的狀態,因此在選擇合適的控制器時,由控制器引起的切換延遲時間就成為了需要考量的關鍵參數。

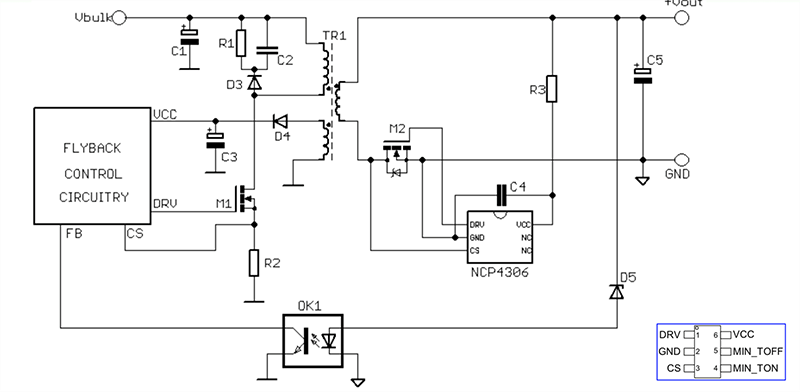

在USB-PD應用中,返馳式電源通常設計為以連續導通模式(Continuous Conduction Mode)或準共振(Quasi-Resonant)模式工作。在CCM中,SR控制器需要非常快速地關斷MOSFET,以避免在一次側造成任何擊穿,有效地在一次側和二次側之間建立直接通路,這會導致功率MOSFET可能出現非常高的瞬時電流。圖3顯示了典型的電路配置,其中M1位於一次側,M2(同步整流MOSFET)位於二次側。

圖3 開關模式電源示例,顯示了一次和二次側電晶體。

圖3 開關模式電源示例,顯示了一次和二次側電晶體。

在此配置中,必須在M1導通之前快速關斷M2。為滿足100W的USB-PD規格,所選的同步整流MOSFET需要具有足夠低的導通狀態電阻,以應對所需輸出電壓需要的電流水準,還要做到最低程度的熱損耗,以避免內部配接器溫度升至過高水準,這反過來又受到控制器降低電流以確保MOSFET能夠在最短時間內關斷能力的影響。

要確定何時關斷MOSFET,涉及到測量裝置汲極至源極端的電壓。如果控制器實施直接感測(Direct Sensing),則可以透過很少的附加元件來實現;如果控制器沒有實施直接感測,則需要額外的外部元件,這不僅增加了總成本,而且本身會引發額外的延遲,進而降低整體能效。直接感測可避免這種潛在的低能效,且在導通和關斷期間都可用。典型情況下,控制器的直接感測接腳需要承受120V或更高的電壓以用於USB-PD應用,為瞬態和異常情況下的瞬時電壓尖峰提供足夠的餘量。

應對功率需求的增加,涉及到導通MOSFET,因此在這種情況下,導通時間延遲極其重要;如果速度太慢,所需電流將流過MOSFET的體二極體而非其溝道,導致無謂的功率損耗和能效下降。

USB-PD配接器的另一個重要考量是符合輕負載和待機功耗限制,如CoC Tier 2和DoE 6級。多數地區都已採用這些或同等標準。無負載時,電源需要能夠檢測到這一點,同時仍能向控制電路(例如USB協定晶片)供電,但仍然保持低於0.075瓦的輸入功率。可檢測到此情況並進入輕負載模式的SR控制器能夠幫助製造商滿足這些要求。

依據應用所需 打造穩定/整合方案

選擇滿足所有這些要求的二次側同步整流器控制器需要仔細考量可用的方案。如前所述,根據應用,配接器設計將針對特定的輸出功率進行最佳化。可提供這種彈性水準的控制器能夠用於多種配接器,透過能提供可調節開關時間的控制器就能實現,時間可在設計時設定。

目前市場上已有業者推出上述所有領域提供同類的性能,如安森美半導體NCP4306,其提供30ns的導通時間和僅13ns的關斷時間,最大化了同步整流器MOSFET的導通時間,同時消除了與一次側開關交叉導通的風險。它在設計上還能夠承受高達200V的直接感測電壓。在7A的汲電流下,控制器可輕鬆驅動小於10mΩ的導通電阻MOSFET,並滿足相應的設計要求,使USB-PD電源配接器能夠在高達100W的條件下工作。

該方案在設計上除了用於驅動經過試驗和測試的中壓MOSFET之外,還有一種可用於驅動氮化鎵(GaN)高電子遷移率電晶體(HEMT),能夠比MOSFET更快地開關。該同步整流器控制器可為GaN提供穩定的驅動電壓(典型值為5V),而不會對其閘極造成過壓,否則可能會導致裝置發生故障。這使其適用於在QR模式下,甚至主動箝位返馳(Active Clamp Flyback)式拓撲結構中工作的超高密度電源配接器。該同步整流控制器(Synchronous Rectifier)的最大工作頻率高達1MHz。圖3顯示了典型應用中的NCP4306。與可實現高達500kHz的高頻QR主控制器NCP1342一同使用時,可實現峰值能效達到93.5%且功率密度接近20W/in3的USB-PD配接器設計。

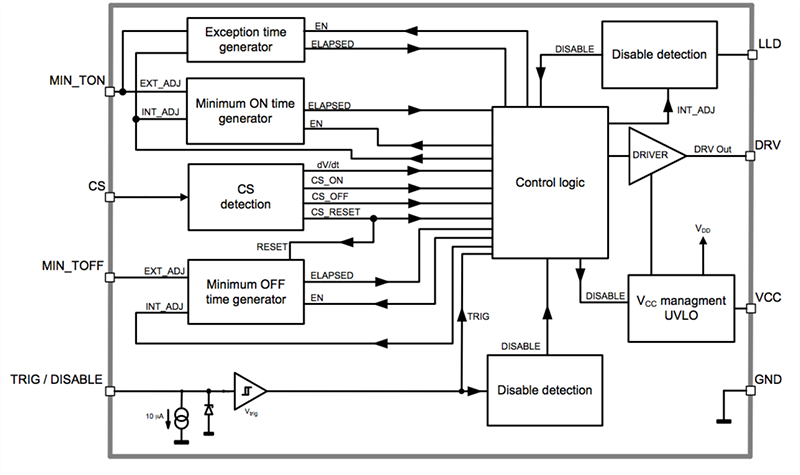

該裝置內部包含用於設置最小導通時間和最小關斷時間遮沒期的模組(見圖4),以對抗由PCB布局和其他寄生元件引起的振鈴,如上所述,這可能導致無謂的體二極體導通。兩個時序參數都可透過外部電阻進行調整,從而為所需的功率輸出和選定的功率元件最佳化設計。輕負載檢測(Light Load Detection)模組可檢測輸出負載降低時電源在跳週期模式下工作時的開關脈衝頻率降低,並將同步整流器控制器進入禁用模式。該控制器在該狀態下消耗的電流非常低(通常為37mA),從而使USB-PD電源配接器能夠符合或剛好超過CoC Tier 2要求。

圖4 NCP4306內部模組框圖

圖4 NCP4306內部模組框圖

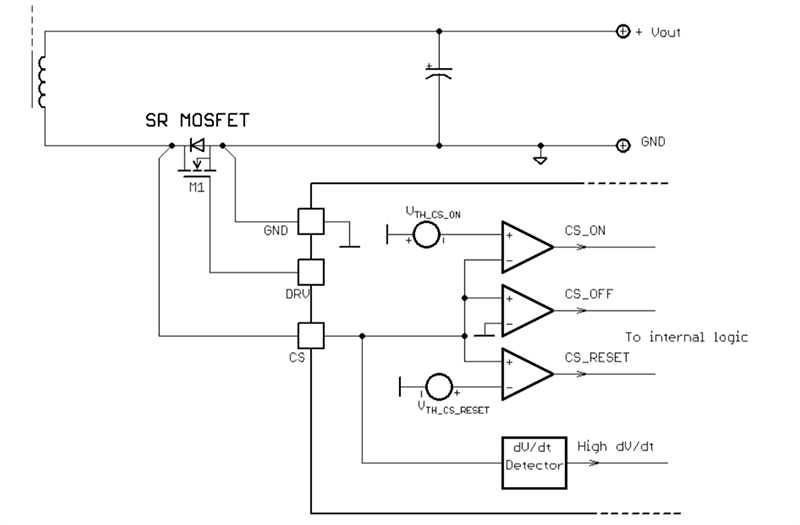

圖5顯示了控制直接感測功能的內部電路。一旦連接到開關汲極端CS接腳上的電壓低於VTH_CS_ON臨界值,同步整流器MOSFET M1就會導通。一旦CS接腳上的電壓高於VTH_CS_OFF(通常為0.5mV),MOSFET就會關斷。NCP4306的直接感測模組內還配備了dV/dt斜率檢測器,以區分閒置狀態下的共振振鈴和實際主開關導通的情況。這對於具有不同輸出電壓和負載曲線的USB-PD設計尤為重要,且有助於確保控制器在需要之時可啟動MOSFET。

圖5 NCP4306實施直接感測,可承受高達200V的電壓。

圖5 NCP4306實施直接感測,可承受高達200V的電壓。

多功能特性突出 Type-C成消費者首選方案

在可預見的未來,使用Type-C連接器透過USB供電預計將主導電源配接器的設計,其在許多應用領域的採用已經非常突出,它的多功能性意味著它將成為製造商和消費者的首選方案。選擇正確的SR控制器對於設計一個最佳化的配接器及其重要,這樣的配接器不僅符合能效法規,還能滿足消費者的嚴苛要求。

(本文作者為安森美半導體策略行銷總監)