常諺有云,需要為發明之母。的確,許多創新發明都是來自解決問題的需求,然而,有時為了滿足急迫的特定需求,吾人的發明難免會因為急就章的緣故而在應用性和效力方面做出妥協。雖然這樣的作法不至於讓一項發明淪落失敗的命運,但就另一方面而言,若這項發明所欲滿足的需求演變成市場主流,則此項發明將因為市場接受度的關係演變出更適合、更有效率的解決方案,進一步提升市場的接受度。此後,當這項廣為接受的發明要補足其之前犧牲的功效範圍時,任何附加或修改的部分都不能對現有生態系統或使用模式增加任何負擔。

暫且將哲學放在一邊,PCI Express(以下簡稱PCIe)規格的定義及進入市場的過程便頗符合此模式。PCIe是一種序列式互連介面,並且被視為是基於匯流排的PCI和PCI-X標準的升級版本,其定義可提供更多及更廣泛的效能,並解決長久以來有關平行匯流排的訊號完整度和電路板布局問題。在要求嚴苛的桌上型電腦和企業運算及儲存應用領域中,對於此一升級的需求尤其急迫,而此需求也就驅使PCI協會(PCI-SIG)和元件業者去修改初始規格和系統解決方案,以符合這些應用的迫切需求。由於規格完全針對這些領域的需求,因此主流的伺服器和儲存市場的早期採用者很快便接受PCIe,且已成為晶片與晶片連接的廣泛標準。

樹狀拓撲應用限制多 PCIe衍生版本問世

雖然PCIe氣勢如虹,且在運算及儲存應用領域中無所不在,但是嵌入式和通訊應用中,要採用PCIe卻是限制重重。一般而言,囿於較長的設計和產品週期,這些領域採用新互連技術的時程常常落後於其他市場。目前在嵌入式和通訊產業過渡到PCIe的速度仍落後於PCI和PCI-X,後兩者目前在控制面板方面仍居於主流地位,且仍能持續滿足更多系統需求。然而,現今下一世代的設計和產品創新已自然地向PCIe靠攏,以利用其完整的生態系統,包括現成的微處理器、周邊和交換式解決方案,這些都以PCIe為內建介面。但即便如此,PCIe的應用在嵌入式和通訊應用市場仍然受限,因為這兩個市場是PCIe的發明過程中被忽略的領域。因此,PCIe規格和支援的產品格式,必須再有所進化,才能滿足這些市場的需求。

PCIe規格將PCIe定義為一種採用樹狀拓撲的連接技術,具有單一根源(Single Root)及多重分支,特別適用於一個運算複合體和其相關本地端輸入/輸出(I/O)之間的連接。此架構對伺服器和儲存應用而言相當完美,但對於採用多重根源架構(Multi-root)的系統而言,卻顯得不適用。先進的通訊和嵌入式系統通常都具有分散式運算和智慧功能,且隨著其發展時間久遠,已普遍吸納PCI和PCI-X概念並環繞著這兩種技術來進行系統設計。因此要在嵌入式和通訊系統中推動PCIe做為主要的系統連接介面,必須在PCIe現有規格上做更多延伸,以支援資源的最佳化利用、高效率的數據傳輸和分享,以及多重根源系統中的各種設備的系統一貫性。

PCIe的生態系統已持續進行PCIe規格的延伸工作,以符合要求嚴苛的嵌入式系統和通訊應用的需求。此項工作受到嚴格的檢視,因為必須在不增加廣大使用者的任何負擔,及不改變現有生態系統或使用模式的情況下進行。

在2008年5月,PCIe-SIG透過PCIe基礎規格2.0修訂版的工程變更通知(ECN),為PCIe標準添加了更多功能性,並針對資料移動和分散系統中各元素的分享提供更強大的功能。這項進展移除了嵌入式系統和通訊應用不採用PCIe做為其主要系統連接介面的最大障礙。PCIe的多點傳輸功能(Multicast)能最佳化系統資源,並且能在減少空轉及增加一貫性的情況下,更有效率地將數據傳輸至各個系統元素。更重要的,PCIe多點傳輸提供許多關鍵好處,讓PCIe規格的延伸不會增加任何負擔,也不用改變現有的生態系統或使用模式。

導入多點傳輸有助分散式架構採用

多點傳輸被定義為同步傳送量化數據封包至一個目標群的方式,且同時必須有效率地管理資源和系統頻寬,以避免任何不必要的資料重複。在一個採用分散式或複製智慧架構的系統,例如嵌入式和通訊應用的系統中,多點傳輸功能可提供一個高效率的一對多傳送機制,以執行像是傳送同步啟動時間或重新設定指令和映像等任務,並減少依序重新設定以及系統停工的時間,並能同步更新重要的路由和指令控制,以確保系統數據的一致性。

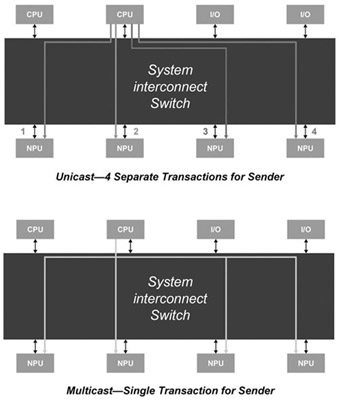

透過多點傳輸功能可以減少傳輸相同數據至各個接收者所需的資源,如此可達到系統資源的最佳化(圖1)。在此模型範例中,一個沒有多重功能的單一PCIe交換和一個支援多重功能的PCIe交換有很大的不同。此具有多點傳輸功能的系統/交換器以單一多點傳輸程序取代四個依序、迴路式的程序,這讓執行的中央處理器能更有彈性地執行其他任務。此種效率能被用以提升效能,如此系統資源能執行其他更多的工作,或是在低效能模式和需要較少系統資源時能節省系統成本及功耗。

|

| 圖1 可減少資源消耗的多點數據傳輸(下)與迴路式單點數據傳輸(下)之比較 |

除了系統資源的最佳化外,將迴路式單點程序改為單一多點傳輸程序能減少傳輸延遲,以強化系統各裝置間的一致性。以圖1的模型為例,假設數據的傳輸順序如數字1、2、3、4所示,則相對於第一個端點,數據傳輸至第四個端點顯然晚了很多,因為第四個端點必須等待之前的程序一再重複並完成。在一個單一根源的系統中,這樣的落差是很好的,因為大部分的數據是由單一主機(Host)所傳送,而此四個過渡程序的重複會在進行下一個動作前完成。然而,在一個採用分散式運算架構,以及顯然為點對點通訊的系統中,反覆的單點程序可能會造成數據傳輸順序的問題,因為封包可能會在不同時間被傳送至每一個端點,而非接收迴路式的單點封包。試想以下情況,有一資訊透過迴路被傳送至各個端點,此資訊為要求某一通訊系統中的封包處理線卡上的四個網路處理器(NPU)更新路由表格,基於依序的傳送和完成,則每一端點更新表格的時間勢必會延長,而此造成的落差會讓這些線卡「空等」它們的更新,之後才能根據最新的表格繼續導引所接收的封包。

多點傳輸數據還能打造系統更佳的連結用途,能除去效能提升的瓶頸,或是提供更小、更有效率的連結,以降低功耗及電路板布局的複雜性。根據上述定義,PCIe協定只有在「分枝」部分才會複製數據。圖2顯示PCIe的互連架構,透過一對PCIe交換可能會有多重跳躍(Hop)。傳送相同、迴路式單點數據至端點1、2、3和4,如圖左方所示,結果會導致相同的數據會多次經過Link 1和4。圖右的系統則為利用PCIe的多點傳輸功能,透過由多點傳輸功能所管理的傳輸機制,此數據經過每一連結的次數僅有一次,在這兩個例子中,數據皆須被合理複製。

|

| 圖2 多點數據傳輸的最佳化使用(右)與迴路式單點數據傳輸(左)之比較 |

多點傳輸提供更多設計彈性

就如文章一開始所述,PCIe標準的快速和廣泛採用,已打造了一個極為豐富的生態體系,以及基於先前規格版本的廣大使用族群。因此,PCIe多點傳輸,就像此規格任何特定的延伸一般,必須對現有生態系統及使用模式不造成影響或是成為負擔。特別是PCIe被定義不須針對現有的根源複合體或端點進行硬體變更,也不需新的資料交易層封包(TLP)格式。

為了在這些限制之下進行最佳化,PCIe多點傳輸被定義為基於位址的多點傳輸功能,其使用一般PCIe的記憶體空間及簡單的程式模型,去導引標準PCIe記憶體寫入TLP至最多達六十四個多點傳輸群組(MCG)中的各個接收者。雖然一個MCG能包含零或一個成員,然而唯有在MCG成員多於二時,系統才會有所好處,因此PCIe交換(或是序列交換)必須被用以提供起始者和MCG成員間的連接。PCIe群組中的任何一個裝置都可以擔任開啟多點傳輸交流的角色,並將交流傳遞給附屬於多點傳輸功能結構(Multicast Capability Structure)交換的任何成員。針對每一個交換埠,多點傳輸功能結構交換皆能自任一連接埠將封包傳輸至其他任一連接埠。由於具有多點傳輸功能結構,根源複合體和端點能從中獲得好處,但是,就如前文所述,對於這些裝置而言,此為一可選擇的特性。

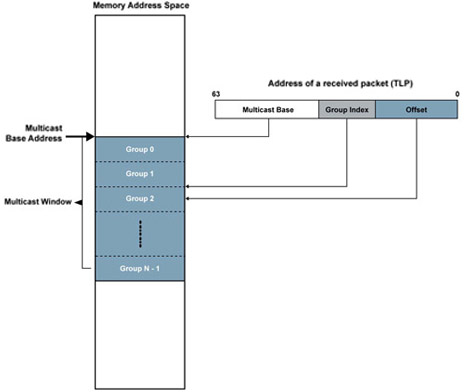

對系統而言,其並未因具有多點傳輸功能而受到影響,系統軟體藉由在PCIe記憶體空間中開啟一個多點傳輸視窗而形成多點傳輸位址空間,其開始於如圖3所示的多點傳輸視窗基礎位址(Multicast Window Base Address)。從此基礎位址開始,多點傳輸視窗被組為一個連續性的位址範圍,其可能會針對最多六十四個支援MCG中的每一個成員,而被分為相同大小的次範圍。其中對於多點傳輸視窗的大小並未有實質限制,例如多點傳輸視窗可大至263位元。多點傳輸視窗中的群組數目約在一至六十四的範圍內。

|

| 圖3 多點傳輸記憶體視窗和PCIe TLP路線 |

支援多點傳輸服務系統中的PCIe裝置必須要具有多點傳輸功能結構,讓每一個PCIe功能皆能進行多點傳輸,因此,在一個PCIe交換中,傳輸或接收多點傳輸數據的每一個交換埠都必須在其相關的虛擬PCI至PCI(P2P)橋接中支援多點傳輸功能結構。在每一個多點傳輸功能結構中,相同組成的控制暫存器包含下列資訊:多點傳輸視窗基礎位址、MCG的數目和MCG視窗大小。此外,每一個功能結構都擁有一個獨立組成及維護的六十四控制位元向量,其能促使接收或無法接收來自0~63的TLP,如此便能控制每一個MCG中的每一個具有PCIe功能的成員。此暫存器和控制位元在裝置運作的任何時間點皆可被讀取及寫入。

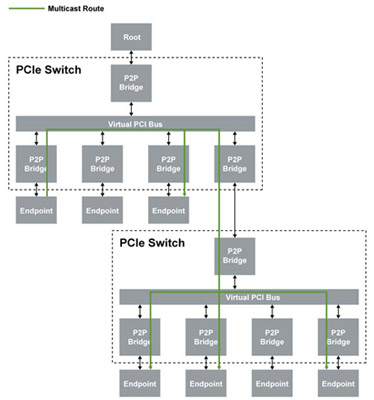

多點傳輸PCIe TLP的傳輸和路由稍微不同於單點TLP。圖4所示的基本功能PCIe交換圖表可清楚描述這些不同。在接收到一個來自根源的TLP時,位於入口埠的位址編碼會測定此TLP是否為多點傳輸TLP(邏輯上來說,初始程序便是在此處轉變為多點傳輸程序。)沒有錯誤、經過解碼的TLP會被傳送至此交換的虛擬PCI匯流排。不像單點交流,其具有不同的路由規則,是根據此TLP是在P2P橋接的主要或次要部分被接收,多點傳輸TLP則是系統性地傳送TLP,完全不考慮P2P橋接是否具有上鏈或下鏈交換埠。

|

| 圖4 PCIe多點傳輸範例--交換功能檢視 |

所有連接至虛擬PCI匯流排的交換埠(例如P2P功能)皆會接收多點傳輸TLP,並根據啟動多點傳輸接收(Multicast-receive-enable)向量中的位元狀態去檢視位址中的MCG ID。在個別MCG的基礎上,此啟動多點傳輸接收向量會指示一個P2P功能是否被允許傳送TLP至其目的。這讓交換中的每一P2P橋接功能在個別群組的基礎上,能將自己登錄為一個多點傳輸TLP的接收者。

一旦此交換中的一個P2P橋接功能接收到一個多點傳輸TLP,則其會在此TLP上執行輸出程序。根據和此P2P相關的交換埠上的連結夥伴的功能,多點傳輸TLP的輸出程序會有所不同。在此情況中,此連結夥伴具有多點傳輸功能結構,例如圖5所示的PCIe交換至PCIe交換,則此TLP會在毋須修改的情況下被進一步傳送。然而,就如前文所述,PCIe端點並不須具有多點傳輸功能結構才能接收多點傳輸TLP。為支援不具有多點傳輸功能的端點,系統軟體必須保證此端點的基礎位址暫存器會與多點傳輸位址範圍部分重疊,或是PCIe交換必須利用可選擇指定的多點傳輸覆蓋機制。

|

| 圖5 PCIe多點傳輸範例--多重交換系統中的路由 |

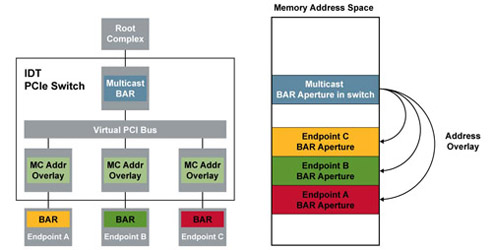

確認端點功能位址範圍和多點傳輸位址範圍的確有所重複,這樣的工作加重了系統設計人員的負擔,而且每一個產品單品(SKU)可能還需要獨特的編碼基礎,因此定義良好的交換執行便很重要,可以在每一個交換埠的多點傳輸功能結構中落實多點傳輸覆蓋的特性,以支援最大的彈性並利用目前可用的端點。此位址覆蓋功能,如圖6所示,為一個可被用以重新分配被接收到的多點傳輸TLP位址的機制,自多點傳輸視窗到端點的基礎位址暫存器(BAR)視窗。此位址覆蓋是由交換埠所執行。每一交換埠可能與一個不同的位址覆蓋值搭配,以允許能獨立分配至每一端點的BAR視窗。支援32位元和54位元位址間的轉換,例如此多點傳輸區域可能會在4Gbytes範圍之上,而端點的BAR可能會在4Gbytes範圍之下,或是相反。

|

| 圖6 多點傳輸覆蓋結構實現和記憶體分配 |

擺脫舊包袱 PCIe大舉進軍嵌入式應用

因需求而誕生,符合苛求的桌上型和企業及儲存應用的迫切需求,PCIe標準已成為晶片至晶片互連的主流介面,擁有豐富的生態系統,以及數量龐大的終端應用基礎。為求完全滿足這些大量、早期採用的應用的需求,此規格和早期的產品形式都是針對他們的核心需求而量身打造。隨著其他終端應用和使用模式的出現,此規格和生態系統正不斷發展以擴大適用的應用範圍。

最近PCIe所增加的多點傳輸功便是一必要的發展,能最佳化系統資源的利用,並藉由減少系統空轉、支援多重根源的嵌入式和通訊系統中,點和點間的高效率及一致的數據傳輸,以大幅增加系統效能。在不能對現有生態系統或使用者族群造成負擔的嚴格條件下,此擴充的功能不須改變根源或端點的硬體,也不用新的TLP格式。此基於位址的PCIe多點傳輸功能,具有極簡化的程式化模型,能在PCIe交換中執行,並提供超過預期的強大功能和彈性,實現各種獨特設計,例如雙埠介面(Dualcasting)等。

(本文作者任職於IDT)