早在兩年前IEEE報告就指出,2015年通訊網路的傳輸容量要求將達1Tbit/s,到2020年更必須支援到10Tbit/s。

該報告還指出,2015年固網和行動網路裝置數量將多達一百五十億台,其中還包含機器對機器(M2M)的互連;在光傳輸網路(OTN)應用方面,核心節點的每波長頻寬到2015年預計達到100G?400G,到了2020年更會提升到400G~1T。

新型FPGA可滿足1Tbit/s應用

為了滿足TB級的網路應用,市場上推出UltraScale All Programmable現場可編程閘陣列(FPGA),該元件可支援1Tbit/s系統的建置,且具理想效能、系統整合度和高頻寬,廣泛適用於有線通訊、量測、航太國防及資料中心等各種應用。

事實上許多公司早已表示對1TB網路應用的需求,希望收發器能直接驅動25G/28G背板,進而解決布線性(Routability)、串音(Crosstalk)、差動式饋入損耗(Differential Insertion Loss)和阻抗匹配(Impedance Matching)等問題。

新款FPGA可以克服以上問題,且毋須使用重定時器,即可提供25G/28G背板操作,進一步支援各種1Tbit/s應用。

|

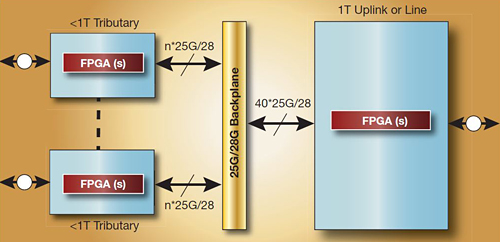

| 圖1 在高層次TB級系統概念圖中,多個低於1Tbit/s的支路板與一個1Tbit/s的線卡進行訊號傳輸。 |

圖1是通用的1Tbit/s系統高層次模塊圖。其中,多個頻寬低於1TB的支路板(圖1中有兩個)透過運行速率為25G/28G的背板與一個1T線卡相連。

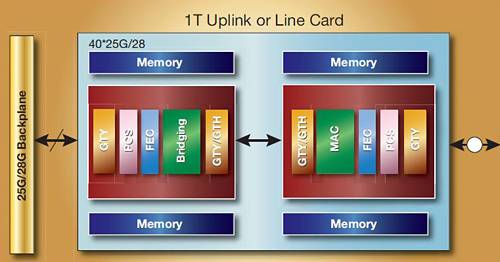

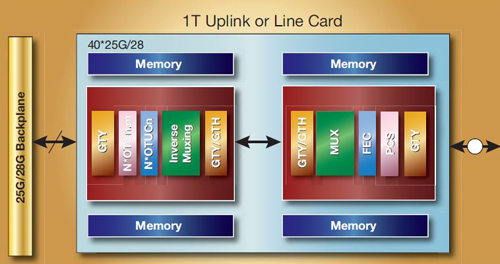

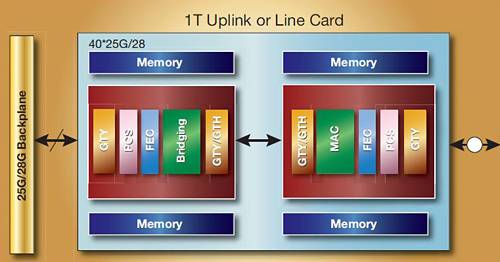

圖2、3和4則為三種1Tbit/s乙太網路和OTN可能應用的模塊圖,全都以新型FPGA為基礎。

|

| 圖2 多個低於1Tbit/s的乙太網路支路板透過25G背板連結對1TB乙太網上行連結模組傳輸訊號。 |

25G背板收發器戰勝可布線性問題

從上述的模塊圖可以了解,若沒有支援25G/28G的背板收發器,則難以實現各種1T網路應用。而若只有一個僅具備10G連結的背板,則會產生布線性、串音、差動式饋入損耗,甚至是阻抗匹配等問題。

可布線性問題

這些實例展示以總頻寬為40×25Gbit/s

=1Tbit/s的速率,在25G/28G背板上運行的四十個通道。背板厚度通常約0.25英吋,其主要取決於兩個因素:連接器壓裝的機械及支援多個通道路由的需求。

|

| 圖3 1TB乙太網上行連結模組在OTN連結上分佈有效載負,透過25G/28G背板連結重複使用既有的OTN線卡(<1Tb)。 |

若背板介面僅支援10Gbit/s的運作,通道數就須要增加到原來的2.5倍,每個1Tbit/s線卡和支路板的背板通道數量會從四十個增加到一百個。在需要二十五個支路板和線卡的系統中,最終所需的通道總數則為100×25=2,500,會為路由造成很大的問題。

|

| 圖4 1TB OTN線卡透過28G背板連結重複使用從低於1TB OTN支路模組傳送的訊號。 |

使用背板介電材料時,以Megtron-6為例,其介電常數約為3.65且標準導線寬度為7mil,使用者會發現每個差動式帶狀線對的堆疊高度為:每100歐姆(Ω)的差動奇模阻抗對應16mil。

假設背板連接器間距通常是2毫米(mm),就是每層連接器的引腳間可以建置一個通道。因此,背板每層能夠在每個連接器支援十個通道(發送+接收)的作業。

如果以25Gbit/s的速率運作,通常需要十六個布線層,背板總厚度為16mil×16布線層=0.256英吋。如果是10Gbit/s的運作速率,則厚度為0.640英吋(16×2.5=40布線層,背板總厚度為16mil×40層=0.640英吋)。

但是,背板最大厚度通常由通路孔的深寬比決定,典型通路孔直徑為15mil,標準深寬比為25:1,代表背板厚度上限約為 14×25=350mil。因此,10G背板無法支援1T應用。

串音問題

對1T應用而言,相較於10G背板,25G背板的另一個關鍵優勢是串音效應。串音通常是通道距離太近所引起,背板通道越多,串音的機率就越高。因此,比起擁有兩千五百個10G通道的背板,擁有一千個25G通道的背板較不會有串音問題。

但是大多數介電材料並不完全同質,因此會有遠端串音(FEXT)效應。而在背板連接器周圍的通路孔區域發生的通常為遠端串音。

由於背板系統的串音問題可以同時是近端串音(NEXT)和遠端串音效應,系統設計師必須留意要降低與總雜訊預算相關的串音雜訊成分。

事實上敏感元件和干擾源網路之間均存在互電容電場(Cm)與互感磁場(Lm)。互感會在與干擾源網路相對的敏感元件線路上感應產生電流(冷次定律);互電容會通過互電容傳遞在敏感元件線路上的雙向電流,而近端和遠端敏感元件線路上的電流會一起產生近端串音和遠端串音效應,如公式1。

I(Next)=I(Cm)+I(Lm) while I(Fext)= I(Cm)–I(Lm) ................................公式1

近端串音都是正數的;遠端串音可以是正數,也可以是負數。

差動式饋入損耗

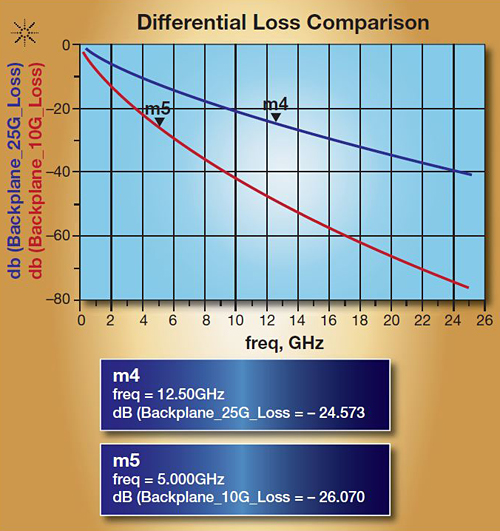

通道的饋入損耗是建立可靠連結時的重要參數。饋入損失取決於兩個因素:連接器損耗和介電損耗,使用Megatron-6等介電材料時,切線損耗為0.004,圖5顯示1公尺長走線的饋入損耗,表面粗糙度為1微米(超低截面)。

由於背板的最大厚度為0.350英吋,10G背板的走線寬度已經降到只有3mil,以允許差動奇模阻抗維持100歐姆的情況下,在0.350英吋厚的背板上鋪四十層布線。另一方面,25G背板的走線寬度為7mil,可在最大厚度為0.350英吋的背板上鋪十六層布線。

圖5所顯示的10G背板的差動式饋入損耗高於25G背板,是因為10G背板在最大背板寬度內增加布線層數,所以導致走線寬度變窄。

|

| 圖5 25G和10G背板分別在各自的奈奎斯特頻率(Nyquist Frequency)中顯示饋入損耗。 |

新式的FPGA元件毋須使用重定時器即可支援25G/28G背板的操作,進而支援各種1Tbit/s的應用。這些將要上市的1Tbit/s應用要求接收器能夠直接驅動25G/28G背板,以解決布線性、串音、差動式饋入損耗和阻抗匹配問題。因為過多的布線層數、更大的連接器和通路孔深寬比相關的可靠度問題都會產生某種程度的影響。

由於背板重定時器是一項附加元件,須建置在線卡和支路板上,所需的電壓調節模組、配電網路、直流阻斷器和參考時脈都會占用印刷電路板(PCB)空間。由此可知,使用外部重定時器除會產生可靠性問題,還會占用大量且耗費成本的PCB板空間。

(本文作者皆任職於賽靈思)