如同其前一代產品周邊裝置元件互連(Peripheral Component Interconnect, PCI),PCI Express正在成為普遍使用的系統介面。與PCI不同的是,PCI Express採用串列器/解串器(SERDES)介面,為用戶提供了未來應用所需的可拓展性。

隨著系統頻寬的提高,更多的應用開始使用基於SERDES的介面,如PCI Express。過去,通常使用特殊應用積體電路(ASIC)或特殊應用標準產品(ASSP)來實現下一代介面解決方案。ASIC和ASSP因為可以提供低成本、低功耗的設計解決方案而被廣泛採用。然而,現在一些新的現場可編程閘陣列(FPGA)系列為設計師提供更具吸引力的選擇。

FPGA提供極具靈活性的平台,並且不像ASIC或靈活性較差的ASSP需要冗長的研製時間和大量的非重複性工程費用(NRE)。新一代含嵌入式SERDES的FPGA如萊迪思(Lattice)ECP2M和LatticeECP3元件,具備極其豐富、高價值的可編程架構,並針對串列介面推出一種低成本、低功耗的解決方案。這些FPGA還能夠支援各種串列協定,如PCI Express、超高速乙太網路(GbE)、序列Gigabit媒體獨立介面(SGMII)、10GbE附加單元介面(XAUI)、串列RapidIO等,可使用單一FPGA平台實現多種設計。

PCI Express也開始代替過去的平行介面如PCI,成為控制板應用的介面選擇。新一代元件使用一個或多個PCI Express介面。在大多數元件中,PCI Express可作為一個PCI Express端點來實現。設計師通常須要將這些元件與前幾代採用平行匯流排的元件連接,例如帶有平行匯流排介面的微控制器。使用一個低成本、低功耗的FPGA來橋接PCI Express和平行介面,讓設計者擁有足夠的靈活性,可在毋須超出系統成本和功耗預算的前提下,輕易地解決這個問題。

協定糾結/設計難題伴隨而來

當設計師將設計從PCI遷移到PCI Express時,協定錯綜複雜的細節與基於SERDES設計的複雜性將帶來巨大的挑戰。幸運的是,FPGA和全功能PCI Express矽智財(IP)、參考設計、硬體評估板和相關的實作過程有助於設計順利進行,否則PCI Express設計師將面臨困難曲折的研究學習過程。

事實上,FPGA是一種基於PCI Express應用的理想平台。由於FPGA的可編程特性,使得設計師擁有更大的靈活性,在之後的設計週期中能夠以很短的周轉時間來解決設計問題。設計師還須要為每個設計需求演變過程中的特性更改或添加作好準備。

此外,FPGA的設計讓設計者能根據新的參數規格更改與更新設計,從而使產品不會因過時而被淘汰。可編程平台還可使用同一款FPGA來實現介面解決方案,連接到大量其他PCI Express晶片集:端點元件、Root Complex或開關。此外,還可以將系統所需的其他功能放到FPGA中,減少電路板上的元件數量,並進一步降低系統的總成本。

FPGA提供靈活可編程平台

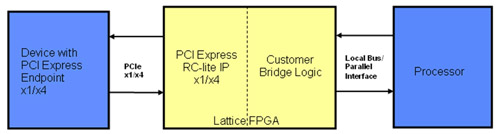

FPGA為系統設計提供極為靈活的可編程平台。全套解決方案包括矽智財、硬體平台、演示設計、驅動器和軟體,使得設計師能縮短其開發週期,同時降低設計的複雜性。PCI Express解決方案常見的設計要求是PCI Express串列介面(端點元件)與合法的平行匯流排介面之間的橋接(圖1)。

|

| 圖1 PCI Express橋接解決方案 |

含PCI Express Root Complex矽智財的FPGA,為設計師提供了實現這樣一個解決方案所需的基本構建模組。或者,也可以使用ASSP和ASIC來實現該功能。然而,與FPGA不同的是,這些元件僅能實現一種固定的配置,且不能更改來實現其他可用的平行匯流排介面。相反地,可編程FPGA平台可在設計中進行更改來達成特定的橋接功能,以符合其特定板上可用介面的要求。設計者還能靈活地在單一FPGA中完成多種橋接或不同橋接配置,從而減少電路板上元件數量。由此可見,內含PCI Express Root Complex矽智財的FPGA可以提供設計所需的多種其他橋接解決方案。

以Root Complex達成橋接功能

以PCI Express端點當作一個訊號發出(Upstream)元件時,不能與訊號接收(Downstream)元件通訊。該功能可由Root Complex元件來達成,但是使用FPGA的全功能Root Complex非常昂貴。反之,一個具備傳輸層功能子集的「輕量版」Root Complex核心則足以實現大部分橋接功能。

如圖1所示,該橋接由兩個基本建構模組組成。第一個模組是PCI Express Root Complex(或Root Complex-lite)矽智財與PCI Express端點元件介面。第二個模組是橋接邏輯,用以介面到本地匯流排/平行介面。因為採用可編程FPGA來實現,設計師能有極大的靈活性制定基於特定介面需求的設計。其他功能也可以放在同一個FPGA內,以減少電路板上其他元件的數量,並降低元件材料的總成本。

支援PCI Express Root Complex矽智財

PCI Express是一個複雜的協定。全功能、充分驗證的PCI Express矽智財能夠大幅降低設計的複雜性。例如,Lattice PCI Express Root Complex Lite(RC-lite)內提供一個×1或×4 Root Complex功能,主要用於PCI Express橋接應用。

|

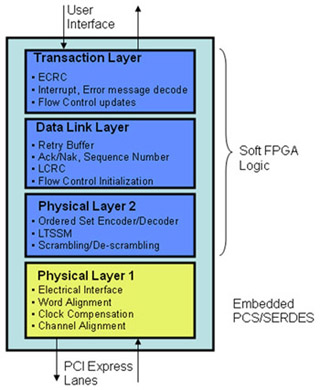

| 圖2 PCI Express RC-lite IP協定堆疊 |

如圖2所示,所有的PCI Express層都使用嵌入式ASIC模組和PCI Express RC-lite矽智財在FPGA中實現。各個模組包括電氣SERDES介面、物理層、資料連結層,以及支援完成PCI Express Root Complex功能所需的協定堆疊(Protocol Stack)最簡化的傳輸層。這個「輕量的」矽智財專為用於簡單橋接PCI Express端點介面和並行本地匯流排介面應用而優化。

LatticeECP2M或LatticeECP3 FPGA中的PCI Express RC-lite IP實現了低成本、低功耗的PCI Express橋接應用,同時為設計師提供制定橋接介面的靈活性。此外,PCI Express硬體評估板和各種參考設計、演示板和軟體驅動協助設計師快速設計PCI Express並縮短產品上市時間。萊迪思還提供了一款硬體評估板用以測試RC-lite IP解決方案。設計師還可以在實際部署之前,完成其解決方案的操作性並驗證其系統功能,節省一般設計後調整與性能增強所需的時間和成本。

FPGA可降低設計難度

PCI Express讓設計師面臨很大的設計挑戰。而介面需求根據元件是否須連接到其他端點、Root Complex或開關而各不相同。

此外,在許多情況下,PCI Express端點須要使用平行匯流排介面連接到另一元件。設計者可以使用低成本、低功耗的FPGA平台來達成這些功能,同時保留靈活可編程架構的所有優點,例如在一個FPGA中完成PCI Express Root Complex IP功能,為實現這些橋接功能提供理想的平台。

(本文作者任職於萊迪思)