積體電路(IC)是所有現代安全系統的根基。積體電路所提供的邏輯機制,本身可用來控制感測器或是扮演感測器的角色。IC驅動著各種最終元素,藉以達到安全狀態,另外它們也可作為平台,讓軟體在這類平台上運作。

半導體內部的整合雖然可以簡化系統層級的建置,但付出的代價則是IC內部的複雜度提高。如此的整合度提高了系統的可靠度,因為除了減少零件數量,同時還提供許多機會,讓用戶以更低的診斷測試間隔增加診斷的覆蓋率,這些因素降低了成本,讓安全性可更輕鬆負擔。但也有人指稱這樣的整合度不是好事,因為它會提高複雜度。但IC複雜度提高的代價卻也換來模組與系統層級的大幅簡化。

出乎意料的是,雖然各界已制定各種功能安全標準來規範包括流程控制、機器、電梯、可變速驅動器、以及有毒氣體感測器等,但卻尚未針對積體電路訂立功能安全標準。反觀IEC 61508與其他B級(Level B)與C級(Level C)標準各方面的要求與知識,則早已全面普及。本文將引導讀者解讀目前針對半導體所規範的現有功能安全標準。

積體電路一般都是針對IEC 61508或是ISO 26262標準所著手研發。此外,有時還須依循第二級與第三級標準的額外規範。依照這些功能安全標準進行研發與評鑑,讓業者有信心確定這些有時相當複雜的積體電路能具備足夠的安全性。IEC 61508在制定時是鎖定各種客製型系統,而不是針對開放市場的量產IC。本文將探討與評論針對IC規範的現有功能安全要求。此外,本文也將討論IEC 61508及其在工業領域的應用,但許多素材也與包括汽車、航空電子、以及醫療等領域的應用息息相關。

功能安全

功能安全是整體安全的其中一個環節,其涉及到對特定系統的信心,反映出當系統在需要執行安全相關任務時是否能確切執行。功能安全不同於其他被動型態的安全性,像是電氣安全、機械安全、或是本質安全(Intrinsic Safety)。

功能安全屬於主動形態的安全性。舉例而言,馬達的安全功能賦予人們信心,足以相信發生事故時馬達會關得夠快,避免開啟安全門的操作員受傷,或是讓機器人在有人類靠近時能自動降低操作的速度與力道。

標準

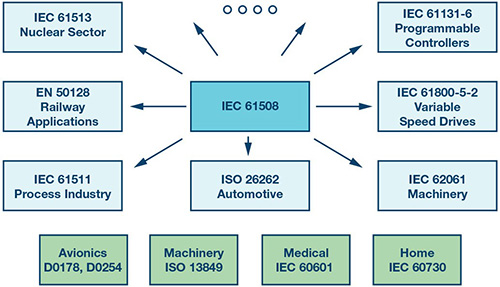

最關鍵的功能安全標準當屬IEC 61508[1],其第一次改版於1998年公布,第二次改版則於2010年公布,2017年開始生效,第三版可能在2022年修訂完成。自從IEC 61508於1998年發表第一版以來,IEC 61508標準針對各個領域進行調整,包括汽車(ISO 26262)、流程控制(IEC 61511)、PLC(IEC 61131-6)、IEC 62061(機械)、可變速驅動器(IEC 61800-5-2)、以及其它諸多領域,這些標準說明了IEC 61508廣泛涵蓋這類較為受限的領域。

有些功能安全標準,諸如ISO 13849與D0-178/D0-254等,它們雖不是從IEC 61508所衍生出來的,但任何熟悉IEC 61508的人在閱讀這些標準時,都不會對其內容感到陌生。

在一個安全系統中,各種安全功能負責在系統運行時執行關鍵的功能安全動作。安全功能定義了一項必須執行以達成或維持安全性的作業。典型的安全功能包含一個輸入子系統、一個邏輯子系統、以及一個輸出子系統。通常這意謂著當偵測到不安全狀態時,某個機制會根據感測到的數值做出決策,若是判斷有潛在危險,就會指示輸出子系統將系統轉至事先定義的安全狀態(圖1)。

|

| 圖1 一個功能安全標準的範例 |

從離開不安全狀態轉換到安全狀態之間的時間非常重要。舉例來說,某個安全功能可能包含一個感測器,主要負責偵測機器上的某個保護裝置(Guard)是否開啟,其由一個可程式邏輯控制器(PLC)負責處理資料,透過一個可變速驅動器施予一個安全範圍內的扭力來關閉輸入閥,藉以關閉馬達,及時防止伸入機器的手部觸碰到運轉的部件。

安全完整性等級(Safety Integrity Levels)

SIL代表安全完整性等級的英文縮寫,用來表達要將風險降低到可接受的水準所必須降低的風險程度。根據IEC 61508,安全等級(Safety Level)分為1到4,每增加一個數字代表安全高出一個等級。在機械與工廠自動化方面並沒有SIL 4,因為這些環境中,通常曝露在某一種危險狀況下的不會超過一個人。SIL 4是保留給例如核能與軌道交通等領域,這些領域一旦發生事故往往導致成千上萬人受害。另外還有其他功能安全標準,像是汽車採用的汽車安全完整性等級(ASIL)A、B、C、D;以及ISO 13849,其性能水準a、b、c、d、e可對應到SIL 1到SIL 3(表1)。

|

| 表1 各種應用領域中安全等級的大略對應表 |

本文對單一IC能否達到SIL 3以上等級的可能性持保留態度。不過在IEC 61508-2:2010附錄F的表格中確實有一個SIL 4欄位。

三項關鍵要求

功能安全對IC的研發規範了三項關鍵的要求,以下章節則將深入探討。

要求1—依循嚴苛的開發流程

IEC 61508是覆蓋完整生命週期的典範,涵蓋從安全概念、需求攫取(Requirements Capture)、維護、一直到最終的處置等所有階段。但這些階段並不是全都和IC有關,必須有足夠訓練以及經驗才有辦法分辨出它們。IEC 61508針對特定應用積體電路(ASIC)提供一種V模型,連同IEC 61508的檢查、稽核、以及其他要求,構成一整個系統,雖然它不能保證安全性,但在過去證明能產生各種安全系統以及開發出各類IC。

絕大多數IC製造商對於新產品研發都設定了嚴苛的標準,因為要修改具有瑕疵的IC必須投入極昂貴的成本。光是一組小幾何格局(Low Geometry)製程的光罩,其成本就超過50萬美元。再加上冗長的前置時間,種種因素迫使IC設計業者實施嚴苛的開發流程,其中納入許多妥善的驗證與確認階段。功能安全其中一項重大差異,就是安全不光是要達成,還得要展現出來,因此即使是頂尖IC製造商也必須在正規開發流程上再額外加入安全流程,以確保能產生與達成正確的合規性(Compliance)證據。

開發過程中產生的錯誤是屬於系統性錯誤(Systematic Fault),這類錯誤僅能透過設計變更才有辦法修正。系統性錯誤包含和需求攫取、電磁相容穩健性不足、以及測試不充分等因素有關的錯誤。

IEC 61508-2:2010的附錄F列出了一組專屬的衡量指標,IEC委員會的專家認為它們適合用來開發積體電路。表F.2適用於現場可編程陣列(FPGA)與複雜可編程邏輯元件(CPLD),而表F.1則適用於數位ASIC。這些指標依照SII分為建議(R)或高度建議(HR)類別,在某些情況還提供各種替代技巧。對於有完善開發流程的IC供應商而言,這些要求很少會讓廠商感到意外,但在SIL 3規定的99%失效涵蓋率(Fault Coverage)就相當具挑戰性,尤其是小型數位或混合訊號元件,這類元件相當大比例的電路屬於專利區塊。

在第二版標準的一些要求雖然是針對數位IC,但也適用於類比與混合訊號IC(下次改版的ISO 26262將納入類似表格,以及針對類比與混合訊號IC推出的版本)。

除了表F.1與表F.2,還有一些介紹章節讓大家有深入的認識。舉例來說,在介紹段落中提到使用工具的一項容許差(Allowance),並規範18個月的建議期限,在合理的範圍內運用到複雜度相近的多個專案。這意謂著並不需要套用IEC 61508-3全部的工具要求。

如果模組/系統設計者過去已成功使用IC並知悉其應用以及在實地環境的失效率(Failure Rate),即可賦予運轉經驗證明(Proven in Use)。IC設計業者或製造商要取得這項證明其難度來得更高,因為他們通常對最終應用並沒有足夠的知識,對於退回來要求分析的零件,也不知它們在實地運行環境的失效比率。

軟體

所有軟體錯誤都屬於系統性,因為軟體不會有老化的問題。因此任何晶片內建軟體都應考量IEC 61508-3的要求。一般而言,晶片內建軟體可能包含一個核心/開機載入程式,在微控制器/DSP上運行。但在一些情況中,微控制器/DSP可能含有IC製造商編寫的小型微控制器以用來建置一個邏輯區塊,而不是使用狀態機器。這種程式化微控制器軟體可能必須符合IEC 61508-3的規範。應用程式層級的軟體通常由模組/系統設計者負責,而不是IC製造商,但IC供應商可能需要提供相關工具,像是編譯程式或低階驅動程式。如果這些工具用來開發安全相關的應用軟體,那麼IC製造商就必須為最終使用者提供足夠的資訊,才能符合IEC 61508-3:2010標準中7.4.4條款關於工具的要求。

筆者自己也使用包括C與其他許多程式語言,另外還使用有限數量的Verilog語言。Verilog與其姊妹語言VHDL正是其中兩種用來設計數位IC的硬體描述語言(HDL)。究竟HDL是否屬於軟體,這個問題很耐人尋味,但當前光是要遵循IEC 61508-2:2010附錄F,問題就已經夠多了。在實務面上,筆者發現遵循附錄F再加上IEC 61508的其他要求(生命週期階段等),究竟HDL是否被視同為軟體並不重要,因為開發者到最後還是得完成所有必要的工作。另一個有意思的相關標準是IEC 62566[2],用來規範以HDL語言為核能產業開發安全功能。

要求2—本質可靠

IEC 61508以每小時危險失效率(PFH)或失效危險機率(PFD)的形式訂立許多可靠度要求。這些限制代表成年人因自然災害致死的風險,而你的日常業務不應讓這個風險顯著增加。SIL 3安全功能的最大PFH為10-7/h,大約是每一千年出現一次危險失效。若以FIT(失效率/每十億小時運作的失效數)來表示,則換算出來的就是100FIT。

由於典型的安全功能包含一個輸入模組、一個邏輯模組、以及一個致動器模組,因此PFH預算就得分配到所有三個模組,對於PFH而言這完全可行,因為整個IC的PFH只有一位數字(小於10FIT)。採取冗餘架構即可容許更高的數據,讓兩個100FIT的項目等同於一個項目的信心度,10FIT的可靠度受限於共因失效(CCF)的問題。不過,冗餘配置的設計不僅會消耗大量的空間與電力,還會增加成本。

一般建議採用業界普遍依循的標準,像是SN 29500[3]或IEC 62380[4]。但這些標準也存在許多問題,包含;

諸如SN 29500這類標準,所展示的是晶片內建電晶體究竟有多麼可靠。若以兩顆內含50萬個電晶體的IC來建置一種安全功能,如果每顆的FIT為70,那麼整個系統的FIT就是140。但若用一個內含100萬電晶體的IC取代兩個IC,那麼一顆IC的FIT僅為80,降低幅度就超過40%。

在IC內的軟性錯誤(Soft Error)通常會被忽略。軟性錯誤不同於傳統可靠度預測,因為一旦電力經過循環,軟性錯誤就會完全消失。軟性錯誤是由太空中的中子粒子或封裝材料的Alpha粒子撞擊到晶片內部RAM基本結構或正反器(FF)所造成,而且會改變儲存值。

雙位元錯誤偵測與單位元錯誤偵測(ECC)可用來偵測與無縫校正RAM內的錯誤,但代價則是速度的降低以及更高的晶片內部錯誤。同位(Parity)增加的負載就比較少,但系統設計者必須解決錯誤回復的問題。如果不採用同位或ECC技巧,軟性錯誤率就會超越傳統硬體錯誤率,幅度達到1,000倍(IEC 61508針對RAM規範的數據是1,000FIT/MB)。現今用來解決FF中軟性錯誤的技巧被用來建置邏輯電路,但其結果不盡人意,反倒是包括看門狗計時器、計算方面的時間冗餘性、以及其他技巧則確實有所幫助。

要求3—要有容錯性

不論產品有多麼可靠,會發生的意外終究還是會發生。容錯(Fault Tolerance)是指接受這樣的事實,然後著手解決。容錯有兩個主要元素。其一是採用冗餘配置,另一項則是使用診斷法。不論IC多麼可靠,也不管IC採用什麼樣的開發流程,兩者都會接受發生失效的狀況。

冗餘可以是同樣或多樣性,也可建置在晶片內部或晶片外部。IEC 61508-2:2010的附錄E提供一套技巧,展現採用非多樣冗餘配置的IC,運用足夠的措施來支援晶片內的冗餘配置。附錄E似乎是鎖定雙重鎖步微控制器,對於以下項目的晶片內部獨立性並沒有提供指南:

但在某些情況下,可針對這些案例對附錄E做巧妙的解讀。附錄E裡有一個有趣的項目就是βIC的計算,它代表的是晶片內部的共因失效。β值低於25%,即可判斷共因失效的來源有足夠的隔離,這樣的數值相較於IEC 61508-6:2010表格中所列出的1%、5%、或10%都高上許多。

對積體電路而言,診斷是其中一個關鍵領域。晶片內部診斷必須滿足以下功能:

這意謂著晶片內部診斷機制能將系統成本與空間減至最低。通常診斷機制迥異於(不同作法)它們監視的晶片內部項目,因此它們極不可能會和自己所監視的項目在相同時間以相同方式發生失效。倘若真的發生同時失效的狀況,那麼很可能它們具有相同的問題(通常和電磁相容、電源問題、以及溫度過高有關),甚至以不同晶片建置診斷機制也會發生相同失效狀況。儘管標準中並沒有列入相關要求,但使用晶片內部電源監視器與看門狗電路時會產生一些疑慮,這些都屬於最後手段的診斷方法。有些外部技術顧問往往堅持這樣的診斷機制應建置在晶片外部。

通常較簡單的IC所建置的診斷機制會由遠端的微控制器/DSP加以控制,量測程序則是在晶片內部執行,而結果則會傳到晶片外部進行後續處理。

IEC 61508要求最低診斷覆蓋率的單位為安全失效比率(SFF),SFF考量安全與危險失效的關聯,但不同於忽略掉安全失效的診斷覆蓋率(DC)。要衡量已建置診斷機制的成效,可使用量化失效模式與影響分析(FMEA)或失效模式影響與診斷分析(FMEDA)。不過建置在IC內部的診斷機制也可涵蓋IC外部的元件,而IC內部的項目則可透過系統層級診斷機制來涵蓋。IC開發商在執行FMEDA時,必須假設IC開發商不知悉最終應用的細節。在ISO 26262的詞彙中,會將此稱為獨立安全單元(SEooC)。對於利用IC層級FMEDA的最終使用者,他們必須確定這些假設在其系統上仍能成立。

在IEC 61508-2:2010的表A.1(以及表A.2到A.14)則列出了在分析IC時應考慮到哪些IC失效狀況,甚至在IEC 60730:2010的附錄H中進一步探討這項議題。

積體電路開發選項

目前有許多種選項來開發用於功能安全系統中的積體電路。在標準中,並沒有要求僅採用符合規範的IC,而是要求模組或系統開發商挑選最適合用在其系統的IC。可用的選項包括:

注意,對於非針對IEC 61508開發的零件,安全指南可列入安全資料表或類似文件,以避免和遵循安全指南所開發的零件產生混淆。

選項1是對半導體製造商最昂貴的選項,但卻對模組或系統開發商最有利。應用對於IC展現的安全觀念若是和系統的安全觀念契合,則採用這樣的元件搭配模組或系統的外部評估,就能降低遭遇問題的風險。SIL 2安全功能的額外設計工作量可能達到20%或更高。除非半導體製造商即使在沒有功能安全的情況下也已採取嚴苛的開發流程,否則額外的工作量可能還會更多。

選項2能節省外部評估的成本,但影響還是相同。這個選項適合準備將模組/系統委外認證的客戶,而且IC在整個系統占極大的比重。

選項3最適合已釋出IC,提供安全資料表能讓模組或系統設計者取得額外的資訊,這些必要資訊讓他們進行更高層級的安全設計。其中包括如實際採用的研發流程、IC的FIT資料、任何診斷的細節、以及ISO 9001對製造廠房的認證。

選項4未來仍將是開發積體電路最常見的方法。運用這樣的元件來開發安全模組或系統,會需動用額外元件,以及模組/系統設計的費用,因為相較於單通道架構,元件並沒有足夠的診斷機制來因應雙通道架構。沒有安全資料表,模組/系統開發商必須做趨向保守的假設,並將積體電路視為黑箱。

此外,半導體廠商需要對標準發展自己的解釋,目前市場上已有業者就為此發展了ADI61508與ADI26262內部文件。ADI61508收錄IEC 61508:2010的7個部分,並針對IC研發解讀了相關的要求。

SIL 2/3開發

有時IC可依據SIL 3的所有系統要求進行研發。這意謂著IEC 61508-2:2010的表F.1中所有和SIL 3相關的項目都會被觀察,所有的設計審查與其他分析都在是SIL 3的規範下進行。然而硬體標準可能僅符合SIL 2。這樣的電路可歸類為SIL 2/3或SIL M/N,其中M代表硬體標準所有條件達到的最大SIL值,而N則是系統要求達到的最大SIL值。用兩個SIL 2/3 IC可建置出一個SIL 3模組或系統,因為兩個SIL 2項目在硬體標準方面同步升級至SIL 3,但就系統要求而言每個項目已達到SIL 3。如果IC僅達到SIL 2/2,那麼結合兩個這樣的IC也無法達到SIL 3,因為最高也只能達到SIL 3/2。

套用硬體標準到IC

一些例外狀況則是用一個IC建置大多數安全功能,此時很難為一個半導體元件指定SFF、DC、或PFM的極限。舉SFF為例,在SIL 3中,要求SFF必須高於99%,但這是適用於整個安全功能,而不是IC。如果IC達到98%,它仍能用來建置SIL 3安全功能,但系統中其他部分就必須達到更高的覆蓋率以能補償。積體電路的安全手冊或安全資料表必須公布系統層級FMEDA使用的λDD、λDU、以及λ。

理想的狀況下,IC要求可從系統層級分析得來,但通常並非如此,研發實際上是一種SEooC(參閱ISO 26262)或獨立安全單元。在SEooC方面,IC研發業者必須假設IC未來將如何運用在系統中。系統或模組開發商必須比較這些假設與其實際系統,看看IC的功能安全對於其系統是否足夠。這些假設可決定診斷機制建置在IC或系統層級,以及這樣做對IC層級的特點與功能所產生的影響。

加強積體電路防禦效能

系統必須兼具防禦能力才安全。目前只有IEC 61508與ISO 26262中所列的防禦相關指南向讀者提及IEC 62443系列規範。不過IEC 62443似乎偏向較大元件,像是整個PLC元件,而不是個別IC。好消息是,功能安全標準中大多數涉及消除系統失效的要求也適用於防禦。缺乏任何參考依據是相當耐人尋味的,因為在某些情況中,硬體可提供硬體信任根以及像是物理不可仿製功能(PUF),這對安全與防禦而言至為關鍵。

現有IEC 61508從IC研發一路涵蓋到煉油廠。雖然在包括機械與流程控制方面已有領域專屬的標準,在第2版IEC 61508的某些指南中已針對IC列出相關規範,但並沒有特別針對積體電路的標準。正因缺乏專屬的要求,導致開放各方自行解讀要求,以致客戶與外部技術顧問的期盼產生分歧。

這意謂著業界未來會傾向依循更高層級標準,為其IC制定特定行業專屬的要求。這類要求已廣泛見於如EN 50402這類標準,其中最特殊的,就是2016年的ISO 26262草案,其中新增的Part 11就是專門規範IC。

本文對於第3版IEC 61508的期盼,由於此標準大約會在2021年發表,因此將擴充與確定IC的規範。本文作者有幸參與IEC TC65/SC65A MT61508-1/2以及MT 61508-3,因此有機會參與這項工作。或許未來改版標準會新增Part 8,以專門用來規範半導體,使此產業具有連貫性,讓開發出的IC能符合所有產業的要求。儘管如此,未來標準仍不太可能納入IC製造商所需的一切,來讓他們設計出符合功能安全要求的IC。因為涉及安全、電磁相容等因素的要求,未來仍必須從系統應用的知識衍生而來。

(本文作者任職於亞德諾半導體)