除了在某些舊型個人電腦硬體及作業系統外,通用序列匯流排(USB)音效的普及率極高。由於具備健全的連結功能與理想的資料傳輸率,很多人可能會認為利用這種介面傳送高品質音效是輕而易舉,實際上,現今的USB音效產品是在背後克服大量的晶片與系統層級問題,解決時脈回復等各方面的棘手難題後,才有現今的成果。

USB音效設計挑戰不小

問題主要出在最終輸出元件,它負責把音效傳送到喇叭、耳機或需要主時脈的Line-out輸出插座,以便轉換出清晰的音效。主時脈必須有兩個獨立的特性:一是必須處在底層音效取樣率的正確倍數之上,即使出現時序錯誤,也不會錯失音效樣本或出現樣本重複的狀況;二為必須有夠低的抖動或相位雜訊,而且不會犧牲數位轉類比的處理效能,同時要滿足這些需求,帶給業者極大的挑戰。

一部分的難處在於,數位資料串流經過USB線傳送到另一端,接收端並不知道確切的取樣率。事實上,接收端只知道額定取樣率(Nominal Sample Rate)。此外,透過USB管線傳送的資料並沒有附上任何形式的時脈訊號。這點與大多數其他序列介面大相逕庭,其他介面要不是連帶傳送時脈訊號,不然就是資料結構經過特別設計,接收端可從鏈路擷取出時脈資料。

USB介面唯一的時脈資訊,就是每隔1毫秒(ms)就有一個特定類型的資料封包宣告一個訊框的起點,而接收端硬體會偵測到這個事件。發送端透過一個已知的方法根據系統時脈得知毫秒,原始音效取樣率也是採用這種方法。但稍後會討論一種例外情況。

有一種簡單的解決方法,就是把這個1kHz定速時脈放到鎖相迴路(PLL)乘法器,然後乘以需要的倍數以製造音效主時脈,以及所有依賴主時脈的次時脈。然而,在CD音樂系統中,取樣頻率為44.1kHz,傳統的音效數位類比轉換器需要一個比主時脈高二百五十六倍的取樣率,也就是11.2896MHz。

事實上,在一個單階式PLL中,若把輸入參考頻率乘以這麼大的倍數,會導致效能低落。限制因素包括迴路頻寬、參考贅餘訊號的拒斥及壓控振盪器的訊號抖動。此外,在這種情況中,對1kHz套用的乘法倍數並不是整數,這使得工作更加艱難。

從相位雜訊與贅餘訊號拒斥的角度來看,並置兩個複雜的乘法器迴路,是一種可行的方法。但這種方法耗電量極高,須要進行晶片與系統層級的類比設計,而且對於時脈頻率變化的反應速度過於遲緩。

USB音效鏈路使用的額定取樣率,在不同音軌間可能會快速改變,若要等待長時間才能穩定,可能導致效能變得不可靠。此類鏈路主要用在採固定頻率的錄音室數位音效鏈路等較不計較成本與尺寸的地方。

多年來業界開發出許多方法,發展出必要的音效主時脈且免除PLL乘法器的問題,並將這些功能整合到專屬的晶片組,安裝到為數眾多的USB喇叭、耳機和外接式音效卡。這些元件發揮外界要求其達成的功能,但不考慮額外矽元件空間或接腳數的問題,此一做法能壓低成本,並讓使用者樂於採用。

然而,這些特殊功能晶片恐怕無法滿足下一代USB介面的需求。媒體播放裝置及最新的平板裝置都建構在新型平台,採用新的作業系統,以USB作為標準化有線鏈路,用來支援各式各樣的配件與強化功能組件。現有的USB音效晶片組無法滿足這些系統的需求組合,對零件供應的基礎架構產生衝擊。更強效的USB音效功能愈來愈被微型化行動裝置所重視。

以數位格式從行動裝置中擷取出音效訊號,有許多好處。類比音效介面不再是系統音效品質的限制因素。音效系統或連結到播放裝置的配件,其製造商可透過電路設計來達到更優異的量測數據與音質表現。同樣重要的還有數位音效鏈路提高對分時多重存取(TDMA)干擾的抵抗力,還有抵抗行動裝置手機數據機對系統內音效播放通道中類比線路所產生的干擾。

市面上有許多微控制器整合USB元件連結埠,但卻沒有一款產品有必要的時脈產生與回復電路,來滿足現今聲音重現的高標準要求。有時候可運用外部的時脈淨化晶片或更精密的音效轉換器來解決這項問題。這類轉換器整合PLL或取樣率轉換器,藉以消除主時脈精準度/品質的落差。但這樣做又會讓系統退回到高成本、高電流消耗、高零件數量或是上述問題同時出現的窘境。此外,對於影片影像甚至是PowerPoint的簡報影片必須與音效維持時序一致的系統而言,調降音效的時脈並暫存在一個長記憶體緩衝區,並不合適於這種做法。

時脈回復跳脫設計框限

高度多元化的混合訊號元件問世後,這種問題變得很容易解決,這類元件將微控制器(MCU)、可編程數位邏輯及多元化的可調式類比電路整合到單一元件。其中一個例子就是賽普拉斯(Cypress)的新款PSoC3可編程系統單晶片(SoC)。

當出現系統層級的衝擊時,採用可編程微處理器(MPU)的設計可快速調適,因為新的程式碼和新的電路板會比新矽元件更快達成。但有時應用會要求專屬的週邊或處理支援,這些資源尚未整合到任何快速問世的微處理器中。

新問題首先浮現的解決方案,是微處理器的克難組合,結合現場可編程閘陣列(FPGA)的微處理器、可編程邏輯元件及各種專屬的固定功能晶片,其資源使用率通常只有一半,用來建置一些必要的特殊功能。結果產生過大的電路板及過高的材料清單成本,這對於剛萌芽的新市場產生極大的扼殺力。

高度可編程的系統單晶片架構提供一個替代方案。在這類元件中,晶片設計的工作僅限於初期,通常還未明確了解特定用途,針對類比與數位兩個領域建構一個更可調適化、更具彈性的架構。數位方面的彈性來自於內建模塊如通用數位模塊(UDB),能建置各種複雜的組合與序列邏輯功能,並獨立於主處理器核心。

專屬的協同處理器通常面臨的原生訊號處理作業如濾波等功能,都能納入到元件。在類比方面,可利用交換器與晶片內部元件來強化運算放大器與比較器,建構出各種類比模塊,其互連方式僅受限於使用者的想像力,彈性多重領域時脈樹進一步提高多元性。

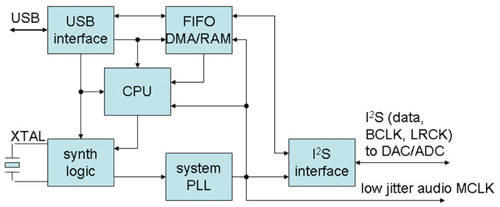

這些高度多元化的元件,其成本不一定接近單一功能專用元件的矽元件。但若僅須小幅度地修改,可編程元件通常都能提供最具競爭力的零組件成本,勝過於彈性較低的零件後續修改型(Patchwork)解決方案。快速的產品設計、重設計、加工,在過去數年確保可編程系統單晶片為電子產品設計做出重大的貢獻。這種解決方案的核心是USB音效時脈回復程序,其採用的基本組態如圖1所示。

|

| 圖1 USB音效時脈回復架構範例 |

可編程SoC縮短開發時程

可編程SoC的彈性化USB介面,讓系統能夠結合許多音效與控制通訊協定端點功能。可編程數位邏輯模塊建置一個頻率合成系統,能從一個穩定的晶體來源擷取出任何標準音效取樣率主時脈。在正常運作下,時脈會鎖定到接收端USB時基,使用訊框起點脈衝時序。系統時脈PLL透過彈性時脈路由框架整合到這個合成器。整個系統追蹤來源端取樣率,為系統的音效轉換器提供一個高品質的音效主時脈,並根據現代高品質音效系統的要求,提供理想的訊號抖動性能。

音效資料的時序通常跳脫緩衝區的限制,鎖定一個或多個標準I2S介面,配合聲道數量,連同可編程數位模塊進行建置。這種介面可連結到標準的音效數位類比轉換器、處理器或數位放大器。其他客製化介面亦可建置在這些模塊,例如Sony-Philips數位介面格式(S/PDIF)傳輸。整個流程可雙向運作,類比數位轉換器傳出的資料可透過USB連結埠再回傳。

有些USB音效模式要求區域時脈能夠微調以配合輸入端時脈,例如一個轉送遠端同步化音效資料流的訊源。可編程系統單晶片架構能夠在一種調適模式下運作,可微幅修正區域時脈,藉以提供必要的微調匹配功能。

固定功能微控制器無法滿足這種時脈產生流程的嚴苛效能要求,它們缺乏彈性的時脈產生系統無法調整至精準標的,抖動也不夠低,通常都是採用粗糙的增加/削減取樣模式。這種方法在電信領域可能管用,但在處理高品質音效方面就完全不能接受。

此外,專屬的USB音效介面元件(在材料清單成本中是除控制微處理器外另一個必有的項目)無法同時管理關鍵的雙向控制通訊協定傳輸,在這些最新媒體播放裝置中,這種控制機制能支援創新功能。

可編程SoC還能以低廉的成本提供先進的功能,例如某些系列的賽普拉斯PSoC3,透過嵌入式音效濾波引擎(數位濾波器模塊)為產品創造附加價值。分布回饋(DFB)能為USB音效接收訊號提供後製處理功能,像是響應等化與分頻濾波等。充裕的效能足以打造出冗餘的處理元件;在一對立體聲的每個聲道上至少能建置10秒的雙二階(Biquad)濾波器,為頻率響應提供精準微調的控制功能。

眾多高度可調整的解決方案,協助設計者省略大多數接合邏輯與類比監控電路。液晶顯示器(LCD)直接驅動能降低顯示器成本,再運用電容式觸控按鈕的感測功能,開發出美感十足的工業設計及現代化的人機介面。一個元件能作為新一代行動音效配件或消費音效裝置的核心,提供全數位化音效與資料交換技術的所有利益。可編程元件的彈性,意謂著必要的功能與介面都能依照需求進行整合。

固定功能元件的性能最終還是會追上可編程SoC,但採用一個理想的設計架構,運用高調適性SoC架構作為基礎,研發業者至少能搶先一步,在下一次遇到產品開發的問題時,能快速找到答案。

(本文作者任職於賽普拉斯)