從當今的智慧手機設計看來,不難發現它們都在使用超薄邊框設計來提高螢幕占比,而且使用金屬後殼甚至是一體式金屬機身設計,以減小智慧手機的厚度,並增加內置電池容量來保持續航力,這些設計都會導致用於手機天線的空間變得受限。而且從GSM模式的四頻到支援國際漫遊,以及全球通用手機的700MHz頻段(LTE B12/13/17/28)和高頻2.7GHz的B7,甚至對於不同場景的條件如使用者頭部或手等部位對天線性能的影響等因素,都會大幅增加天線的調試難度,若不考慮使用天線可調諧方案,確實很難滿足眾多營運商的OTA(Over-the-air)需求。

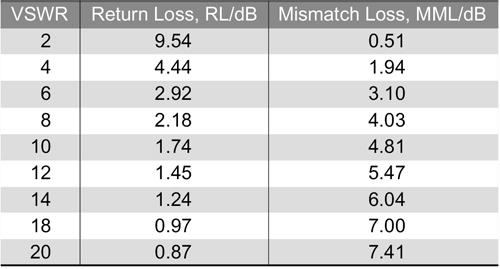

天線的效率對手機的接收性能,特別在訊號微弱的環境裡和手機的續航力有不可分割的關係。實際上,天線的諧振頻率跟其物理長度是相關的,諧振頻率是波長的四分之一及其倍數。由於手機的工作頻段增加,而且用於天線的空間及周邊環境條件變差,因此手機天線的頻寬並不能覆蓋所有的工作頻段,在某些頻段天線阻抗的電壓駐波比(VSWR)較差時,會導致一部分的訊號被反射到原點,無法從天線發射出去而造成失配損耗(Mismatch Loss, MML),電壓駐波比越大,失配損耗也就越大(表1),造成天線的效率變差。

|

| 表1 電壓駐波比(VSWR)跟回波損耗(RL)與失配損耗(MML)的關係 |

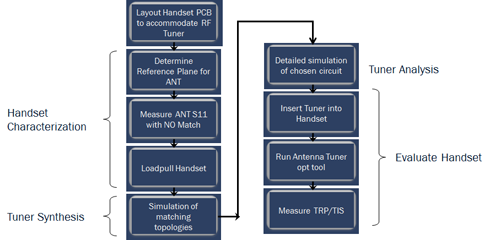

可調諧匹配設計流程

對於某些頻段,無法利用天線結構和形狀來增加天線的頻寬,只能透過加入可變電容的匹配電路來改善該頻段的電壓駐波比、減低失配損耗並改善天線效率。要決定在通路上使用哪一類型的可變電容,主要是需要考慮到其插入損耗(Insertion Loss, IL),因為如果PTIC的插入損耗過大,可能就無法發揮PTIC用在匹配電路上的優勢,原因在於使用可調諧匹配後,由失配損耗補償過來的增益,無法完全抵消整個可調諧匹配的插入損耗;使用開關型PTIC在通路匹配上就會出現這個問題,原因是開關型PTIC的Q值較低,插入損耗較大。以安森美半導體(ON Semi)的PTIC為例,基於鈦酸鍶鋇(Barium Strontium Titanate, BST,又命名為ParaScan)這種介電材料所製成,可透過電容兩邊的壓差來改變其介電常數,從而改變其電容值,並且是連續的,因此其PTIC的優點在於高Q值(80@1GHz, 50@2.5GHz)和低插入損耗,從而適用於在通路匹配上的串聯和並聯使用。

|

| 圖1 可調諧匹配的設計及測試流程 |

坊間一些天線工程師有時因缺乏射頻基礎理論,僅僅在有限的空間及環境下盲目地調試天線的形狀,往往不能在短時間內調出理想的效果,特別是在載波聚合(Carrier Aggregation, CA)的使用情況下,要同時兼願主載波和副載波,兩者在兩個不相連的頻段,調試時就更為困難。對此,半導體原廠藉由提供整套可調諧匹配的設計流程,使天線工程師能在短時間內瞭解使用可調諧匹配後對天線效率的改善程度,從而針對某些效果不理想的頻段執行天線結構和可調諧匹配之最佳化,達到服務供應商的嚴格測試要求。可調諧匹配的設計流程如下:

1. 利用PTIC元件,以L型或PI型匹配在PCB上布局。

2. 找出測量天線阻抗的參考面。一般以在可調諧匹配的輸出端最後一個裝置焊盤定立為測量天線阻抗的參考面。

3. 用網分在天線參考面的焊點測量天線的阻抗S1P。

4. 以在可調諧匹配的輸入端第一個裝置焊盤定立為Load-Pull的參考面,用Load-Pull調諧器找出最優的Load-Pull參數。

5. 在ADS使用不同的匹配拓撲結構做可調諧匹配模擬。

6. 對比不同的匹配拓撲結構在ADS的模擬結果,找出最佳的匹配拓撲結構及其物料清單(BOM)。

7. 按照模擬得出的可調諧匹配的物料清單,將裝置貼到PCB上。

8. 以手動或自動化軟體調試可變電容的供電電壓,找出最優的配置電壓。

9. 以此最優電壓配置,在暗室中測量TRP及TIS。

10. 採用原廠自主開發的ADS模擬工具包含PCB Layout、固定的電感和可變電容模擬模型,能夠模擬類比自由空間、頭/手等使用場景,以及CA情形。

很多天線工程師都有使用軟體進行模擬的經驗,認為模擬的結果跟實際測試結果有差異,原因在於流程2的天線阻抗S1P測量參考面不正確,導致測量的S參數不準確,而正確測量天線阻抗對模擬準確度是非常重要的。有關天線阻抗S1P測量方法,安森美提供有相關的技術文檔。此外,在天線調試的過程中,可能會有2組的配置電壓能將電壓駐波比或回波損耗調諧得很好,失配損耗很小,但這並不代表這2組匹配的插入損耗都是一樣,但透過軟體做模擬就能找出哪一組匹配的插入損耗是最小的。

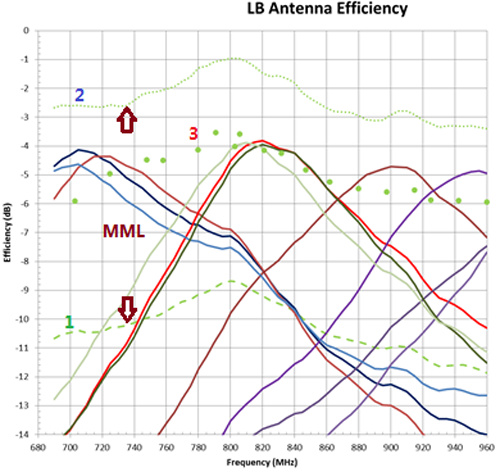

實際在通路匹配使用無源可調諧IC

圖2為使用安森美半導體PTIC在通路匹配的模擬及實測天線效率資料。曲線1為在不帶任何匹配的情況下,實測的天線效率(Antenna Efficiency),同時可在網分測量天線的電阻,從S1P文檔計算出天線的失配損耗,將實測的天線效率加上計算出天線的失配損耗,便相等於最佳的天線輻射效率(Radiation Efficiency),即曲線2。曲線3為在ADS模擬後得出的天線效率,模擬的天線效率比曲線2天線輻射效率差,原因是可調諧匹配有損耗(包括匹配電路的耗散損耗及匹配後還存在一些失配損耗)。其他的曲線為透過模擬得出的配置電壓值,在頻段可調諧匹配的實測天線效率,基本上實測試資料跟模擬資料能對得上,兩者之間的差異很小。

|

| 圖2 模擬及實測的天線效率資料 |

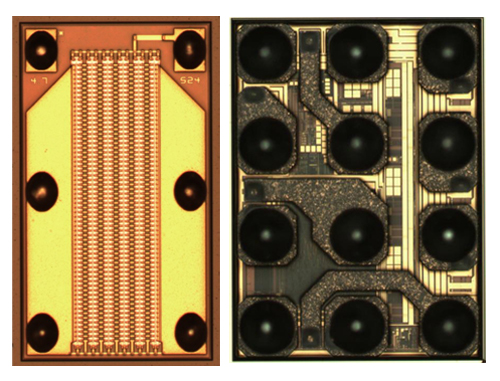

在評估PTIC元件時,除了前述的高Q值及低插入損耗外,不妨留意其電容可調諧範圍(配合如圖3的HVDAC控制IC)、線性度、是否具有連續的可調諧電容值、小封裝尺寸和低成本,以及有無多種電容值可供選擇。理想的天線可調諧方案能夠透過減少天線的失配損耗而大幅提高天線效率,以安森美半導體的PTIC為例,相較於其他可變電容技術,無論在並聯還是串聯時都處於700∼2700MHz範圍內,Q值較佳,而與高Q值的繞線電感配合使用後,整個可調諧匹配的插入損耗很小,適合用於通路上可調諧匹配。此外,其天線可調諧方案還具有低成本和小尺寸的優點,跟使用開關來切換不同的電容值相較之下,它擁有連續的電容值改變技術,因此更適合在通話中使用閉環自動調諧方案,以解決不同場景對天線效率的影響。

|

| 圖3 (a)GEN5 PTIC的Bump Side圖,(b)用於搭配的HVDAC控 制晶片TCC-303的Bump Side圖 |

本文將介紹在通路匹配(Matching)上使用無源可調諧積體電路(Passive Tunable Integrated Circuits, PTIC)的挑戰,無源可調諧積體電路的優點、設計流程,以及改善智慧手機天線效率的實際案例。

(本文作者任職於安森美半導體)