自從90年代初期起,因為影片壓縮有助於利用有限傳輸頻寬與儲存容量,來呈現高品質影片,因此在設計現代電子產品方面,也成為越來越重要的一環,在許多消費性電子(CE)產品中皆整合錄影與影片播放功能。

隨著多媒體風潮來襲,針對這類產品開發晶片的特殊應用積體電路(ASIC)、系統單晶片(SoC)以及特定應用標準產品(ASSP)設計團隊,就需要適合的方法,才能為其產品快速加入通過驗證與測試後的音樂或影片功能。

在實際作法上,業者可獲得各種通過測試、立即可用的矽智財(IP)模塊與韌體,結合多種數位影片與音樂的編解碼器。這些產品讓ASIC與SoC設計團隊在不須掌握新一代影片標準細部技術的狀況下,也能將現成的數位音樂與影片功能整合到設計中。此外,一旦新標準推出時,這些產品還擁有支援新標準的彈性。

影片的編碼作業,一開始是由攝影機運用電荷耦合元件(CCD)或互補式金屬氧化半導體(CMOS)感測器擷取影像,以某種畫面更新率,如每秒十五、二十五或三十格,連續擷取一連串的靜態影像,即畫格。這些感測器會擷取紅、綠、藍(RGB)三原色的畫素,之後再轉換成亮度與YUV格式色相的影像以利人眼觀看。

提升處理器效能 數位壓縮去蕪存菁

本文所討論的是數位影片壓縮法,採用有損耗的壓縮技巧,捨棄人眼察覺不出的部分影像,對靜態影像進行壓縮。其特性包括將影像分割成許多較小的畫素區塊、預測這些畫素區塊的數值、計算預測值和實際值之間的差距(餘數),以及把空域(Space Domain)的餘數轉換成頻域(Frequency Domain)的一連串係數

業界經常利用離散餘弦變換(DCT)把空域資料轉換成頻域。DCT最初被廣泛運用在JPEG靜態影像的壓縮上。在H.264/AVC數位影片標準問世之前,大多數影片壓縮機制都採用DCT來轉換8×8畫素區塊,但H.264/AVC則採用一種較簡單的整數型轉換法來處理4×4畫素區塊。

影像通常含有比較多重複出現的影像圖案,在頻域裡低頻的訊號更常出現,因此要把一個畫素區塊的頻域進行量化,使用較少位元表示係數時,因為多數高頻係數變成0,通常會連帶消除高頻率部分的係數,這也表示代表區塊所需的位元數得以減少。

對頻域係數進行編碼需要兩個步驟:第一,係數經過量化後成為離散值,利用感官式權重法來限制係數位元的數量。第二,量化後的係數再利用無損耗可變長度(VLC)編碼技術來進行壓縮,這種技術對常出現的係數分配較少的位元,因此進一步減少影片串流的檔案大小。

動態補償有效維持畫質 運算資源消耗大

VLC壓縮又被稱為熵編碼。在H.264/AVC壓縮法問世之前,霍夫曼編碼是影片壓縮最常用的熵編碼方法。H.264/AVC標準採用兩種熵編碼方法,稱為適應性可變長度編碼(CAVLC)與適應性二進制演算編碼(CABAC)。CABAC編碼需要較多運算資源,採用非整數的位元資料進行VLC編碼。在一定品質水準下,CABAC編碼的位元壓縮率比CAVLC提高約10%。CABCA提高位元壓縮率的代價,就是需要效能較高的處理器,使用較高時脈的處理器,處理器執行單元需要較高的平行運算能力,或兩者都需要。

靜態影像壓縮法的壓縮比可達10:1,並仍能維持優異的畫質。數位影片壓縮機制利用畫格間暫時性冗餘,達到大幅超越的壓縮比,可達200:1。當影片串流內容是一段影像沒有改變的靜態畫面時,影片壓縮機制僅須告訴影片解碼器重複最後一張影像畫面,並產生非常高的壓縮比即可完成。大多數連續影片畫格之間,至少都有一些畫素有變動,因此影片壓縮機制必須使用各種和動作有關的壓縮方法來處理不同類型的影片。

其中一種簡單方法是把前一個畫格減去目前畫格,再對兩畫格之間的差別內容進行編碼。Motion JPEG與Motion JPEG2000影片編解碼器就是使用這種機制。對於畫面中物體甚少移動的影片串流,這種壓縮法相當有效率。

其他更先進的機制則運用一種名為動態補償(Motion Compensation)的技巧,把畫格切成許多巨區塊(Macro Blocks),並搜尋前一個已編碼的畫格中是否有類似的巨區塊。動態預測影片編碼器後會編碼出一個動態向量,告訴影片解碼器先前已編碼的巨區塊會出現在新畫格的哪個位置。這種機制須利用相匹配的影片解碼器,把先前畫格的巨區塊儲存在畫面緩衝區中,以利重複使用。

動態預測使用的參考畫格,不一定得是前一個畫格。許多影片壓縮技巧可以不按顯示次序來對畫格編碼(尤其是非即時編碼的預錄影片),意謂中間影像畫格可以根據前一個畫格、未來的畫格,或混用兩者來進行編碼。不過,動態預測也衍生一個相當大的搜尋問題,亦即可能須要進行每秒數十億次的運算。

多核心硬體編解碼器 兼顧影像/音效資料處理

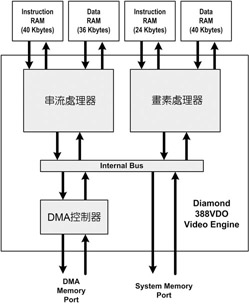

圖1中顯示的影像引擎,使用一個串流處理器以及一個畫素處理器之多微處理器核心,以及一個直接記憶體存取(DMA)控制器來執行影片壓縮與解壓縮演算法的平行處理模式。影像引擎核心內的串流與畫素處理器會分割處理影片壓縮作業,DMA控制器則把已/未壓縮的影像資料在兩個處理器之間及處理器與系統之間移動。影像引擎內的每個處理器都有自己專屬的區域指令和資料記憶體。

|

| 圖1 影片引擎之模塊圖表 |

這款影像引擎的串流與畫素處理器採用可配置處理器架構。串流處理器內加入額外的指令,能執行位元流分析與熵編碼作業。有些新指令採用彈性長度指令延伸集(FLIX),運用超長指令字(VLIW),每個指令能執行兩個獨立作業。而畫素處理器則是加入了單一指令多重資料(SIMD)指令,能同時針對多個畫素進行處理運算。

藉由加入到兩個處理器的指令集,影像引擎能在標準解析度(SD或D1)螢幕解析度以及每秒30畫格速率下,進行影片串流的解碼與編碼作業,所需時脈速度低於200MHz。目前支援的解碼器包括H.264 Baseline Profile、H.264 Main Profile、JPEG、MPEG-2 Main Profile、MPEG-4 Simple Profile、MPEG-4 Advanced Simple Profile、VC-1/WMV9 Simple Profile、VC-1/WMV9 Main Profile、RealVideo 9/10及China AVS等,而編碼器則包括H.264 Baseline Profile、JPEG、MPEG-4 Simple Profile與MPEG-4 Advanced Simple Profile等。

低時脈速度通常達到較低的功耗需求,選擇200MHz時脈速度讓設計人員能採用通用型低成本130奈米IC製程,若使用更先進的製程,則能達到更快的時脈速度,提供更高性能並降低耗電量。

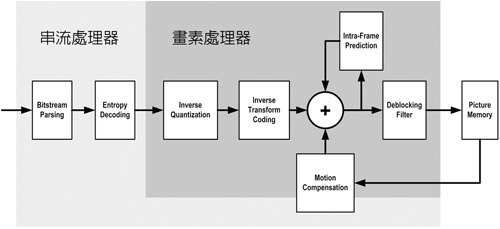

圖2顯示影像引擎在進行H.264/AVC影片串流解碼時的作業配置。串流處理器執行位元流的分析,包括分隔網路抽象層、圖像層與切片(Slice)層及熵解碼的作業。畫素處理器則執行逆向量化、逆轉換編碼、畫格間預測、動態補償及影像去區塊解算。串流處理器能協助畫素處理器執行動態補償作業。

|

| 圖2 影像引擎在執行H.264/AVC解碼時之作業分配 |

要留意的是,雖然可在一個處理器上執行所有解碼作業,但由於需要較高的時脈速度,故也須要採用較昂貴的製程技術。

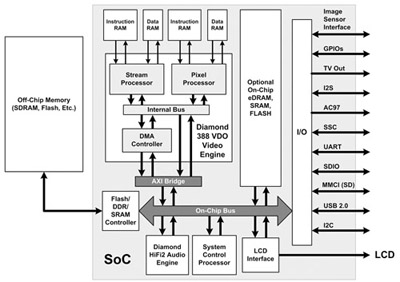

結合影像與音效引擎的SoC設計如圖3。此設計中主系統控制處理器控制SoC運作,並執行晶片內部與外部記憶體的程式,而晶片內部SoC音效解決方案音效引擎核心則提供數位音樂解碼功能。

|

| 圖3 結合音效/影片引擎之系統單晶片設計 |

音效引擎元件目前已被用在各種手機與數位電視SoC,能執行持續普及的數位音樂編解碼器。在許多設計中,這類音效引擎亦能作為主控制處理器。

影像引擎與音效引擎都顯示出處理器及其立即可運作的韌體,在各種複雜的晶片設計裡能架構為一個複雜、高效能、低功耗的功能模塊。圖3顯示運用模塊導向的設計模式,研發團隊能運用複雜、成熟的IP核心,快速組裝出極精密的SoC,之後再運用程式碼來設定這些SoC,為市場開發出各種獨特產品。

(本文作者任職於Tensilica)