隨著消費者對各種通訊設備的性能要求越來越高,資料傳輸速度也在不斷地向上攀升。像雲端計算或網際網路計算等須要無縫存取大型資料中心的新技術趨勢,使得對頻寬的要求也大幅增長。因此,資料網路和電信基礎設施系統設計人員面臨的壓力也越來越大,因為他們必須在未來3∼5年間開發出能夠把傳送速率從目前的10Gbit/s提升到25Gbit/s的系統。

這條物理鏈路中所有的利益相關者,包括原始設備製造商(OEM)、主動和被動元件供應商、矽元件供應商、印刷電路板(PCB)與原始電纜供應商,以及外包商,都必須比過去更緊密地合作。

無疑地,這種大規模的改變將帶來嚴峻的技術挑戰。例如在電信、資料通訊、網路與其他各種產業中,高速和寬頻系統的迅速流行及商業用戶數量的急劇增加,都會造成嚴重的潛在訊號完整性問題。這些問題包括訊號損耗和雜訊等傳統挑戰,以及電磁干擾(EMI)、功率完整性和功率效率等新情況。

隨著每一條高速串列鏈路對系統頻寬需求的增加,鏈路(或埠)的數目也在不斷地增加。當物理鏈路中訊號速度和埠密度要求同時增加時,訊號損耗、串音、反射和模式轉換等問題會降低系統的性能,並使問題變得更加難以解決。

對系統設計人員來說,好消息是現在有較以往更加可行的預測分析工具,能將設計風險降至最低,並縮短產品上市的速度。元件供應商利用這些工具來為設計人員提供準確的、具有可預測性的元件級模型與端到端通道模型,以便讓他們找出系統在價格與效能之間的最佳平衡點。

取得最佳性價比

在資料傳輸系統升級時,必須考慮到商業應用環境中的實際情況。高速串列鏈路系統設計人員必須找出每一個關鍵元件在價格與效能之間的最佳平衡點。如果採用成本高昂且超過設計需求的元件,系統成本可能會太高,導致沒有人願意購買。隨著系統主機殼如刀鋒型伺服器、核心路由器或交換機,出貨的元件必須是可升級、可擴展到25Gbit/s的產品,同時還必須確保這種可擴展性成本與所需系統性能間的平衡。

幸好,新標準將使這種元件的選擇過程變得更加容易。國際電機電子工程師學會(IEEE)、光纖互連論壇(OIF)和InfiniBand貿易協會(IBTA)等產業組織,目前正在加緊定義25Gbit/s通道標準。這些標準定義合格/不合格的標準和通道性能限制,以便為系統設計人員提供相關的指南。

設計人員必須針對訊號路徑上的每個元件進行分析,以確定其對鏈路性能的影響。透過電氣、機械和商業的方式,將這些通道元件最佳化,可獲得更好的系統設計。這些通道元件包括Tx/Rx矽封裝和球閘陣列封裝(BGA)通孔、背板和子卡印刷電路板疊層與通孔、經匹配的連接器及直流阻隔(DC Blocking)等。

降低開發風險

系統設計人員如何才能確保其開發的系統不僅可以正常運作,而且也具有成本效益呢?他們應該進行鏈路分析、功率完整性分析、電磁干擾分析等三項關鍵的降低風險分析,以確保其投資能帶來相應的投資報酬率。

市面上都有相應的預測分析工具和測量技術來評估上述的每一個關鍵領域。一些擁有良好信譽的業界供應商也可以提供這類型的分析。例如莫仕(Molex)與業界的原始設備製造商合作完成這種分析,以確保通道內所有的互連元件都已針對25Gbit/s而優化。

鏈路分析抽絲剝繭

|

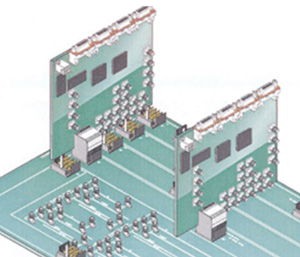

| 圖1 對鏈路中每一個元件都要進行模型和測量靈敏度分析,以確保能在價格與效能間做出最好的決定。 |

被動和主動(包括矽片)鏈路分析可以幫助確定每一單獨的通道元件是如何影響鏈路總體性能。藉著分析每個元件的靈敏度,就可以獲得更好的性價比(圖1)。

每一條資料傳輸通道都是獨一無二的,通常要求有專門的設計。雖然有各種標準可指導設計,但資料傳輸系統的實際價值在於它執行必需任務時的性能水準。鏈路分析可以幫助設計人員決定應該使用哪些元件來建立一個最佳的、具成本效益的高速資料傳輸系統。

好消息是,過去十多年間,用於鏈路分析的預測分析工具不斷地在改進,越來越好。以往,鏈路分析一般是被動的,不包括通道中的關鍵矽元件。今天,AMI工具可以讓更多的通用平台用來分析通道中的主動和被動元件,這些工具都帶有一個關於不同矽晶片、印刷電路板材料、連接器解決方案的選單。

另一項好處是,這些通用主動平台讓系統設計人員能夠對多家矽晶片供應商的產品進行比較,獲得鏈路的合格/不合格的位元誤碼率(BER)結果。這樣一來,設計人員就可以避免犯下代價高昂的錯誤。

例如,莫仕工程師在執行鏈路分析時,會選擇有代表性的極端狀況(Corner Case)來確定通道性能,包括多種最差情況的獨特案例。然後,進行被動通道分析並執行靈敏度分析,以確定適當的互連解決方案、印刷電路板材料、原始電纜類型和設計技術。

接下來,利用這些AMI平台工具執行一個主動鏈路分析,為客戶提供其通道的BER值。其目的是在於協助設計人員把產品設計時間縮到最短,並加快產品上市的腳步。

最後是執行元件模型和通道模型的相關性研究。莫仕開發出原型相關性平台來測量極端狀況,以證明這些模型滿足測量要求,並能在現場工作。

分析功率完整性

第二項關鍵分析是印刷電路板功率完整性。IC使用的電壓數目越來越多,功耗急劇增加,這使得提高功率完整性變得十分困難。此外,設計人員希望減少層數以降低成本、改善通孔效應,並開發出間距更細且可在銅面(Copper Plane)上打孔的球閘陣列封裝設計(埠密度大),但這樣一來,會讓直流電壓和電流的供應變得困難。要在10Gbit/s系統中實現功率效率已是一件相當不容易的事,因此支援25Gbit/s系統將特別需要具有創新性的新穎設計。

要在一段長距離上驅動25Gbit/s的訊號傳送速率,需要額外的電源。另外,電源的波動會影響到矽片封裝中的訊號延遲預算,並且可能在印刷電路板中產生雜訊。新的模型建立工具可實現板級功率完整性分析,其他的新工具則能夠分析供電與配電系統及其對系統級溫度升高的影響。這些工具以不同的網格密度顯示可能導致晶片過熱的熱區(Hot Zone)。這些熱區可能需要印刷電路板採用額外的導熱銅片或纜線來散熱。

新興的電源和冷卻技術,結合支援這些更大電流負載和更高資料率的最優化互連系統,將有可能在市場上流行起來。

電磁干擾分析挑戰不小

電磁干擾分析是三個領域中最具挑戰性的一種。電磁干擾或射頻干擾(RFI)是因為電磁傳導或由外部源發出的電磁輻射所引起的一種干擾,可能導致電路中斷或降低電路性能。

雖然有多款預測分析的電磁干擾模型建立工具正在逐漸成形,但功能仍遠不及鏈路分析和功率完整性工具。因此,電磁干擾分析仍須在電磁干擾艙內對實際系統進行測量。由於每個資料傳輸系統都是獨一無二的,所以必須對每個系統進行分析和測量。例如,莫仕的元件都要經過最優化研究,其中包括模型的構建/測量週期,以確保最佳的元件性能和最小的電磁輻射。

莫仕使用由ETS-Lindgren開發的SMART 1000 Mini-Reverb艙之客製化衍生產品來測試硬體元件。該測試裝置有兩個艙室,分別用於發射(嘈雜)和接收(安靜)應用。每個艙室都有一個調諧器,分別由頻率範圍為1~18GHz及18~40GHz的步進電機驅動。確定地板完全密封,天花板完全開放,然後對互連解決方案進行測試,以驗證該設計的電磁干擾遮罩性能。

這種分析有助於確保莫仕解決方案在原始設備製造商的環境中能夠提供足夠的電磁干擾性能。在某些情況下,實際的原始設備製造商系統卡和主機殼是在莫仕的電磁干擾艙內進行測試,以確定其符合要求。

對高速內部和外部輸入輸出(I/O)應用,以及一些內部板對板應用而言,這種類型的測試是很重要的。為儘量減少內部計算設備的電磁干擾的潛在影響,這類測試更是重要。如果一個設備會產生大量的電磁干擾,它就很可能不符合某些美國聯邦通訊傳播委員會(FCC)標準。

合作夥伴攜手共創榮景

這條物理鏈路上的所有利益相關者彼此間已締結一種強而有力的合作夥伴關係,共同為25Gbit/s系統開發新的元件和解決方案。莫仕則是把焦點集中在藉由策略性合作夥伴關係開發互連解決方案,以確保完整解決方案的開發。這些合作夥伴主要包括業界的原始設備製造商、矽產品供應商、印刷電路板材料廠商及合同製造商。現在市面上已經有支援25Gbit/s同類最佳性能的設計工具與技術。將這些產品導入服務,需要業內所有合作夥伴的共同努力。

(本文作者任職於莫仕)