一般認為,混合波束成形技術將是在微波和毫米波頻率下操作的5G系統之架構選擇。在這種架構中,它採用了一種數位(MIMO)和類比波束成形的技術組合,以克服高路徑損耗並提高頻譜效率。

如圖1所示,一種m個數據串流的組合會被分流成n條射頻(RF)路徑,而在自由空間(Free Space)中形成波束,使得天線單元(Antenna Element)的總數成為m×n的乘積。數位串流可以若干方法組合,無論是將所有能量引導到具有高層MIMO的單一用戶,還是支援多用戶MIMO的多個用戶。

|

| 圖1 混合波束成形的方塊圖 |

在本文將以探討一個大規模天線陣列的簡單例子,來檢視毫米波無線電的最佳技術選擇。深入探究毫米波系統中無線電部分的方塊圖,首先看到的是一個連接到多條RF路徑的經典外差結構(Heterodyne Structure)。在這些路徑中,本文採用移相器(Phase Shifter)和衰減器來形塑波束。

歷史上,毫米波系統一直都是以分離式元件來打造的,因而使得它的體積大,成本也居高不下。傳統的系統是由互補式金屬氧化物半導體(CMOS)、SiGe BiCMOS和砷化鎵的組合所構成的,每一種技術都是經過精挑細選,以提供最佳的性能。例如,數據轉換器現在是以細線(Fine Line)CMOS製程來開發的,使得取樣率可以在GHz範圍之內。升頻轉換和降頻轉換及波束成形功能可以SiGe BiCMOS有效地實現。根據無線電的需求,功率放大器和低雜訊放大器可能會需要GaAs,但如果SiGe BiCMOS能夠滿足要求,則可以實現更高的整合度。

對於5G毫米波系統而言,有一項要求是要將射頻晶片(RFIC)安裝在天線基板的背面上,從而導入了一種外形尺寸的需求,而帶動了積極的整合。理想情況下,單一波束的整個方塊圖應整合在單一的IC中,至少應將升頻轉換器和降頻轉換器與射頻前端整合在一單一的射頻IC之上。整合的程度和技術選擇的等級在一定程度上是視應用的需求而定的,如接下來所要分析的實例分析中看到相同。

實例分析︰EIRP基地台天線系統

針對這次的分析,本文考慮了一種典型的基地台天線系統,等效全向輻射功率(Equivalent Isotropically Radiated Power, EIRP)的要求為60dBm。本文做了以下的假設:

該模型是以8個數據串流為基礎,連接到不同數量的射頻鏈。而模型中的天線數量則是以8的倍數增減,最多有512個單元。

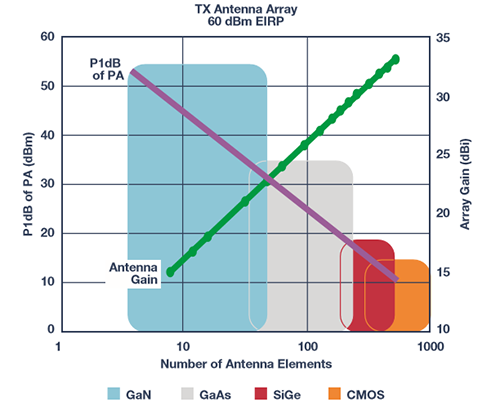

在圖2中,說明了功率放大器的線性度如何隨著天線增益的增加而變化。請注意,由於開關損耗的原因,放大器的輸出功率比出現在天線的輸出功率高2dB。隨著單元添加到天線,指向性增益(Directivity Gain)會隨著對數x軸而呈線性地增加,隨後,也減少了每一個個別放大器所要提供的功率貢獻量。

|

| 圖2 天線增益與功率放大器輸出位準需求之間的關係圖 |

為了便於說明,本文在曲線之上覆蓋了一份技術地圖,以指出在整個天線單元的範圍之內,哪種技術是最佳的。請注意,在各個技術之間會有重疊的現象,因為每一種技術都可被一個範圍之內的幾個數值所採用。此外,一個範圍之內的性能也可以一種已知的技術來實現,這取決於製程和電路設計實踐的方法。對於單元數很少的情況,每條鏈中都需要高功率功率放大器(PA)(功率氮化鎵(GaN)和砷化鎵(GaAs)),但是當單元的數量超過200時,P1dB會在20dBm之下交叉,而將該值帶進到矽製程可以滿足的範圍之內。當單元的數量超過500時,PA的性能便會落在以目前CMOS技術可以實現的範圍之內。

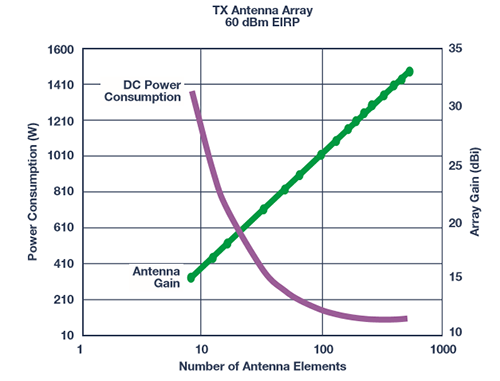

現在,考慮當添加單元的天線Tx系統功耗,如圖3所示。如所預期的一般,功率消耗與天線的增益成反比,但會達到一個極限。超過幾百個單元時,PA消耗的功率不再在其中占有主導地位,導致遞減轉回(Diminishing Returns)。

|

| 圖3 天線增益與天線Tx部分的功率dc功率消耗之間的關係圖 |

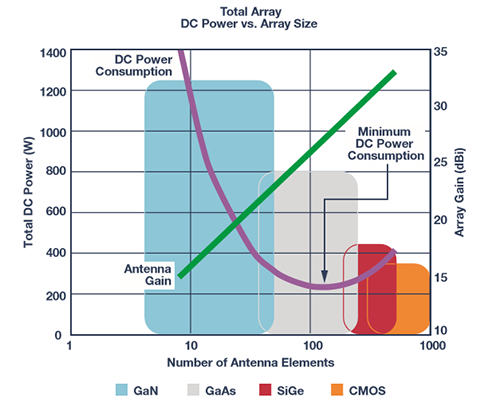

整個系統的功耗如圖4所示(發射器和接收器)。如所預期的一般,接收器的功率會隨著RF鏈的添加而呈線性地增加。如果將下降中的Tx功率曲線重疊在增加中的Rx功率曲線上,就可觀察到一最小功耗的區域。

在這個例子中,最小值出現在大約128個單元之處。回顧圖2中所介紹的技術圖,為了實現EIRP為60dBm,且有128個單元,則最佳的PA技術是GaAs。

雖然採用GaAs PA將使得EIRP為60dBm的天線具有最小的功率消耗,但這可能無法滿足系統設計的所有需求。記得在稍早之時,曾經提及到在許多情況下,要將RFIC安裝在天線單元的λ/2間距之內。使用基於GaAs的發射接收模組可提供必要的性能,但它不能安裝在尺寸限制範圍之內。為了能夠利用GaAs發射接收模組,有必要採用替代的封裝和路由方案。

有一種優先採用的選項是增加天線單元的數量,以容納整合在RFIC之內的SiGe BiCMOS功率放大器。在圖4中顯示,SiGe放大器可藉由倍增單元的數量到大約256個來滿足輸出功率的需求。儘管功率消耗會略微增加,但可以採用SiGe BiCMOS RFIC,以放進天線單元(在28GHz情況下)的λ/2間隔範圍之內。

|

| 圖4 整個天線陣列直流功率消耗與天線增益之間的關係圖 |

在將這種趨勢延伸到CMOS,顯示CMOS也是有能力實現整體60dBm的EIRP,但從技術圖中可以看到,這將需要額外倍增天線單元的數量。有鑑於此一解決方案將導致額外的尺寸和功耗,所以考慮到當前的技術限制,本文不認為CMOS這種做法是一可行的選擇。本文的分析建議,考慮到功耗和尺寸整合這兩項因素,EIRP為60dBm的天線的最佳實現方法是利用SiGe BiCMOS技術來達成,以利RFIC整合。而如果考慮用戶終端設備(CPE)所需要的較低功率天線,則CMOS當然是比較可行的選擇。

雖然這次的分析是基於當前可用的技術,但在毫米波矽製程和設計技術方面也都有長足的進步。可預期矽製程未來將可發展出功率效率更好和輸出功率更高的能力,這將能夠實現天線更小的外形尺寸和經過改善的優化。

隨著5G到來的時間越來越迫近,它將繼續為設計工程師帶來多項挑戰。但在決定毫米波無線電應用的最佳技術解決方案時,考慮清楚訊號鏈的所有面向及不同IC製程的各種優勢,將十分有幫助。

(本文作者為ADI通訊事業群技術長)