每位積體電路設計人員在設計過程中必須克服的一項挑戰是,針對不同半導體晶圓廠或技術設計產品,不論設計者進入不同的受雇公司,或公司基於生產策略新設立晶圓廠,最終的結果都必須為了新晶圓廠或製程而將現有設計做轉換。

新晶圓廠挑戰加劇

針對不同晶圓廠開發產品的其中一項主要工作是,累積使用新設計套件的經驗。設計套件包含一組工具,以及文件說明元件布局、處理、建立模型、測試、可靠性及統計數據的能力與限制,其主要目的在於提供所有將生產的元件適用的完整設計環境。

這個環境包括設計規則、設計規則檢查演算法和元件模型。代工服務供應商長久以來均針對客戶提供穩定且妥善開發的設計套件,不過,射頻(RF)及微波裝置通常需要額外的自訂設計套件,才能實現獨特的架構,這在代工服務中是一大挑戰。

|

| 圖1 為新晶圓廠開發特定適用的元件模型,是多重供應策略發展的一大挑戰。 |

另外,使用雙極性場效電晶體(BiFET)製程的代工,使得問題更加複雜。砷化鎵(GaAs)電路設計人員一直尋求矽晶片設計人員運用BiCMOS技術所達到的彈性,這是由於發揮雙極性電晶體和場效電晶體(FET)的最佳特性所致。導入BiFET技術能夠將異質接面雙極性電晶體(HBT)與含磷化銦鎵(InGaP)的擬態高速移動電子電晶體(pHEMT)整合於單一GaAs晶粒,對於GaAs IC設計人員能夠發揮的彈性更大,不過,在針對多個BiFET晶圓廠設計產品方面也造成其他挑戰(圖1)。

手機市場爆量 晶圓擴增需求在即

對於資料網路而言,全球採用智慧型手機的趨勢造就GaAs功率放大器的市場持續成長,Anadigics所生產的功率放大器便是其中一例。有鑑於此,考量以現有晶圓廠使用的相同製程建立新生產製造設施的選項後,Anadigics決定將增加晶圓廠加入生產製造計畫中,開始採取多重供應來源策略。這將使得整體產能發揮極大的彈性,同時維持對於技術及產品開發極為有益的內部固定產能。

採取新的多重供應來源策略後,Anadigics接著面臨實作的挑戰。公司擁有運用本身150毫米InGaP GaAs晶圓廠開發獨特產品的追蹤紀錄。Anadigics率先開發和實作商業化BiFET製程量產(InGaP-Plus),並且運用BiFET製程開發出許多世代產品。

在2009年第四季,Anadigics與穩懋半導體宣布達成GaAs積體電路設計製造的策略協議。此協議旨在運用穩懋半導體的GaAs晶圓廠生產多款新系列產品,而Anadigics本身的晶圓廠則繼續生產其他新系列產品及現有產品。

穩懋半導體提供以InGaP作為發射材料的HBT技術生產發射極的代工服務。穩懋半導體獲選的原因,在於HBT製程所生產的BiFET產品在射頻功率、效能、線性度及可靠性等方面,與Anadigics的InGaP-Plus BiFET製程類似。自從2009年達成策略協議後,Anadigics與穩懋半導體即共同實現Anadigics工程人員運用穩懋半導體晶圓廠,推出3G及4G射頻功率放大器裝置。

過程中,由穩懋半導體針對所需的BiFET製程將設計套件提供給Anadigics,Anadigics的設計人員得以將本身晶圓廠製程導入穩懋半導體的製程。不過,一些裝置結構未能完全符合Anadigics本身晶圓廠生產的裝置所具有的特性。

經過廣泛的分析後,確定穩懋半導體製程與Anadigics的BiFET製程兩者間的差異,以及Anadigics的新設計中採用的多個獨特裝置結構導致產品效能特性有出入。解決方法是擴充穩懋半導體的設計規則,納入所需的裝置結構。Anadigics與穩懋半導體雙方的技術設計人員共同開發測試適用於Anadigics產品開發及穩懋半導體製程的設計規則。

元件模型開發聲聲催

在共同合作的過程中,其中一個必須克服的挑戰是,開發以穩懋半導體之BiFET製程生產的特定產品適用元件模型。電晶體裝置模型可擷取裝置的電子運作方式,以便設計人員能夠模擬全部電路和產品的整體效能。Anadigics的重點在於電晶體在特定的大訊號射頻條件下所呈現的效能,其中包括這些電路元件間以及對於這些電路元件的金屬互連所具有的阻抗和寄生電容。

除了準確的裝置模型外,設計人員通常也使用「經驗法則」或已知方法來設計產品,這通常是以使用可預測之裝置模型的可行製程所得到的經驗為依據。因此,為了決定全部產品的設計所需的最佳裝置結構,必須先在穩懋半導體晶圓廠以測試結構進行工程晶圓製程,這使得Anadigics技術團隊能夠界定測試結構的特性,並定義符合公司效能和布局需求的新模型。團隊尤其使用此特性界定來支援FET和HBT的全新可擴展模型。

產生新模型後,這些模型必須加入Anadigics的IC設計人員使用的模擬工具專屬的設計套件,也就是安捷倫(Agilent)的Advanced Design System(ADS)。ADS設計套件包含在所支援製程中設計與模擬IC所需的一切資訊,其中包含裝置定義和相關的模型檔案與次電路、對應的原理圖符號,以及簡便的元件庫與調色盤清單中使用的符號。

更新設計規則手冊

穩懋半導體測試新設計規則合格後,也同時更新官方的設計規則手冊。這本手冊包含一系列數值表示和文字敘述的實體配置規則,設計人員必須遵循這些規則,才能確保產品能夠大量生產。由於設計規則適用於特定的半導體製程,因此新的和轉換的IC配置必須經過更新,才能符合目標製程所有的規則。

雙方共同定義和記錄新設計規則後,設計規則檢查(DRC)軟體便須要更新。DRC是廣泛的自動化驗證,可確保特定IC的實體配置符合所有設計規則。樣品裝置配置的自訂DRC回歸測試套件,也可用來確保DRC軟體的任何變更不會對於其他未變更的設計規則造成任何假性回報違規。經過適當製作的設計規則手冊,加上穩定且妥善實作的DRC軟體,不僅有助於達到更高的大量生產產能,而且可縮短設計週期,並加速上市時程。依據設計手冊和測試套件驗證新的DRC後,就在現有工程和模組上執行,以確認能夠識別設計違規。

反覆的過程

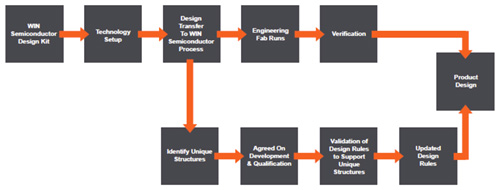

建立新裝置模型及設計套件是一個反覆的過程(圖2)。由於新的裝置及架構是依據協定的開發和審核標準所建立,因此也須要針對提議的設計規則進行驗證。這類驗證可確保設計規則支援所需的裝置和架構,並且能夠達到預期的結果。因此,完成初始的裝置模型並更新設計套件後,隨即重複進行此程序將模型、設計手冊及DRC軟體最佳化。

|

| 圖2 建立新裝置模型及設計套件 |

維持效能與可靠度

衡量雙方合作的結果成功與否的標準在於,是否能夠開發可在穩懋半導體生產的產品,同時使Anadigics本身的晶圓廠生產的產品維持一貫的效能和可靠度。第二個標準是新產品的設計簡易度為何。Anadigics希望讓內部的設計人員能夠輕鬆建立運用穩懋半導體晶圓廠生產的裝置和產品,就如同運用Anadigics自身的晶圓廠一般容易。

Anadigics揀選一個採用該公司獨家High-Efficiency-at-Low-Power(HELP)技術的新產品系列作為穩懋半導體大量生產的第一組產品。設計人員運用Anadigics極為成功的HELP3 AWU660x系列功率放大器中既有的架構,設計新的功率放大器HELP3DC系列。HELP3DC系列可達到與HELP3產品相同的優點,差別在於此一系列專供直流對直流(DC-DC)轉換器使用。

運用新的設計套件後,Anadigics設計人員能夠重新建立HELP3產品系列使用的獨特電路配置。穩懋半導體生產的新款HELP3DC產品確實達到Anadigics生產的HELP3產品一貫的效能和可靠度。

擁有更多生產製造彈性

多重供應來源生產的實作須要Anadigics與穩懋半導體雙方共同緊密合作。由於運用Anadigics的工程技術、裝置模型建立和設計長才,以及穩懋半導體的製程與技術專業知識,顯著強化的設計套件就此成形。如此的過程,最終的成果是能夠使針對穩懋半導體設計的新產品達到與Anadigics內部生產的產品相同的效能,並且為客戶提供預期的一貫效能及可靠度。最後,多重供應來源生產讓Anadigics有更多的生產製造彈性可持續滿足客戶的需求。

(本文作者Dan Stofman為Anadigics自動化製程設計總監、Kevin Chang為晶圓研發資深技術人員)