長程演進計畫(LTE)是無線寬頻的最新第三代合作夥伴計畫(3GPP)標準,打破當今蜂巢式無線網路固有的模式。相較於前代全球通用行動電信系統(UMTS)和全球行動通訊系統(GSM)標準,LTE採用高效率光譜射頻技術,並大幅簡化其架構。LTE系統的無線接入部分Node-B,是連接無線電和整個網際網路通訊協定(IP)核心網路之間的邊緣設備。這種架構無法監測UMTS中間鏈路上的元件,必須透過無線電介面才能有效測試LTE的網路元件。

|

| 圖1 在LTE測試環境中,模擬器可取代無線電磁區,或為核心網路提供測試介面。 |

這也是Prisma Engineering的LSU UeSIM LTE專案設計組所要解決的問題。該模擬器針對所有LTE測試需求提供全面性的解決方案,協助網路設備設計人員對無線介面和核心網路進行測試和監控(圖1)。一個這樣的硬體平台在每個磁區中可模擬多達一千零二十四個使用端設備。在無線介面上所進行的工作負載(Load-and-stress)和功能測試(Functional Testing)包含完整的LTE堆疊和應用,而其射頻前端則採用本地多重輸入多重輸出(MIMO)技術設計,可支援5MHz、10MHz、15MHz和20MHz等多種不同頻寬。

該高階模擬器的核心採用三個賽靈思(Xilinx)Virtex-5現場可編程閘陣列(FPGA),可支援高階軟體無線電重新配置(Radio Reconfiguration)。Prisma Engineering設計組發現,若使用功能強大並可重新編程設計的架構,便能更方便地在同一個開發板上靈活應用多種無線接入標準。

目前有LTE Test Manager和Quick GUI兩種用戶測試工具,LTE Test Manager主要針對LTE設備廠商,而Quick GUI主要針對LTE網路營運商。Quick GUI提供通過與未通過測試方案,而Test Manager則可進行更為複雜的分析。

LSU UeSIM LTE架構簡介

支援MIMO運作的LSU UeSIM LTE模擬器,採用CompactPCI無線電模組標準架構,其中包含一個協定處理單元(Protocol Processing Unit, PPU)範本、一個軟體定義無線電(SDR)和兩個無線電模組。

|

| 圖2 LSU軟體無線電卡上的賽靈思Virtex-5 FPGA和TI DSP |

採用英特爾(Intel)技術的PPU機板是主要的處理器卡,能管理多個SDR範本,改善負載-應力效能。軟體無線電機板是專門為擴充賽靈思先前的LSU系統在無線電介面的運行效能所設計(圖2),而CompactPCI無線電夾層卡則負責提供不同標準射頻的發送/接收功能如GSM(850和900MHz;1.8和1.9GHz)、LTE(700MHz,2.1、2.3、2.5和2.6GHz)和全球微波存取互通介面(WiMAX)(2.4、3.5和5GHz)。

SDR卡整合LSU軟/硬體

SDR卡是一種整合LSU軟/硬體環境的高效能平台,用於提高系統與基頻(CPRI/OBSAI)、無線電介面和兩者之間的連接功能。該卡以特定頻寬內不同的外部無線電模組支援各種無線標準,如GSM/GSM增強型數據傳輸(EDGE)、UMTS、高速封包存取(HSPA)、WiMAX和LTE等。

Prisma採用三個德州儀器(TI)的1GHz數位訊號處理器(DSP) TMS320C6455、亞德諾(ADI)的類比數位轉換器(ADC)AD9640與數位類比轉換器(DAC)AD9779,完成使用賽靈思FPGA的SDR卡設計。時脈網路採用亞德諾的AD9549,能為FPGA、DSP提供極高彈性的時脈基礎。

LTE加工數據路徑一分二

Prisma將LTE加工數據路徑分為兩大部分:在FPGA內實現的射頻前端,以及在DSP內實現的物理資源配置和資料控制通道。

在上行鏈路方面,DSP負責處理媒體存取控制(MAC)層到實體層的交換,以及實體層某些功能的操作。其中包括編碼(Coding)、交錯(Interleaving)、加擾(Scrambling)、訊號調變(Symbol Mapping)和子載波分配(Subcarrier Allocation),以提供參考訊號(導頻)、資料來源和通道控制。離散傅立葉轉換(DFT)函數負責根據SC-FDMA標準完成來自不同終端的資料轉換。該系統使用外部記憶體介面(EMIF)把每個正交分頻多工(OFDM)符號都發送到FPGA的上行鏈路。

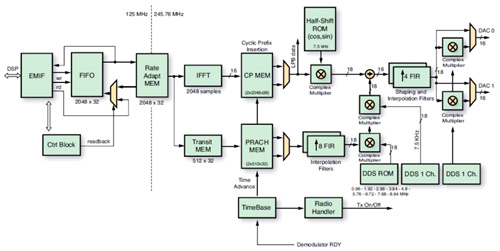

該FPGA將資料速率從125MHz(DSP EMIF時脈介面)提升到245.76MHz(FPGA加工速率),然後FPGA再執行一系列操作:二千零四十八點反向快速傅立葉轉換、循環字首插入、PRACH資料通道插入、7.5kHz頻率下轉換OFDM光譜符號的半移位元函數、通道整形與內插濾波以及24MHz頻率下的中頻(IF)轉換。隨後該元件以122.88MHz的時脈頻率把中頻資料發送到DAC,同時射頻卡再將類比訊號轉換為射頻訊號,發送至功率放大器。

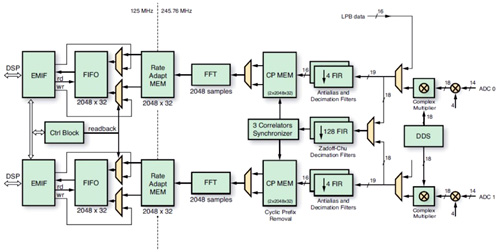

而下行鏈路方向上,在LNA放大、可編程式設計增益和轉換階段完成後,射頻卡再將接收到的中頻資料發送到SDR卡(140MHz)。而ADC將以122.88MHz的頻率對類比資料進行二次採樣,FPGA則負責處理最終到基頻的17.12MHz頻率轉換。該資料與兩個單輸入、單輸出通道和一個MIMO通道都有關聯。

中頻資料隨後進入下行鏈路FPGA,由該FPGA將其轉換為基頻並進行過濾。即便晶片速率保持在245.76MHz,多向截取濾波器仍能以30.72MHz的符號率進行奈奎斯特FIR濾波(Nyquist Filtering)、光譜鏡像抑制和資料率降低等操作。

FPGA資料輸入流程看上去像一系列的資料,而非OFDM符號。同步函數會對資料流程進行適當的切分,從而描繪出OFDM符號。要實現這一點,同步線路必須使用多個相關器,在銳減的資料中檢測出Zadoff-Chu同步主訊號,以取得OFDM符號。最後,刪除循環字首後,以FFT轉換獲得的最終資料則使用EMIF介面傳遞到另一個DSP。

下行鏈路包含兩個以串列RapidIO介面連接在一起的DSP。這兩個DSP的作用是進行頻率校正、通道估計、均衡和MIMO解碼。之後,再由這兩個DSP在MAC層相互連之前,進行資料通道和控制通道截取、Viterbi和Turbo解碼、去交織和解擾。在上行鏈路側,由第三個FPGA負責上行鏈路和下行鏈路FPGA間的回送測試,確保SDR範本符合通用公共射頻介面(CPRI)/開放基地台架構創始聯盟(OBSAI)標準。

Prisma的設計小組廣泛使用賽靈思Core Generator IP生產濾波器、直接數位頻率合成器(DDS)、快速傅立葉轉換(FFT)、區塊存取記憶體(Block RAM)、先進先出(FIFO)和乘法累加器(MACC)功能,把DSP48E和延遲校準測量(DCM)用於設計中的時脈誤差校正。這種大規模的模擬方法可在縮短開發時間的同時,加快方案設計的速度(圖3)。

|

| 圖3 前端「上行鏈路FPGA」實現反向FFT、循環字首插入(Cyclic Prefix Insertion)、濾波、IF上變頻轉換以及其他時分雙工和PRACH處理所需的操作。該系統將同一訊號發送至兩個DAC以備冗餘。 |

在上行鏈路中採用射頻卡架構

由於該產品推出時間非常緊迫,因此賽靈思對FPGA和DSP間的功能劃分進行分析。值得注意的是,FPGA應能夠支援更多的LTE功能,不過賽靈思的設計目標之一是尋求系統中FPGA與DSP的平衡。

FPGA時脈頻率是設計中較為困難的一環。在大型設計中採用245.76MHz的時脈速率是一項艱巨的任務,設計小組必須考慮功耗、布局布線和在設計上可能會面臨的約束。儘管如此,由於ISE如設計套件可提供各個設計在反覆運算上所需的穩定高品質,過度取樣因子(FPGA時脈頻率與OFDM符號頻率之比)為8,能讓像濾波器和FFT般的設計要項在轉變最少的條件下能滿足所需的LTE功能,而ISE軟體也協助實現一個合理的同步化電路區塊。

Prisma設計的關鍵在於在上行鏈路中採用射頻卡架構,而非使用I/Q不平衡的直接轉換法,接收來自中頻的FPGA資料。使用賽靈思數位頻率合成器(Direct Digital Synthesizer),18位元的正弦/餘弦波(Sine/Cosine Wave)可用於複雜調製工作的理想載波,並可確認無線電訊號傳輸上所測得的誤差向量幅度(圖4)。

|

| 圖4 前端「下行鏈路FPGA」進行IF下變頻轉換、多相截取濾波、同步、循環字首刪除和直接FFT等操作。該系統使用兩個鏈路來支援TDD和FDD模式的MIMO操作。 |

(本文作者任職於Prisma Engineering)