安謀國際(ARM)於2012年初發表全新處理器核心Cortex-M0+。本文將從技術層面介紹此一新方案,同時說明Cortex-M0+如何在嵌入式應用發揮設計開發優勢。

Cortex-M0+處理器是以2009年發表的Cortex-M0處理器為設計基礎,延續Cortex-M0所提供卓越的程式碼密度以及在8位元和16位元處理器的矽面積上最佳的能耗。Cortex-M0處理器自發表以來,已成為ARM授權速度最快的處理器,至2011年底為止,已有超過五十家廠商取得授權。此外,ARM的設計團隊也持續與合作夥伴密切合作,從各種可能的面向強化產品,因而促成Cortex-M0+的誕生。

根據當時ARM合作夥伴的意見反饋,在ARM現有的處理器解決方案中,面對處理資源耗用龐大的應用程式時,有部分需求無法被滿足;其中最重要的就是達到更低的功耗並同時兼顧更高的能源效率。為滿足這些需求,設計團隊從頭重新設計Cortex-M0+,並保有完整的指令集與除錯相容性。這是ARM首次設計具有二階管線(Pipeline)的處理器,並在提升處理器效能的同時,維持相同的高頻率,最後的成果相當振奮人心。在Dhrystone迴圈電力分析中,Cortex-M0+消耗的動態功率,僅有現有Cortex-M0的三分之二(表1)。

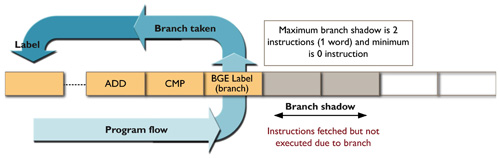

處理器的低功耗表現固然重要,但系統層級的功耗也不可輕忽。Cortex-M0+藉由採用二階管線設計,處理器的陰影分支(Branch Shadow)可被降低(圖1),進而減少對快閃記憶體的存取次數。快閃記憶體的功耗是微控制器(MCU)功耗的主要來源,因此減少存取次數也直接影響整體功耗。

|

| 圖1 Cortex-M0+陰影分支 |

Cortex-M0+輸出/入速度升級

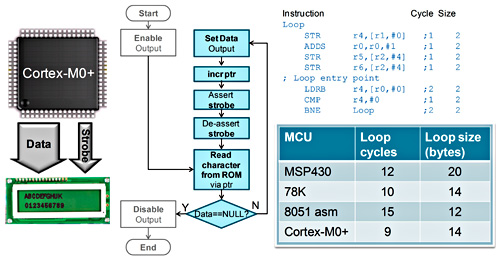

Cortex-M0+處理器支援全新輸出/輸入介面,可提供單循環存取功能,提升輸出入埠運作速度。處理器的輸出入介面為一般32位元介面,微控制器廠商可依需求再加上自己的輸出入埠周邊。搭配此輸出入介面的Cortex-M0+,周邊存取速度將勝過任何市面上常見的微控制器(圖2)。

|

| 圖2 Cortex-M0+核心的輸出/入介面設計全面改良,促使微控制器輸出/入速度大幅提升。 |

輸出入介面既然是系統記憶體圖的一部分,就能以一般的C語言指標存取介面上的輸出入暫存器,毋需特別資料型態等C語言延伸功能。

此外,由於能夠同時存取AMBA AHB-Lite與單週期輸出入介面,Cortex-M0+處理器能夠在存取輸出入時同時讀取指令,也因此單週期輸出入的存取不再受限於時間的限制。

這項改善也有利於功耗感測的應用程式,可以選擇以低速運轉並保留相同輸出入切換頻率,或者更快地完成輸出入控制,然後隨即進入休眠模式。

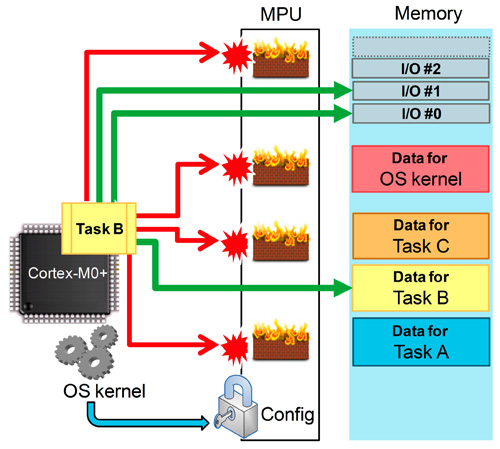

Cortex-M0+也具有多項Cortex-M3與Cortex-M4的實用功能,這是在先前的Cortex-M0所看不到的。像是特權/非特權優先執行層級,以及與Cortex-M3和Cortex-M4類似的記憶體保護單元(Memory Protection Unit, MPU)(圖3)。MPU是具有八個可程式區域的可程式組件,可以在運行的時間透過作業系統針對各種應用程式任務,動態地建立允許存取規則。這樣的機制,在設計上能夠避免應用程式使用到其他應用程式與作業系統核心所使用的記憶體空間。

|

| 圖3 記憶體保護單元 |

此外,Cortex-M0+與Cortex-M3和Cortex-M4相同,同樣支援向量表重定址功能,能讓處理器在運作時輕易地重新指派異常向量。這些功能都可由晶片設計廠商來調整。Cortex-M0+在最低配置時,矽面積與Cortex-M0相同。

對部分的晶片設計廠商來說,更好的消息就是它們能在幾乎不影響系統設計的效能之下,使用搭配16位元快閃記憶體的Cortex-M0+處理器。Cortex-M0+處理器經過設定後,能以16位元而非32位元的設定來抓取指令。由於ARMv6-M架構下多數指令為16位元,因此系統仍然能維持良好效能。這使得Cortex-M0+能維持低矽面積,讓合作夥伴能夠設計出大小合適的解決方案,滿足消費者與安全市場的需求,例如用於工廠自動化、汽車與醫療用的小型感測器/致動器。

支援MTB 提供指令追蹤

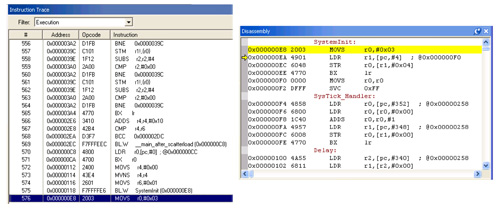

除錯支援中也有幾項新功能。除了Cortex-M0處理器既有的除錯功能外,Cortex-M0+也支援微追蹤緩衝區(Micro Trace Buffer, MTB),提供簡易指令追蹤功能(圖4)。程式設計師可將部分的系統靜態隨機存取記憶體(SRAM)指定為追蹤緩衝區,MTB也將指令流程資訊儲存在專用SRAM中,作為循環緩衝器。當處理器因為中斷點等原因暫停時,除錯軟體能夠透過普遍採用、只需要2管腳的串列除錯(Serial Wire Debug, SWD),擷取追蹤資訊然後重建最新執行紀錄。MTB也能支援單擊觸發功能。

|

| 圖4 MTB支援指令追蹤,在Keil MDK-ARM已全面支援。 |

Cortex-M0+的串列除錯介面也能夠選配稱為多點串列(Multi-drop Serial-Wire)的功能,讓多個支援多點串列的裝置能共用一個除錯連結,這在建造多核心系統單晶片系統時特別有幫助。

對軟體開發商而言,最大的受益就是能夠繼續沿用已經採用Cortex-M0產品上的現有軟體,也能夠繼續使用相同的編譯器套裝軟體、整合式開發環境(IDE)及除錯配接器。Cortex-M0+的指令集與Cortex-M0相似,同時也支援Cortex-M0的所有功能。Cortex-M0+處理器並支援Cortex-M0處理器的休眠模式,且提供優異的中斷處理功能。

Cortex-M0+創造新商機

ARM Cortex-M0+處理器帶來許多創新功能,是一個兼具低功耗、高能源效率、高效能、簡單除錯與記憶體保護功能的微控制器處理器。諸多全新功能,結合業界公認易於使用的特性與Cortex-M處理器系列相容的能力,Cortex-M0+將可提供微控制器開發商更多嶄新的應用商機。

(本文作者為安謀國際嵌入式技術專家)