由於有時無線射頻遠端網路架構(Remote Radio Head)必須支援射頻卡,因此射頻(RF)卡被設計為具有單一輸入時脈,可在鏈結至基地台中被重新取得。這些單一時脈的品質可能不佳,且須要大幅清除抖動,這樣才能在射頻卡上產生其他適當的時脈。因此,射頻卡的時脈樹核心必須是一個具有可程式輸出頻率的抖動衰減器。本文將會探討其效能屬性、為何需要它們,以及時脈樹的需求。

射頻卡架構考量

現今基地台中大部分的射頻卡設計,都須執行許多的操控,以針對數位電路中的協定,例如長程演進計畫(LTE)或多載波全球行動通訊系統(Multi-carrier GSM)去建立或是分拆訊號,而處理錯誤修正、通道匹配,以及利用數位方式分裂I&Q串流則較為容易。無論為傳送或接收方向,此混合訊號的複合資料流也都需要經過非常小心的過濾/訊號處理。在數位電路中執行這件事,可以避免一些麻煩,例如元件數值的精確匹配。

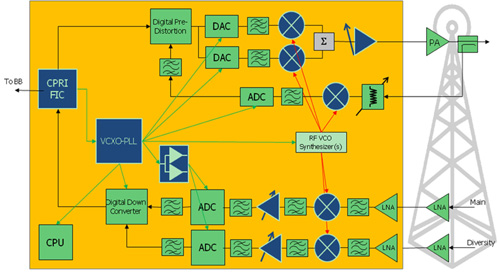

雖然數位控制極為廣泛,不過就某一點而言,訊號都必須被調變為介於824M~2.62GHz間的載波,並且以類比訊號傳送。大部分滿足多通道協定,例如LTE、全球微波存取互通介面(WiMAX)和多載波GSM的基地台架構,都會採用一種單級類比轉換方式,如圖1所示。

|

| 圖1 典型的LTE射頻卡架構 |

在傳送端,個別的次載波會在被調變前,先結合為一個單一數位流。然後,此基頻訊號會被數位類比轉換器(DAC)轉化為相位抵銷的類比I&Q流,之後又透過正交類比混波器,被上鏈轉換(Up-converted)為傳送頻率。可變和固定增益放大器以及雙工濾波器會被用於路徑上,如此可推升訊號,使其達到在傳送頻寬中所需的力道。同時,雜訊及失真僅些微增加,且還能同步將傳送頻寬外的耗電降至最低,以避免和其他射頻通道產生干擾。

至於接收端的部分,射頻訊號通常會被放大、過濾,然後透過混波器轉變為頻率下降許多的中頻(IF),介於75M~250MHz之間,接著還會進一步被適當放大及過濾,最後再經由管線式類比數位轉換器(ADC)取樣,此取樣符合奈奎氏準則(Nyquist Criterion)。然後,次載波的下鏈轉換(Down Conversion)及調變會在數位電路中處理。此接收器的目標是要在ADC之前完成訊號調整,且雜訊及互調失真的增加得降至最低,同時還要避免超出ADC的完整範圍(Full Scale)。

射頻卡架構比較偏愛時脈樹能盡可能的整合。不只是因為上述的理由,還因為每一個時脈樹元件都會對抖動做出貢獻,如此會導致時脈訊號不符規格。就此整合而言,不僅須針對調變產生射頻和中頻時脈,還必須為ADC及DAC產生取樣時脈,也必須生成其他數位元件,例如中央處理器(CPU)、特定應用積體電路(ASIC)及現場可編程閘陣列(FPGA)所需的時脈。

相較於射頻訊號路徑上的時脈,數位元件的時脈規格通常極為寬鬆;週期抖動通常是最主要的考量。在同一晶片上產生這些時脈,做為更敏感的時脈,其中會有兩個問題。首先,數位時脈很少會將進來的各種時脈訊號整合至射頻卡,所以必須以分數回饋(Fractional Feedback)或分數輸出分頻器(Fractional Output Divider)技巧產生所需時脈。這兩種技巧都會造成時脈晶片內及時脈輸出上的突波。第二,降至接近射頻、數位中頻(IF)或取樣頻率的數位晶片時脈(或是生成這些時脈所產生的突波),都無法被輕易地濾出,因此必須要加以避免。即使是這些相關區域外的頻率元件,也可能因為產生寬頻雜訊或是因為沒有被過濾,而混入嚴格的頻率範圍中,造成訊噪比(SNR)特性降低。

混波器/ADC/DAC頻率效果

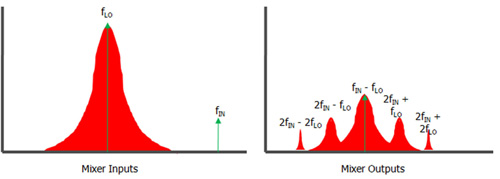

ADC會採用混波器,將較高頻的訊號轉換為較低頻的訊號,反之亦然。在大部分的基地台射頻卡設計中,它們現階段是將射頻轉變為中頻,或是從基頻轉變為射頻。就此方面而言,時脈樹設計的主要考量是頻率混淆(Frequency Aliasing)。當多個頻率通過非線性裝置,那些頻率會彼此產生互動。這些互動源於互相調變。混波器的功能便是取兩個輸入頻率,並產生一個新的輸出頻率,這個輸出頻率可能是這兩個頻率的和(上鏈轉換)或是差(下鏈轉換)。

現今的射頻卡是被設計為重新取得本質為多載波的訊號。理想的訊號包含一個均勻分布在整個相關頻帶的調位線路(Tone Lines)完整系列,而非預期訊號的單一調位線路,這些線路代表被重新取得的通道。很不幸的,當此種多載波訊號行進通過一個非線性元素,例如混波器,那些通道會彼此干擾。通道間的固定間隔會造成奇數階生成物(Odd-order Product),就幾乎落在被恢復的通道的上方。在混波器之前的濾波器會被用來衰減雜訊,這些雜訊會促成偶數階生成物(Even-order Product),而混波器之後的濾波器將除去落在相關頻帶之外的交互調變生成物,但是幾乎不太能除去頻帶內的奇數階生成物,因為它們太接近被預期的訊號。

混波器之後的帶通濾波器(Band Pass Filter)可以徹底清除不需要的乾淨調位線路,在此取樣時脈上的任何抖動都會將那些乾淨的調位線路轉換為如圖2所示的裙狀物。來自每一個不受歡迎的生成物的裙狀物其尾端部分,都會在濾波器的通帶(Pass Band)內造成一些影響,這被稱為寬頻雜訊。任何針對混波器或是ADC、DAC生成的時脈都必須具有極低的雜訊層,如此才能將寬頻雜訊的影響降至最低。

|

| 圖2 相互混頻的效果 |

不想要的訊號通常被稱為「干擾」或「障礙物」,若在混波器的輸入內,便會影響時脈訊號的規格。它們會包含其他由天線所接收的訊號,或是系統內部的訊號,這些訊號被耦合至接收訊號路徑。雖然廣泛分布在預期訊號頻率中的干擾,可以經由前置濾波器而明顯衰減,但是接近預期訊號頻率的干擾仍會通過。再者,在像是LTE這樣的協定中,想要的訊號必須具有極低的平均功率,而即使是經由濾波器衰減的干擾仍會包含足以和預期訊號匹敵的能量。

這樣的效果,就是為何進入混波器內的相位雜訊裙帶必須盡可能的「窄」。必須限制干擾物上相互混頻的相位雜訊的擴散,將其範圍縮減至最小。射頻卡設計的重大挑戰之一便是挑選卡上的頻率,而且還必須顧及將干擾物和來自想要訊號的頻率的相互調變生成物盡可能地分開。

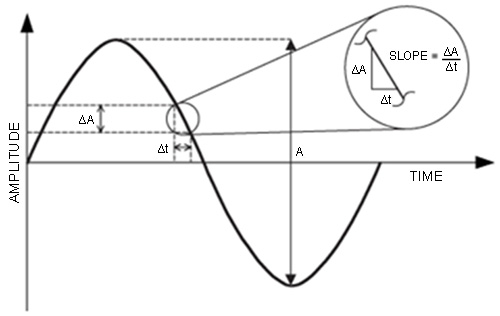

孔徑抖動影響ADC取樣時脈規格

由於ADC為經過取樣的數據系統,且其傳輸並非完美的線性,所以它們也會受到所有相同的作用,也就是存在於被預期的輸入訊號、干擾物訊號和取樣時脈間的交互調變生成物的影響。

然而,還有另一個作用會影響ADC取樣時脈的規格,就是圖3所示的孔徑抖動(Aperture Jitter)。孔徑抖動的基本概念,是指任何發生於取樣時的不確定性,都會被三角轉化為樣本振幅中的不確定性。振幅中的不確定性會導致ADC訊噪比的退化,一旦知道此輸入訊號的頻率,便可針對ADC的預期SNR決定方均根(RMS)抖動量的目標值。一旦達到此目標,則ADC內部時脈樹的固定抖動將會經由分析,以決定取樣時脈的RMS抖動目標規格。

|

| 圖3 ADC孔徑抖動原理 |

潛在機制影響DAC取樣頻率

DAC被用於傳輸路徑上,可將數位基頻訊號轉變為類比訊號,隨後並轉化為RF頻率和放大到所需的發射功率。射頻卡設計須留意修正射頻卡的頻率規畫,確保DAC採樣頻率不會與接收卡端的臨界頻段重疊,這相當重要,因為DAC受到來自兩個潛在機制的頻率生成圖像的影響。

第一種機制和發生於ADC及混波器中的情況是一樣的,取樣時脈(fLO)和輸入訊號(fIN)的卷積(Convolution)會產生N.fLO±M.fIN的頻率。此卷積得自轉換器中的非線性特性。針對取樣時脈抖動的需求,此作用相似於ADC。

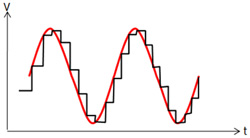

|

| 圖4 DAC輸出和理想輸出比較 |

第二種機制則是大部分DAC操作方式所會造成的作用,這是無可避免的。如圖4所示,在取樣時脈的每一個邊緣,DAC的輸出都會很快地切換至一個新的電壓水準,也就是數位取樣值。此數值會被維持至下一個取樣時脈邊緣。針對每一個取樣時脈,輸出只會匹配預期的波形一次,這將導致引進錯誤的電力。

此外,大部分的DAC將受到時脈饋通(Clock Feed-through)的影響,導致N.fLO進一步發生突波。基於此理由,取樣時脈頻率通常會被設定高於奈奎氏準則所需,如此一來,饋通突波會超出相關頻率,因此可以被輕易的過濾。

DAC輸出波形將會通過類比重建濾波器,以便盡可能除去不被需要的頻率。如果時脈抖動和相位雜訊裙狀物能被良好的控制,此濾波器的設計將容易許多,也會比較便宜。除了對取樣時脈特定偏移的特定相位雜訊水準有所要求外,還會要求整合一定範圍頻率的RMS抖動的規格,這是因為時脈抖動會造成輸出波形的失真,無法呈現理想波形。此舉將導致總諧波失真(THD)或訊噪失真比(SINAD)特性的降低,必須保持一定的規格,才能避免誤差向量幅度(EVM)特性的惡化。在傳送端,更低的抖動、直接促成更好的EVM或被用以鬆動設計限制,以實現波峰因素/峰均值功率比(Crest Factor/Peak-average Power Ratio)降低線路。

射頻卡相位校準要求

除了基本的語音和數據傳輸服務外,許多行動使用者會要求額外的服務。例子之一便是透過一組三角訊號發射台能精準定位使用者的位置。當所有的天線都是以一致的相位傳送或接收訊號時,便能達到最佳的射頻三角形精準定位。一些這樣的服務須要利用獨立的基地台,以彼此之間低於50奈秒(ns)的相位差異(Phase Discrepancy)操作。射頻卡會被給予相對於同一系統中的其他射頻卡相位差異的限制。這是為何每一片射頻卡都自一個單一時脈輸出訊號,在內部生成所有的時脈的另一個理由。它確保至少能為卡上的所有時脈的相位校準提供一個共同的起點。

射頻卡須要自一個單一時脈產生各種時脈,而這個時脈通常會是吵雜的輸入時脈。這些輸出時脈中,有些不會和輸入時脈具有完整關係。針對所有的時脈,必須注意它們對雜訊的貢獻,以避免雜訊被耦合至重要的電路中。ADC和DAC都專門用於混波功能,在RMS抖動及「雜訊裙狀物」方面也都有非常嚴格的要求,以避免在RF訊號路徑上產生干擾訊號。這些頻率都將會被仔細規畫,以實現射頻卡的各個細節,因此每一個設計都是獨特的。再者,針對許多相同的時脈,必須要能夠進行各種相位延遲調整。結果就是必須要有極高效能的時脈樹,其規格必須能針對每一張射頻卡做出量身打造,而且最好是由單一元件來實現。而IDT Netcom時序元件則具有獨特的定位,可針對個別的射頻卡設計要求提供極高效能的元件。

(本文作者為IDT系統架構協理)