無論是作為獨立的處理單元,或者與輔助處理器共用,系統單晶片(SoC)現場可編程閘陣列(FPGA)元件皆可改善嵌入式處理的安全性。雖然可以利用專用安全元件來建構嵌入式處理器模組,然而,在SoC FPGA元件中實施監測和靜態金鑰儲存(Static Key Storage)、系統關鍵功能整合以及安全特性可以提供更大的安全性、靈活性和性能。

在嵌入式設計中,以Linux替代裸機系統(Bare Metal System)已成為日益流行的作法,而隨著32位元運算成為常見商品,及像Yocto等專案使得用於嵌入式應用且建基於Linux的系統變得更加容易創建、開發以及維護,也使得Linux系統受歡迎的程度越來越高。Linux使得原始設備製造商(OEM)變得更像初創企業,其靈活的硬體開發團隊使用作業系統來提取底層的硬體細節以加快上市的速度。

保護啟動過程 杜絕Rootkit威脅

儘管Linux系統具有這些好處,然而如果沒有合適的方法來啟動嵌入式處理器,便會容易受到Rootkit攻擊。對新興的物聯網(IoT)來說,Rootkit特別具有不確定性,因為物聯網將會創造出數十億個具有潛在不安全的新端點。

一般而言,Rootkit試圖存取特權(根)模式(Privileged Mode),同時躲避系統惡意軟體檢測(Malware-detection)工具。惡意軟體也可能試圖透過修改系統的啟動過程,將自己安裝到系統內以達到持久的狀態(Persistent State)。如果成功,惡意軟體感染便是永久的,或者會透過上電循環而存留,這樣惡意軟體就可為所欲為,包括收集個人資訊。一旦系統受到感染,就可能須要將整個作業系統重新安裝。

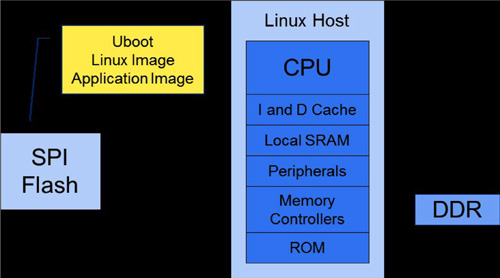

問題從嵌入式處理器開始,其啟動過程通常如圖1所示。在上電時,片上(On-chip)唯讀存儲記憶體(ROM)將從外部非揮發性記憶體取得開機載入程式。開機載入程式是專用的,並且在啟動期間對處理器進行配置,以滿足特定應用的需求。時鐘、高速緩衝記憶體、記憶體控制器以及週邊設備(Peripheral)均會被配置。當處理器被初始化,就從外部非揮發性記憶體取得應用程式(有時被解壓縮),並且複製到應用程式運行之處的快速外部揮發性記憶體。

|

| 圖1 嵌入式啟動過程 |

在啟動過程中,惡意軟體有機會去試圖修改嵌入式系統的開機載入程式,圖2所示為嵌入式Linux系統的典型方塊圖,UBOOT、Linux內核和應用程式層均儲存在易於存取的非揮發性記憶體中。

|

| 圖2 嵌入式Linux系統運作示意圖 |

保護啟動過程的唯一方法,是使用一個可以信任它能始終以預期方式運行的元件來提供保護。作為系統元件,這種信任根(Root-of-trust)支援系統、軟體和資料完整性和保密性的驗證,以及將信任擴展到內部和外部的實體,這是創建所有其他安全層的基礎,而且金鑰必須保密,其遵循的過程也要永遠不變,這是十分重要的。

善用SoC FPGA 進行安全啟動

在嵌入式系統中,信任根與其他系統元件共同工作,以確保只有經過授權的代碼可以安全地啟動主處理器,從而將信任域擴展到處理器及其應用。透過使用加密技術,可以擴展信任域以涵蓋所有重要的系統元件,甚至在本質上不安全的網路中將數個信任系統連結在一起。

雖然許多較新的處理器具有特定的功能以支援安全啟動,但對處理器晶片安全啟動的固有支援仍然相當不普及,且通常需要多晶片的解決方案。建基於快閃記憶體的FPGA是更好的解決方案,它是在多晶片嵌入式系統中提供信任根的最佳元件之一,可以顯著地提升主嵌入式處理器運行中的任意代碼之保障等級,且這種保障等級的提升是可信的。

在本質上,建基於快閃記憶體的解決方案更加安全(它們的程式一經輸入,關鍵的資訊就永遠不會離開晶片),而且今天建基於快閃記憶體的SoC FPGA解決方案還新增了數項先進安全特性,包括片上振盪器、用於加密服務的加速器、安全金鑰儲存、真正的亂數產生器、儲存在安全的嵌入式快閃記憶體(eNVM)中的片上啟動代碼,以及高速串列週邊介面(SPI)快閃記憶體模擬,以實現安全的外部處理器之高速啟動。這些元件還具有超越先前解決方案的更強大的設計安全性,並且包含防差分功率分析(Differential Power Analysis, DPA)的防篡改措施。再加上嵌入式Linux中央處理器(CPU),它們能夠有效地用於防止惡意軟體試圖修改嵌入式系統的開機載入程式。

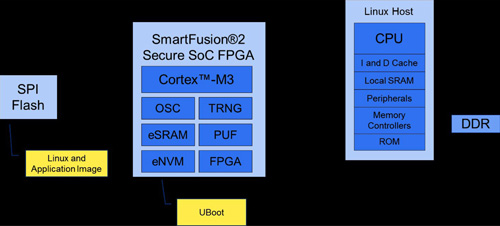

圖3所示為可以用於安全啟動、以快閃記憶體為基礎的SoC範例,美高森美(Microsemi)SmartFusion2 SoC元件內的eNVM可用來儲存UBOOT,而其FPGA架構則會模擬高速SPI快閃記憶體。CPU並不知道這SoC是位於其和SPI快閃記憶體之間。在上電時,SoC將UBOOT的SPI讀取請求從內部eNVM導向CPU,而後CPU進行正常的UBOOT啟動過程,並且從外部SPI快閃記憶體取得應用鏡像的剩餘部分,在後者的階段中,SoC可作為外部記憶體的導管,並且將應用鏡像傳送給CPU。

|

| 圖3 SmartFusion2元件用於儲存UBOOT |

SoC及其內部eNVM僅可使用經過認證的加密位元流(Bitstream)進行程式設計,這種位元流僅可由SoC的FPGA開發環境來建立。位元流檔案格式是專有的,不會提供給任何人,並且具備從Cryptography Research Incorporated(現為Rambus)授權許可的專利保護措施,所以可以抵禦DPA側道攻擊。

為了確保安全的多級啟動,在提供和執行代碼之前,進行驗證是必不可少的。這可確保不會出現攪亂或損壞各階段啟動的入侵,並且可利用對稱或非對稱的金鑰加密技術來進行。更好的是,可以使用對前一個階段的連續回饋來確認在啟動載入期間沒有受到篡改。如果所有的防篡改(Anti-tamper, AT)監測器確認環境是安全的,各個階段就可以繼續執行。

現今的SoC FPGA可以獨立提供執行時間監測和校正行動,或者在有需要時做出懲罰。為了這樣做,所有的應用程式碼將儲存在SPI快閃記憶體內,而且可選擇加密。SoC元件將在每個階段對代碼進行真實性檢查,在需要時將代碼解密,並且在通過MPU-to-FPGA SPI介面收到請求時將之饋入主微處理器(MPU)。為了增加安全性,開機載入程式代碼將會儲存在SoC FPGA的eNVM內。

在上電之後,FPGA將會把主MPU保持在重定模式,直到它完成自身的完整性自我測試。在準備好後,它便會釋放復位。MPU將被配置為從介面至FPGA來啟動(例如透過SPI介面)。FPGA將扮演SPI從屬(Slave)的角色,在MPU復位後,將向MPU提供所請求的Phase-0啟動代碼。假設MPU本身不支援安全啟動,便要面臨一大挑戰,就是確保載入MPU內的代碼未被篡改。

如果各個項目均沒有錯誤,啟動過程將會繼續,將現在獲得信任的代碼載入MPU的靜態隨機存取記憶體(SRAM)內,這將包括開始下一個階段的所需代碼,以及一個現在獲得信任的RSA或橢圓曲線加密(ECC)公共金鑰。一旦MPU SRAM中的代碼獲得信任,就可以部署附加的安全措施,例如使用公共金鑰方法來建立分享的金鑰。此外,也可以將系統所有的硬體元件結合(Bind)在一起加密,使得系統必須具有初始系統的所有元件才能夠運行。

此外,SoC可以提供模組環境情況的即時監控,例如溫度、電壓、時鐘頻率和其他因素。FPGA架構可以安全地配置,以便為外部篡改感測器和侵入檢測器提供輸入/輸出(I/O)。這些情況可以透過SoC來感測,防止來自已知漏洞的攻擊,這些攻擊可施加異常條件來提取關鍵的資訊。透過合適的設計,便可以達到更高的安全等級。

(本文作者為美高森美產品行銷總監)