隨著世界更加互聯與數位化,對更多數據與更高速的需求也日益明顯。全球網路流量的增加,以及雲端和資料中心的去中心化,帶動有線和無線網路支援5G基礎建設的趨勢。5G技術可望催生千倍流量、十倍快的速度和十倍流量增長,這些高度複雜的系統挑戰了矽晶片和製造技術的極限。現已有晶片商,如eSilicon的設計和驗證方法(Design-and-verification Methodology)採用晶片封裝系統(Chip-package-system, CPS)模型和模擬軟體,以時效性和精確度滿足持續進化的市場。

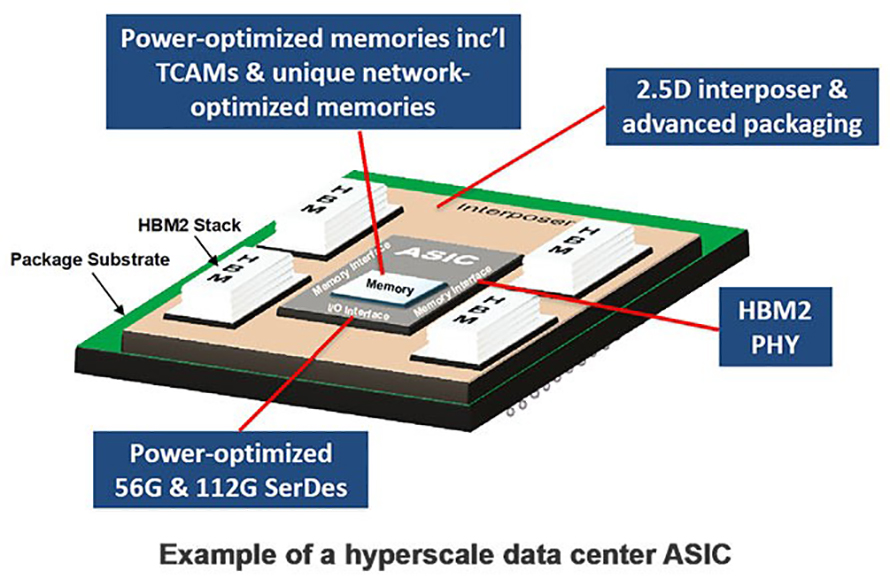

晶片商在進行高科技設計時,需要的不僅是符合規格運作的晶片,同時也需要有全面的系統效能。為了因應這些需求,晶片商針對5G基礎建設、網路、高效能運算和人工智慧市場的一線(Tier-one)系統原始設備製造商(OEM),採用先進特殊應用積體電路(ASIC)和智慧財產(IP)。eSilicon提供的FinFET ASIC整合先進IP,後者以eSilicon的14奈米和7奈米技術以及先進的2.5D封裝開發。因此能提供耗電更少、頻寬更高和彈性更大的產品,以滿足客戶的運算效能和系統可靠度需求(圖1)。

圖1 eSilicon高度可配置的FinFET級7奈米IP平台包括針對應用最佳化的處理器核心,以及數個與矽中介層整合的高頻寬記憶體(HBM)堆疊,這都是複雜2.5D封裝的一部分。

圖1 eSilicon高度可配置的FinFET級7奈米IP平台包括針對應用最佳化的處理器核心,以及數個與矽中介層整合的高頻寬記憶體(HBM)堆疊,這都是複雜2.5D封裝的一部分。

在設計上線(Bring-up)時或產品已在市場銷售一段時間後,與較小半導體技術節點、更高密度以及更小設計空間(Margin)有關的複雜度的確會增加系統故障風險。

由於設計成本高達數千萬美元,重製(Re-spins)會導致設計延誤和錯失市場商機,故晶片廠商會仰賴EDA的晶片封裝系統模型和模擬軟體(包括ANSYS SIwave、RedHawk、HFSS、和CMA),在Tapeout前進行系統測試和驗證。EDA軟體可針對從晶片、封裝、基板到系統的每個元件,製作非常詳細的模型,並提供可將各元件無縫整合為單一模擬的環境。盡早從前端至後端確認整體系統十分重要。設計方式若能涵蓋所有元件(晶片、記憶體、基板和封裝)、確保ASIC本身能正常運作、並在整套系統內正常運作,可降低風險並縮短上市時程。

工程師需要與設備商密切合作,管理其設計和界面的複雜度,包含密切關注跨越晶片、封裝基板和系統的訊號完整性(Signal Integrity, SI)和電源完整性(Power Integrity, PI)的影響。晶片商與EDA商合作,開發CPS SI/PI模型和分析流程,可製作從晶片、封裝、到電路板上所有元件的詳細模型,並一起模擬所有元件,以便瞭解元件如何彼此影響。

確認訊號完整性

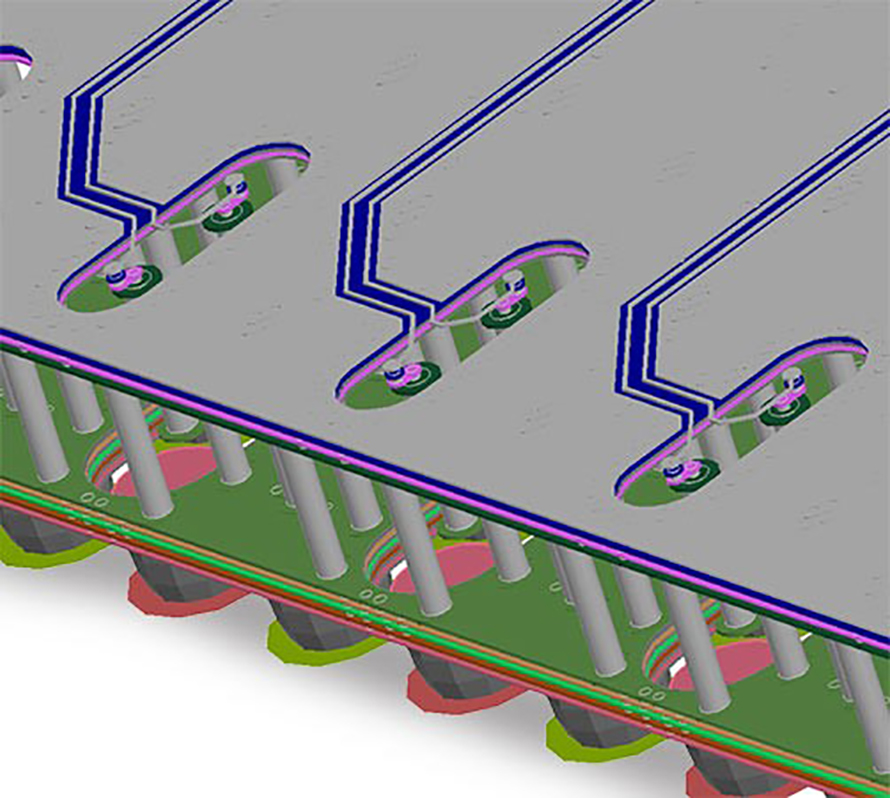

一旦完成基板和矽中介層的初始布局,工程師就會運用高頻結構模擬(High Frequency Structure Simulator, HFSS)軟體和SIwave設計平台萃取複雜的3D架構,針對高速網路的插入耗損(Insertion Loss)、反射耗損(Return Loss)和串音(Crosstalk)效能分析,製作S參數模型。再比較被動元件(Passive Element)的頻率響應和封裝規格。任何不合或不足都會導致設計變更,包括額外的萃取和分析疊代(Iteration),直到符合需求為止。就2.5D封裝設計而言,工程師會連結基板和中介層S參數模型,製作最終封裝模型。該模型再交給客戶進行IBIS-AMI通道分析,確認時域內的傳送和接收效能(圖2)。

圖2 封裝基板BGA區的絕緣錫片經放大並區隔橋接,降低電阻並提高阻抗。

圖2 封裝基板BGA區的絕緣錫片經放大並區隔橋接,降低電阻並提高阻抗。

封裝基板上被動導線的材料屬性和幾何尺寸可能影響最終S參數效能。就2D設計而言,數種場效解決方案(Field Solvers)都能計算阻抗和SI效能,但工程師設計的2.5D封裝就需要真正高頻SerDes設計用的3D場效解決方案ANSYS HFSS。在幾何密集的封裝或中介層內,鄰近結構對訊號效能(特別是高頻部分)可能有顯著影響。

確認直流電源完整性

在直流電源完整性方面,工程師會針對從電路板上從電壓調節模組(Voltage Regulator Module, VRM)經布線通往封裝基板和矽中介層的直流降壓,製作模型。如果工程師發現任何瓶頸或違規,就會進行額外的疊代,改善電源配送網路。工程師可運用高精確度、快速產出量和無縫整合的EDA工具,改善其設計並快速進行假設分析以改良設計。

對從電路板到晶片電源路徑的正確觀點,加上各層級的詳細寄生參數萃取,都是進行可靠PI分析不可或缺的要素。當工程師假設系統電路板上有理想化電壓調整模組的時候,因為局部電流可能超過電壓源的平均電流,模擬結果可能和真實效能也有顯著差異。因此必須精確定義VRM的位置,並萃取驅動封裝的真實布線。

確認交流電源完整性

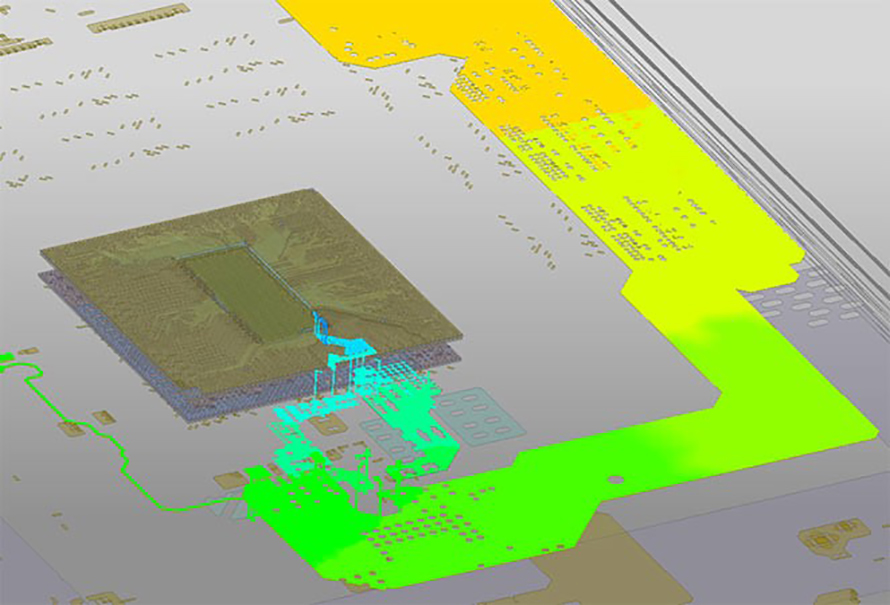

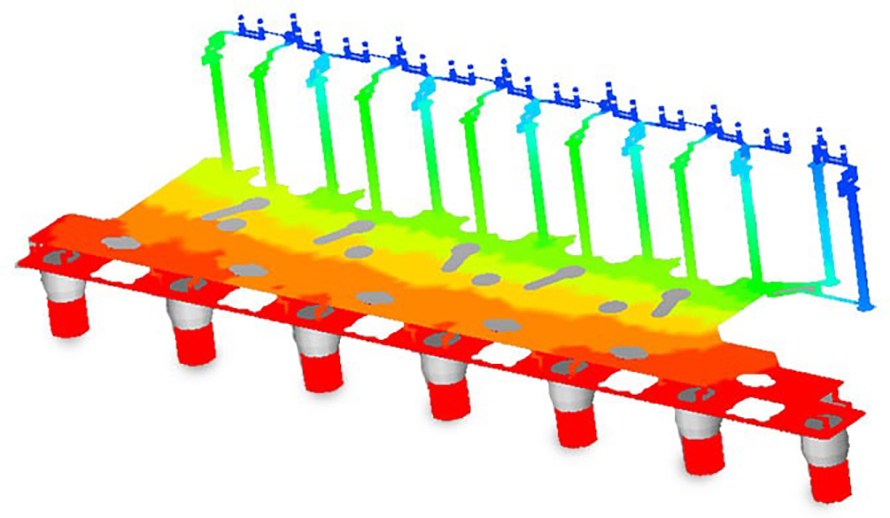

管理系統晶片產生雜訊的衝擊,對設計成功至關重要。要獲得電源完整性的全面觀點,就必須瞭解電源如何透過矽中介層、封裝基板和電路板傳送。工程師採用CPS法,透過萃取和為各元件製作模型,從晶片、中介層、封裝基板、一直到PCB,然後模擬各頻域和時域下的整個系統。要非常精確地確認整套系統,確認從VRM到晶片等元件的不同頻率範圍,可說是一大挑戰(圖3)。

圖3 電壓曲線圖的3D模型顯示從VRM到封裝的模擬電壓梯度,幫助工程師找到降壓處,如PCB通孔、BGA下的瑞士起司面以及封裝層。

圖3 電壓曲線圖的3D模型顯示從VRM到封裝的模擬電壓梯度,幫助工程師找到降壓處,如PCB通孔、BGA下的瑞士起司面以及封裝層。

CMA可跨越晶片、封裝和電路板的寬廣頻譜,製作完整電源配送網路的特徵檔。它能模擬晶片、封裝和電路板邊界的大電流暫態,長短從數奈秒到數毫秒,這些電流可能導致災難性的全面電源走線電壓崩潰(圖4)。

圖4 模擬從封裝到晶片介面、從BGA錫球通過基板通孔、最後到連接C4介面的布線電壓梯度。因為封裝內的電源配送網路較PCB上的更小更密,封裝設計的IR壓降可能改善機會更大。

圖4 模擬從封裝到晶片介面、從BGA錫球通過基板通孔、最後到連接C4介面的布線電壓梯度。因為封裝內的電源配送網路較PCB上的更小更密,封裝設計的IR壓降可能改善機會更大。

交流電源完整性分析的目標是透過阻抗最佳化,確保可接受的暫態電源雜訊。如果電源雜訊過高或其邊界太低,工程師會回溯到頻域,進一步將解耦合電容最佳化,甚至回溯到布局。工程師在設計階段盡早進行分析,不僅是進行確認,而得以將效能最佳化。

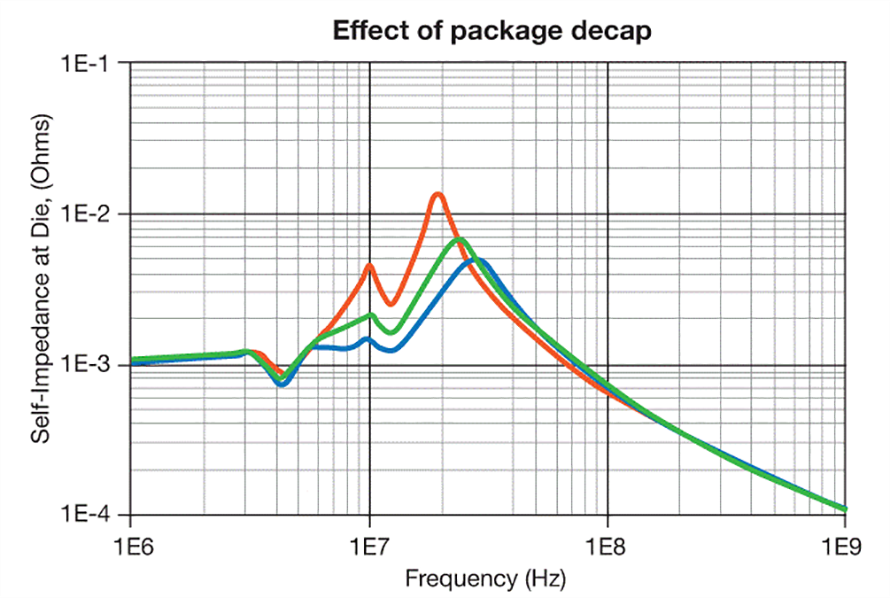

頻域自阻抗和電容最佳化

做為頻域分析的一部分,工程師會觀察晶片自阻抗(Self-impedance)和對各系統元件的影響,必須決定是否需要用封裝層電阻降低封裝的系統級共振(Resonance),因此運用SIwave計算目標阻抗,再添加不同數值和數量的電容,達到去共振頻率的效果(圖5)。

圖5 觀察在封裝層添加1uF電容的效應。數量的增加顯示平行共振點的阻抗降低。一旦達到目標阻抗,再將最佳化聚焦在有效混合電容值和數量上。

圖5 觀察在封裝層添加1uF電容的效應。數量的增加顯示平行共振點的阻抗降低。一旦達到目標阻抗,再將最佳化聚焦在有效混合電容值和數量上。

工程師完成頻域解耦合電容最佳化,就可以進行時域模擬,分析晶片的電源供應雜訊,其運用RedHawk產生電流特徵檔(Current Profile)並萃取晶片電源配送網路的電氣模型。RedHawk主要是一種晶片層級工具,因此模擬可產生含高頻資料的電流特徵檔,但時間非常短。但進行較低頻寬的系統層級分析需要更長的時間。但因為要用電流調變來刺激特定共振頻率,或製作TCAM記憶存取之類功能模式的模型,不是重複波形就能延長電流特徵檔。CMA可讓工程師將電流特徵調變為任何一種包絡(Envelope),並輸出頻域阻抗以及人和時域瞬態雜訊。除此之外,CMA可自動連結晶片、中介層和封裝的複雜介面,大幅節省人工並減少錯誤。

工程師一取得擴展和調變電流刺激後,就會用CMA的時域模擬來分析整個電源配送網路,並比較模擬結果和容許雜訊規格,確認是否有所不合。如果需要額外的邊界,工程師就會再進行頻域模擬,透過改變晶片、封裝或電路板上的電容,進一步將設計最佳化。此外,工程師甚至可能進一步回溯設計流程,將電源配送網路布局最佳化。

(本文作者為eSilicon訊號和電源完整性架構師)