數位設計工具包(DDK)是系統單晶片(SoC)開發的基本構件。如今技術團隊增加越來越多的新標準單元(Cell),使SoC設計人員在選擇最合適款型的標準單元來實現面積、速度和SoC功能方面的目標時更為複雜。

根據摩爾定律,積體電路中的電晶體的數量幾乎以每兩年翻一倍的速度增長。但技術的發展經常超越摩爾定律。此外,SoC開發還希望能夠在十八個月的時間內使晶片效能翻倍。因此,設計團隊正在快速遷移到更低的技術節點,這些節點帶有不同的標準單元和設計技術。然而,某項技術的製造工藝需要時間才能日臻成熟。這就需要考慮技術資料中的不同風格,例如不同的VT(臨界值電壓)、低功耗、高速和高K。

對於SoC設計團隊來說,要熟悉新技術、工藝、版本和不同的資料是一大挑戰。首先,設計團隊需要在可用和不可用的標準單元之間進行選擇,最大限度地降低晶片可靠性和量產風險。為了獲得對於SoC設計最佳的效果,各種通用物理設計流程中,在選擇某些單元時,某些原則必須加以使用或者避免。

了解設計中的多VT和通道

在互補式金屬氧化物半導體(CMOS)工藝中,其中包含多種VT,通常分為高VT(HVT)、標準VT(SVT)、低VT(LVT)三大類。

這些單元經常可以靈活組合,滿足現代SoC的高效能和低功耗目標。基本上,LVT單元都是以高效能為目的,但漏電流較高,而HVT單元漏電流較小,但效能較差。SVT在HVT和LVT的功率與效能之間取得一種平衡。因此,必須根據設計要求謹慎選擇合適的VT。

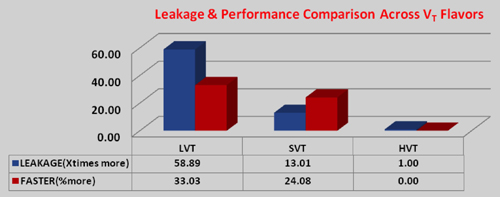

圖1展示了所有VT的延遲和功率變化的典型趨勢。功耗和延遲已根據HVT單元進行歸一化,從圖中可以看出,透過降低VT可提高效能,但同時也會使漏電功耗呈指數增長。這種不對稱的效能與功耗關係對於VT的選擇至關重要,特別是在高效能低功耗設計中。

|

| 圖1 各種VT的功率與效能變化 |

除了VT特性外,基於CMOS的函式庫還為類似的領域和驅動強度(Drive Strength)、提供一些其他的功率與效能關係的變種。只須略微改變特定單元中所用的CMOS電晶體的通道長度即可實現。由於通道長度L與驅動強度成反比(公式1),因此通道長度越長,驅動電流就越低,單元的資料傳輸速度就越慢,從而使功率更低。

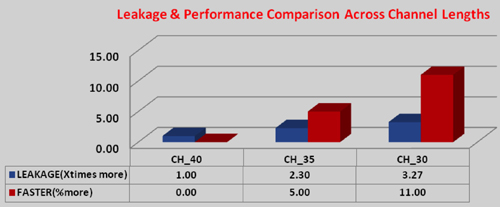

圖2展示了針對一個樣本庫套件中各種通道長度的類似功率與效能比較。許多庫供應商在所提供的低功耗設計套件中包含這些高通道長度單元,目的是進一步縮小VT分割所產生的效能與功率差距。

|

| 圖2 多個通道長度的功率與效能變化 |

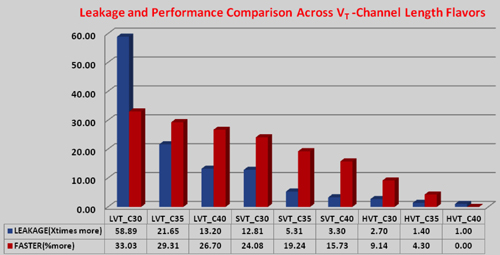

在典型場景下,VT和通道長度劃分被用於提供更大的單元選擇範圍,從而使設計人員和電子設計自動化(EDA)工具能夠更加靈活地進行時序優化和面積減少。圖3顯示了功率與效能平均擴展,這兩個參數(VT和溝道長度)的影響都可見。這種廣泛的單元選擇範圍在物理設計過程中可能帶來更多機會也可能帶來問題,面積這個成本函數可能與時序或功率等其他成本函數恰好相互矛盾。接下來,將分析發生此類矛盾的一些情況,另外還會討論物理設計工程師必須採用某種方法以獲得最高效的實現方法。

|

| 圖3 不同VT與通道長度組合的功率與效能變化 |

留意最佳功耗/面積利用率

當降低VT和通道長度時,單元延遲與輸出轉換的改進幾乎是線性的,因為VT和通道長度(間接地W/L)都會線性影響漏電電流。然而,相對功耗呈指數級增長,原因是漏電流隨著VT和通道長度的變化呈指數級變化。因此,從理論來說,設計人員不得不犧牲許多的功耗才能換來效能的略微改進。這個限制在深次微米(Deep Sub-micron)技術方面更令人擔憂,因為在該技術領域,功耗問題更為突出。

現在就來分析一下,對不同VT和通道長度的使用的控制如何影響整體設計時序和功耗。在執行後期合成或後期布局優化時,設計過程中存在很多時序違規。由於時序的優先順序高於面積和功率,EDA工具通常最終會使用速度更快和功耗更大的單元(LVT、短通道長度)。

有兩種方法可實現最佳時序目標:一是首選使用速度更快、功耗更高的單元(犧牲功率換取效能),二為根據優化工作進行重組(犧牲執行時間換取效能)。

一般普遍認為,在基於重組的優化方面,綜合工具比APR工具更加強大。人們認為,APR工具可智慧地將單元切換到更高的驅動,還能夠根據給定的平面圖進行基於VT的單元切換,以滿足時序目標。一般而言,最好利用綜合工具的強大功能進行重組優化,而不是任其自由地使用功耗高、速度快的單元。然而,這一學派只有在時序關鍵路徑(Critical Path)的百分比很小的情況下才有效。另外,這種方法有時可能導致SoC面積不必要地增大,以滿足時序限制。當實現高效能、時序關鍵型設計時(例如一些SoC內核或圖形處理單元),該工具遇到的大部分路徑都已經是時序關鍵的,僅僅在合成層面進行重組優化無法滿足這些路徑的要求。因此,工具最終擴大了面積,如果停止使用高功耗單元並只依靠時序關鍵路徑的重組功能,工具將開始使用非常高功率的驅動單元。

試想一下,設計人員已完全阻止使用功耗更大的LVT模組來實現優化。由於資料路徑的時序關鍵性依然保持不變,因此為了滿足這些路徑,該工具將不得不插入更大的HVT/SVT單元才能滿足類似的時序,它本來可以透過使用更小的LVT就能夠滿足。

透過分析在所有不同VT下典型緩衝模組的功率、延遲和功率延遲乘積(Power Delay Product, PDP)的擴展,可更好地理解這一行為(圖4)。考慮圖4所示的延遲擴展中間標記的三個模組。模組HVT-C35-9(一個HVT模組,通道長度為三十五個單位,驅動強度提高9倍)、SVT-C35-2.5和LVT-C35-1都擁有相似的延遲和漏電功率,因此可進行互換,以獲得相似的時序。然而,若根據驅動強度的變化來考慮,那麼對於每個LVT,該工具都需要插入驅動強度為原來2.5倍的SVT或驅動強度為原來9倍的HVT。

|

| 圖4 不同VT、通道長度和驅動強度的緩衝單元的PDP擴展 |

現在,隨著所使用的驅動強度不斷增加,相關的單元面積和負載電容也相應地增加。由於動態功率與負載成正比,因此儘管已經努力略微控制時序和功耗(如PDP中所示,這三個單元的功耗幾乎完全相同),但最後依然使用更多的單元面積和更高的動態功率,還增加了總功耗。從實用設計實驗獲得的定量結果也支持這樣的理論,亦即阻止速度快但功耗大的模組(如LVT或短通道SVT)會導致面積和時序退化,並間接導致功率退化。

嚴選單元組合 滿足各種要求

過去,人們認為,如果在設計中限制或停止使用功耗更大的LVT單元,就能夠大幅地節省整體漏電功率。EDA優化工具更加證實了這個概念,當用戶選擇為降低功耗而努力時,該工具在多數情況下會用低驅動LVT來交換高驅動SVT/HVT。這種方法的關鍵驅動理念是降低非時序關鍵型單元的功耗與資料路徑。雖然這種方法在現有設計中被廣泛接受,目的是降低功耗,但在整個優化合成過程中限制使用LVT單元所得到的結果並不讓人信服。表1展示了在四種不同的試驗單元VT範圍下的一個測試範例的綜合品質成果(QoR)。

先來比較一下總面積。如果只使用HVT單元,則閘數(Gate Count)和整體設計的面積都會增加。因此,由於驅動強度和規模更大的HVT單元而增加的面積,還會增加設計中其他驅動單元的相對負載,為小幅減少功耗還要增加動態功率。例如,為滿足臨界時序,該工具可能使用三個高驅動AND邏輯閘,將一個3輸入AND邏輯閘部署為一個整合式3輸入AND邏輯閘,這可能不會提高速度。因此,當只有HVT運行時,閘數最大。此外,如果深入分析,限制設計使用SVT和LVT,更可能使總功率增加2毫瓦(mW),如使用更加劣化的時序(-1,130奈秒總負時差),會進一步增加功率損耗。

另一方面,考慮只運行LVT的情況。在這種情況下,儘管已經允許該工具自由地使用速度更快、但功耗更大的LVT單元來減少閘數和面積,但最後的晶片面積卻幾乎完全相同。之所以有如此令人驚訝的結果,是由於已為合成工具提供速度更快的單元,簡化了時序收斂(Timing Closure),最後該工具採用更大的單元,在重組優化面積方面付出的精力較少。

現在,考慮一下在混合單元配置運行時只使用HVT和SVT。將功耗略大的SVT和HVT單元相結合,所產生的合成QoR要比功耗大的LVT或純保守的HVT版本所產生的合成QoR更好。該時序相當於只運行LVT,同時保留與只有HVT組合時類似的功率配置。此外,面積比使用之前所述組合的情況時要小得多。此外,最後一輪是漸進式LVT運行,使用從HVT+SVT組合獲得的合成QoR結果,進一步提高時序配置,同時依然保持類似的面積和功率配置。

此處所示的結果支援的論點是,遞增式使用速度快但功耗大的單元的最佳混合組合來實現時序關鍵型優化,並利用功率保守型、中等效能的單元來實現總優化,設計人員可獲得最高效的單元選擇,實現低功耗設計。由於單元域的轉變趨勢是包含速度更快、功耗更大的單元(高通道長度LVT和低通道長度SVT),因此會達到一種平衡,設計人員可決定選擇正確的單元組合來滿足目標面積、時序和功率要求。

面積/速度/功率 皆須仔細考量

面積、速度和功率這三個要素都是實現SoC開發目標所需的關鍵和重要因素。物理設計團隊須要在物理實施週期內部署SoC時平衡這三個要素。在實施上述測試範例時,物理實施團隊觀察到,合成階段的技術映射應只透過HVT單元完成,在後續不斷增加的優化過程中,可增量使用SVT和LVT單元,而這種方法通常可為設計提供最佳QoR。

(本文作者任職於飛思卡爾)