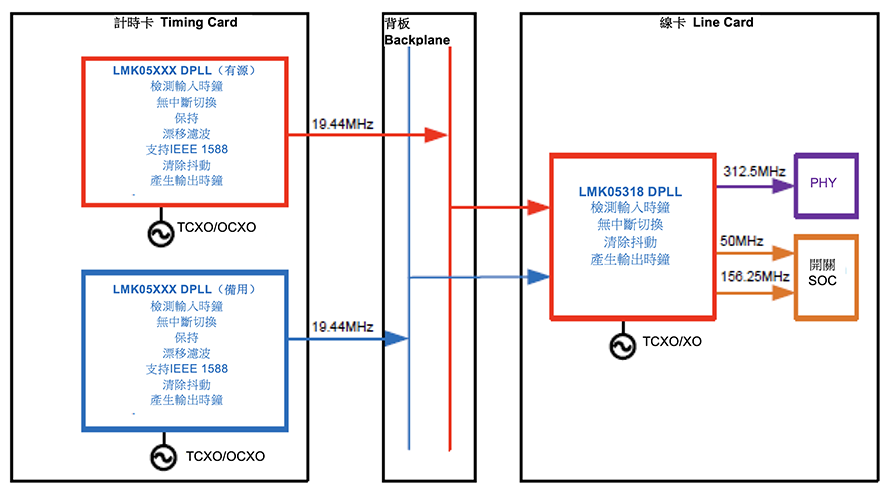

整合數位鎖相環(DPLL)的網路同步器可根據收到的網路時鐘生成潔淨的輸出時鐘,並分配給各種子系統,是通訊網路設備中的關鍵元件。圖1展示了網路同步器用於典型通訊設備(如路由器和交換機)的計時卡和線卡。為了滿足ITU-T G.8262等通訊標準的要求,網路同步器被用於檢測有效輸入時鐘、濾波器輸入時鐘漂移及提供無中斷切換、保持功能。低雜訊時鐘是鎖定到外部晶體參考振盪器(XO)的類比鎖相環(APLL)或溫度補償晶體振盪器(TCXO)或恆溫晶體振盪器(OCXO)而產生的。

圖1 網路同步器用於通訊設備計時卡和線卡的簡圖

圖1 網路同步器用於通訊設備計時卡和線卡的簡圖

網路同步器的關鍵技術規格之一是輸出時鐘整合均方根(Rms)抖動,它整合在各種通訊標準規定的特定頻段內。隨著資料流程量劇增,通訊網路資料速率不斷提高,為了滿足嚴格的訊噪比(SNR)/誤碼率(BER)要求,確保具良好的設計裕量,所需的網路同步器輸出時鐘抖動變得越來越具有挑戰性。

例如,隨著通訊網路系統的傳輸速率從每秒100Gbps提升至現在的每秒400Gbps,系統設計人員要求在12kHz至20MHz(TJrms_12kHz_20Mhz,包括雜散)頻段內網路同步器的輸出時鐘最大總均方根抖動小於150fs。為求簡化,在以下針對輸出時鐘總均方根抖動的討論中,積分頻寬始終為12kHz至20Mhz並包括雜散。

先進的網路同步器積體電路(IC)通常以整合的高頻LC VCO為基礎,產生輸出時鐘。VCO相位雜訊受到其整合LC槽的品質因數(FOM)限制,最佳化後品質因數一般約為20~30。假設LC VCO被環路頻寬很窄(如100Hz)的PLL鎖定,則輸出時鐘均方根抖動可能為幾百fs或更高(主要由LC VCO相位雜訊來決定),因此無法達成150fs的要求。

為了獲得更好的均方根抖動,設計人員可以增加APLL環路頻寬,讓VCO的近端相位雜訊衰減。然而,由於分數N APLL具有類比特性,APLL固有的帶內相位雜訊會受到模擬缺陷的限制,並且容易受到工藝、電源、溫度(PVT)變化及串擾效應的影響,晶體參考振盪器的相位雜訊也會受到限制。因此,增加APLL環路頻寬超出一定範圍,能讓APLL固有的帶內相位雜訊和晶體參考振盪器相位雜訊成為主導因素,藉此防止總均方根抖動進一步降低。此外,增加APLL環路頻寬還會降低分數N雜散和量化雜訊的濾波,進而降低總均方根抖動性能。

LC VCO為基礎的網路同步器積體電路採用低雜訊高頻(如48Mhz) XO,為實現最小均方根抖動而選取的最佳PLL環路頻寬一般為幾百kHz或更高,所產生的最大總均方根抖動約為150fs或更高。由於這些原因,LC VCO基礎的傳統網路同步器正成為400Gbps和未來更高速通訊系統的性能瓶頸。

LC VCO基礎的傳統網路同步器的另一個缺點,是必須使用高頻低雜訊晶體參考振盪器來最佳化總均方根抖動。為了滿足某些系統對保持精度的嚴格要求(例如ITU-T G.8262規定Sync E的最大精度為+/-4.6ppm),選用TCXO或OCXO比常規的未補償XO要好。但是,可靠的高頻低雜訊TCXO或OCXO不易取得且通常價格不斐。因此,系統設計人員必須在時鐘相位雜訊/抖動性能、保持精確性和總體解決方案成本之間進行權衡。

為了解決此一難題,設計人員可以運用以體聲波(BAW)技術為基礎的LMK05318網路同步器積體電路解決方案。該裝置採用與矽積體電路共同封裝的高Q值BAW諧振器,形成超低雜訊整合壓控BAW振盪器(VCBO)。2.5GHz VCBO近端(1kHz~100kHz)相位雜訊比現有的LC VCO改進了10∼20dB。創新的BAW技術大幅降低了同步輸出時鐘相位雜訊/均方根抖動,因而達成了最大均方根抖動小於150fs的嚴格要求,且具有充分的裕量,不僅超越了400Gbps系統的要求,也有利於未來向400Gbps以上的資料速率邁進。此外,該解決方案無須使用低雜訊高頻TCXO或OCXO,因此降低了總體解決方案的成本。

挾超低雜訊優勢 新BAW諧振器受矚目

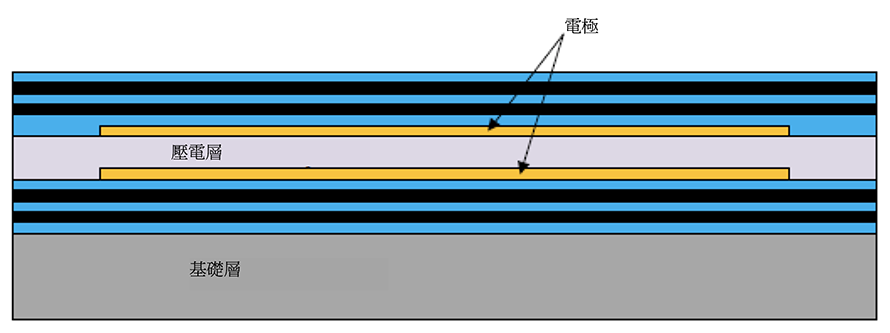

多年來,工作頻率高達幾GHz的小尺寸BAW諧振器一直應用於行動應用,例如無線收發器射頻前端的濾波器。BAW諧振器是一種壓電薄膜諧振器,其運作與石英晶體相似。如圖2所示,壓電薄膜夾在兩個金屬電極和幾個聲學反射器之間,可以限制機械能,最終形成非常穩定的高Q值諧振器槽。

圖2 體聲波諧振器的基本結構

圖2 體聲波諧振器的基本結構

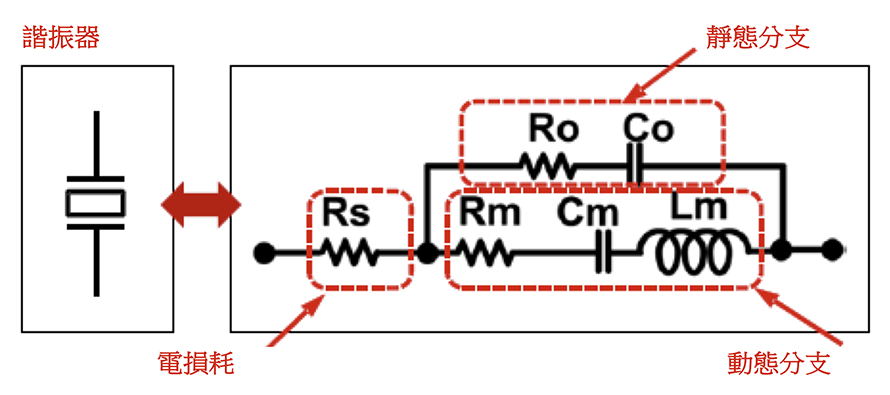

BAW諧振器的電等效性可以透過MBVD(Modified Butterworth-Van Dyke)模型來反映,如圖3所示。與傳統的晶體諧振器一樣,BAW諧振器具有並聯諧振頻率Fp和串聯諧振頻率Fs。

圖3 MBVD模型,BAW諧振器的電等效性

圖3 MBVD模型,BAW諧振器的電等效性

經過各研發團隊多年的聯合研發工作,德州儀器(TI)最佳化了高頻高Q值BAW諧振器的設計,同時解決了與矽積體電路共同封裝的難題。2.5GHz VCBO使用的BAW諧振器的典型品質因數為1200。

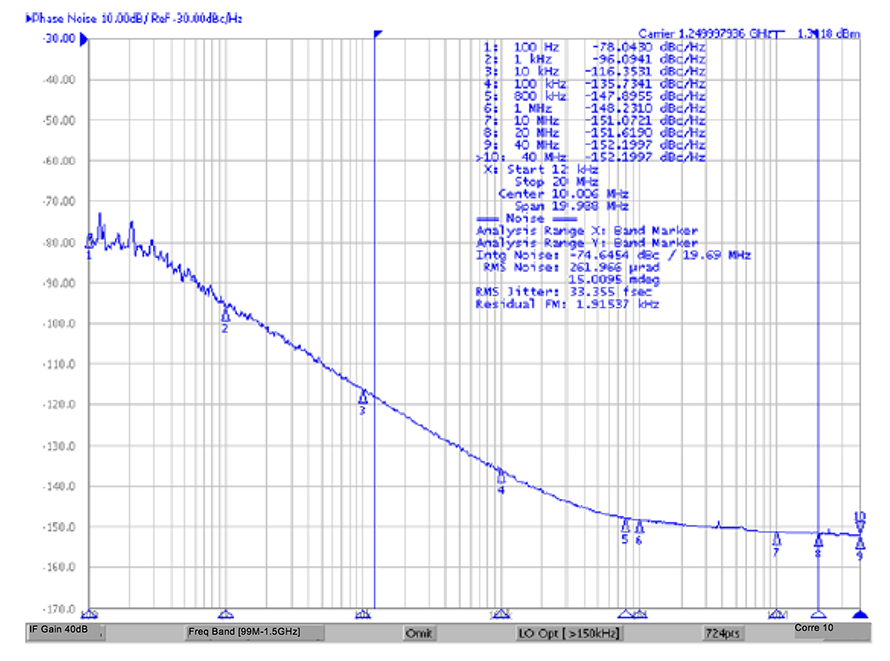

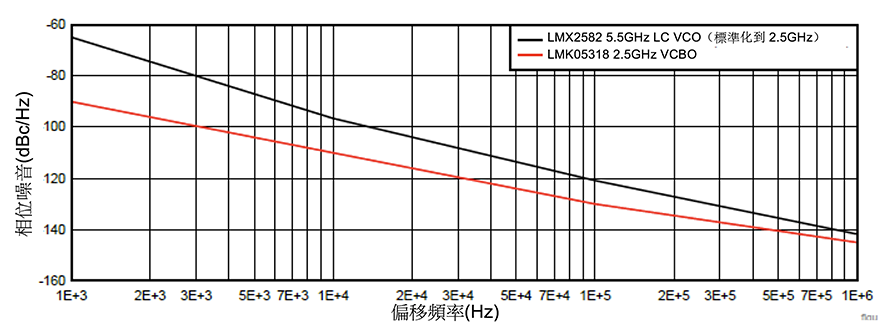

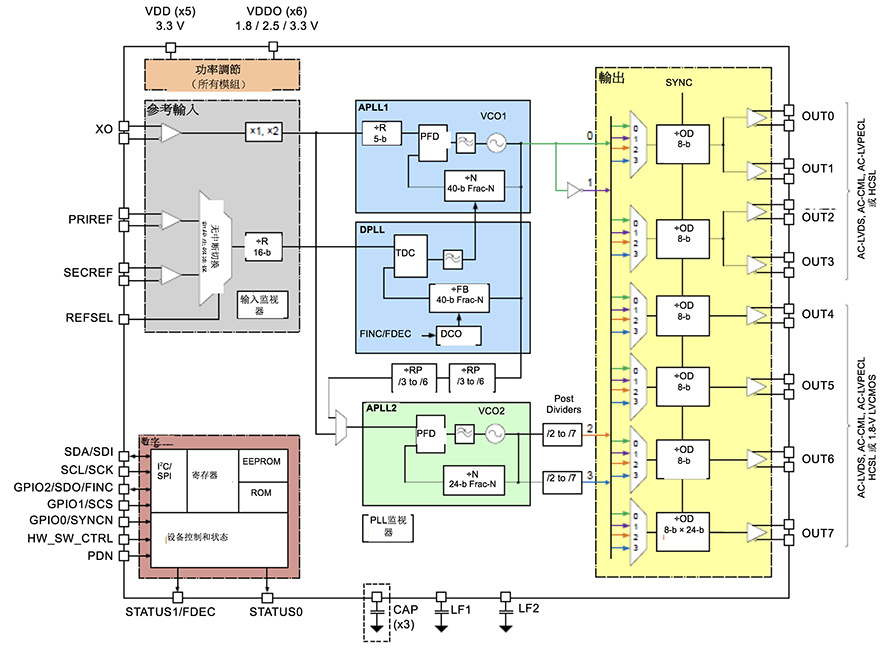

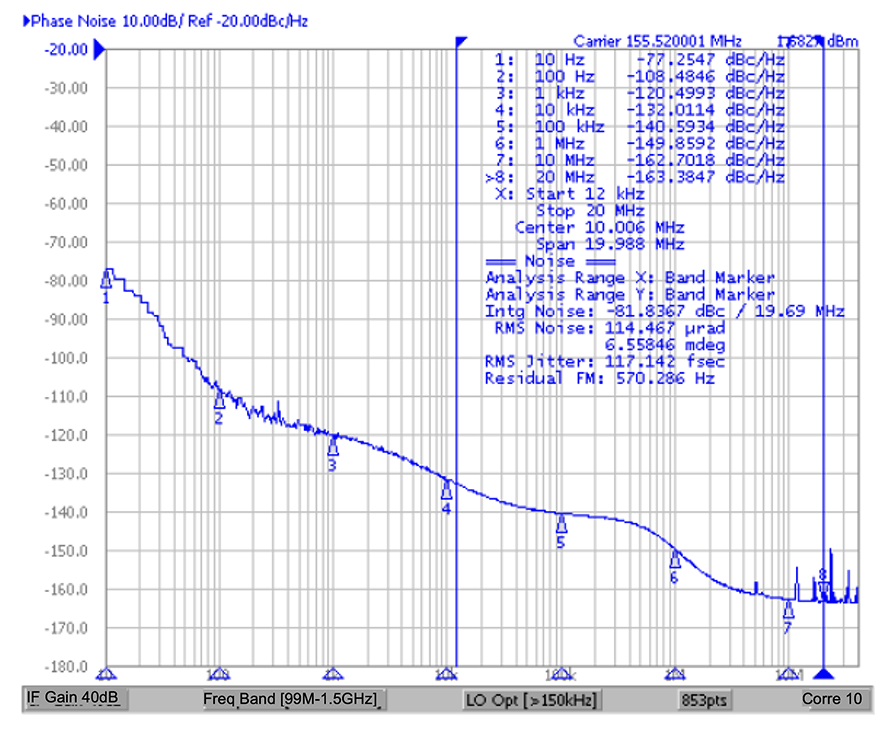

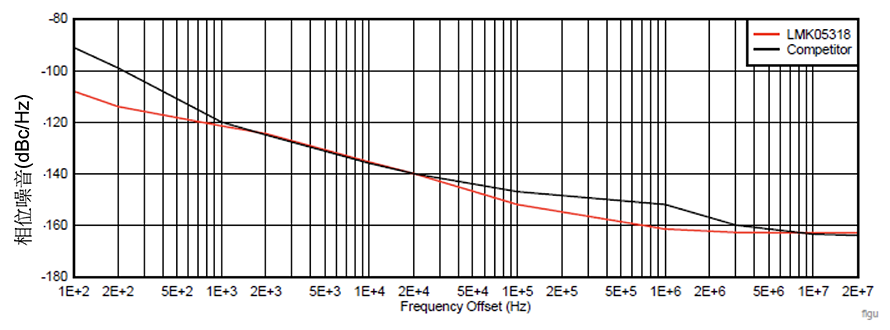

以創新BAW技術為基礎的典型2.5GHz VCBO,在1.25Ghz輸出頻率下的總均方根抖動約為33fs,如圖4所示。LMK05318 2.5GHz VCBO與LMX2582現用的LC VCO的相位雜訊性能比較結果(標準化到2.5GHz),如圖5和表1所示。2.5GHz VCBO近端(1kHz~100kHz)相位雜訊比現有的LC VCO改進10~20dB,明確展現了VCBO的相位雜訊/抖動優勢。建立在此卓越的低相位雜訊VCBO技術基礎上,LMK05318等超低抖動網路同步器產品,達成400Gbps系統等先進高速通訊網路的嚴格要求。

圖4 典型2.5GHz VCBO的相位雜訊(在1.25GHz載波頻率下測量)。總均方根抖動約為33fs。

圖4 典型2.5GHz VCBO的相位雜訊(在1.25GHz載波頻率下測量)。總均方根抖動約為33fs。

圖5 比較LMK05318 2.5GHz VCBO與LMX2582現用的LC VCO(標準化到2.5GHz)的相位雜訊性能

圖5 比較LMK05318 2.5GHz VCBO與LMX2582現用的LC VCO(標準化到2.5GHz)的相位雜訊性能

網路同步器最佳化 提供超低抖動時鐘

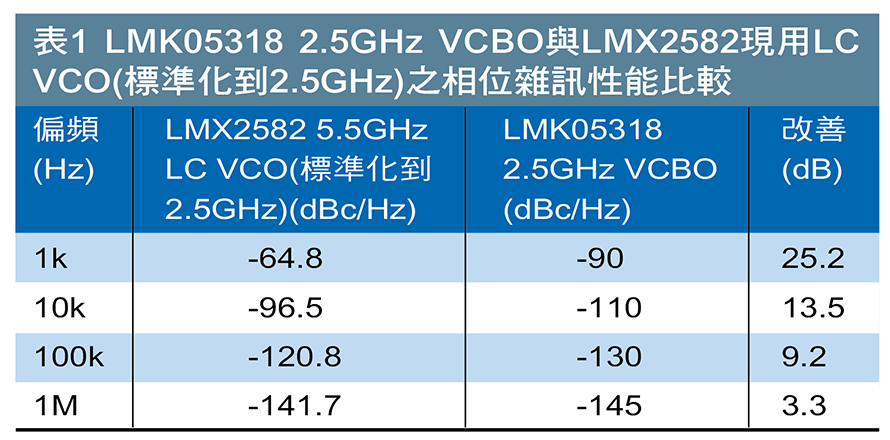

LMK05318是一款商用網路同步器,它利用整合在標準QFN封裝中的高頻高Q值BAW諧振器和矽積體電路,形成可產生超低抖動時鐘的VCBO。LMK05318超低抖動網路同步器的晶片級設計參考圖如圖6所示。

圖6 LMK05318的簡化晶片設計參考圖

圖6 LMK05318的簡化晶片設計參考圖

LMK05318具有完全可程式設計的DPLL內核,可提供輸入時鐘檢測/監控、漂移/抖動濾波,並支援最佳的無中斷輸入時鐘開關和保持功能。可以在啟用DPLL的正常運行模式、禁用輸入時鐘的保持模式或自由運行模式下工作,並滿足ITU-T G.8262等各種通訊標準的要求。具有片上電子式可清除程式化唯讀記憶體(EEPROM)、片上LDO等特性,使它的配置和操作都非常簡單。

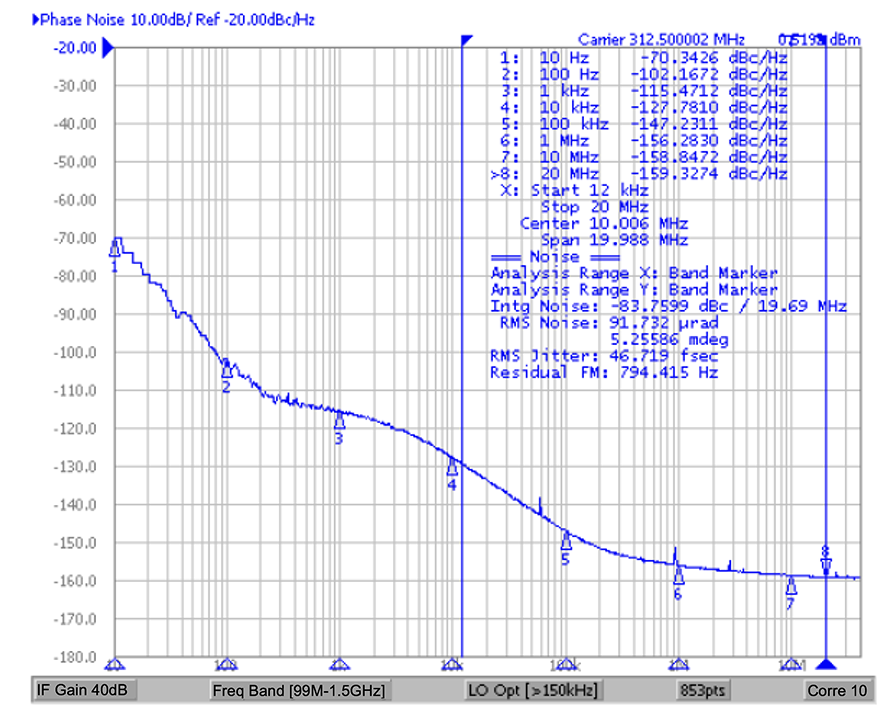

APLL1的VCO1是2.5GHz VCBO。PLL1產生的輸出時鐘實現了同類最佳的輸出時鐘均方根抖動和相位雜訊性能。如圖7所示,312.5Mhz輸出的典型總均方根抖動約為47fs。

圖7 典型的DPLL/APLL1 312.5Mhz輸出相位雜訊。TJrms_12_20Mhz約為47fs。

圖7 典型的DPLL/APLL1 312.5Mhz輸出相位雜訊。TJrms_12_20Mhz約為47fs。

具有5.5~6.25GHz LC VCO的APLL2則可以產生無法直接從2.5GHz VCBO產生的時鐘。在APLL2的155.52Mhz輸出頻率下,總均方根抖動約為118fs(圖8)。

圖8 典型的APLL2 155.52Mhz輸出相位雜訊。FVCO2=5598.72Mhz,APLL2 FPD=2500Mhz/18=138.8⋯Mhz。TJrms_12_20Mhz約為118fs。

圖8 典型的APLL2 155.52Mhz輸出相位雜訊。FVCO2=5598.72Mhz,APLL2 FPD=2500Mhz/18=138.8⋯Mhz。TJrms_12_20Mhz約為118fs。

優異中頻帶相位雜訊 支援低頻TCXO/OCXO/XO

如圖9所示,LMK05318的中頻相位雜訊(10kHz~1MHz)明顯優於使用LC VCO的傳統解決方案,因為它主要由VCBO近端相位雜訊控制,並且沒有寬頻帶APLL1產生的雜訊峰。這在無線巨集蜂巢基地台類型的系統中是一個很大的優勢,此類系統在某些頻率偏移處需要滿足嚴格的時鐘中頻帶相位雜訊要求,如800kHz偏移處的MC-GSM相位雜訊等。

圖9 比較LMK05318與LC VCO基礎的傳統網路同步器之CLKout相位雜訊

圖9 比較LMK05318與LC VCO基礎的傳統網路同步器之CLKout相位雜訊

如圖7所示,由於採用了超低雜訊VCBO,LMK05318透過幾kHz的APLL1環路頻寬實現了輸出時鐘超低抖動,這意味著外部XO/TCXO/OCXO相位雜訊對總均方根抖動的影響較小。LMK05318可以使用低頻(如10~20MHz)TCXO/OCXO/XO,且不會對總均方根抖動產生顯著影響,降低了總體解決方案成本。相比之下,傳統解決方案必須使用低相位雜訊的高頻(約50MHz)外部TCXO/OCXO/XO,價格通常更昂貴。

穩定相位雜訊性能 優異總均方根抖動

LMK05318的輸出時鐘總均方根抖動不太容易受到工藝、電源、溫度(PVT)變化的影響。首先,LMK05318輸出時鐘總有效值抖動主要由VCBO相位雜訊決定,不容易受到APLL帶內相位雜訊和外部TCXO/OCXO/XO相位雜訊的影響。相比之下,LC VCO基礎的傳統寬頻APLL解決方案,其總均方根抖動容易受到APLL帶內相位雜訊和外部TCXO/OCXO/XO相位雜訊的影響。請注意,分數APLL的帶內相位雜訊對非線性調製敏感,因此會隨著PVT變化而發生顯著變化。

其次,對於傳統解決方案,APLL的寬環路頻寬(至少幾百kHz)使得濾除分數雜散和分數PLL量化雜訊變得更加困難。相比之下,對於具有窄環路頻寬APLL(幾kHz)的LMK05318,可以輕鬆濾除分數雜散和分數PLL量化雜訊,從而產生較低的輸出時鐘相位雜訊/抖動。

性能不打折成本再降低 創新BAW同步器提供最佳良方

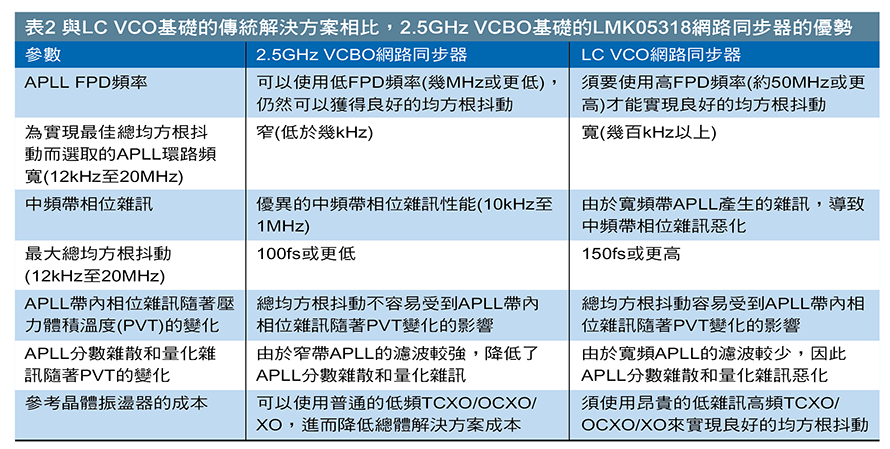

隨著通訊網路的資料速率不斷提高,對網路同步器的輸出時鐘抖動性能也具更高要求,而LC VCO基礎的傳統解決方案已經難以滿足這些要求。建立在創新BAW技術上的新型網路同步器LMK05318,目標為有效改善LC VCO基礎的傳統解決方案的相位雜訊/均方根抖動性能。BAW諧振器採用互補式金屬氧化物半導體(CMOS)相容工藝,並與標準QFN封裝的矽IC晶片整合。2.5GHz VCBO近端(1kHz~100kHz)相位雜訊比現有的LC VCO改進了10~20dB,明確展現了VCBO的相位雜訊/抖動優勢。在1250MHz輸出頻率下的輸出時鐘典型總均方根抖動為33fs,在312.5Mhz輸出頻率下為47fs。該網路同步器的輸出時鐘最大總均方根抖動小於100fs,超越了高速400-Gbps通訊網路對均方根抖動的嚴格要求。與LC VCO基礎的傳統解決方案不同,此網路同步器可使用頻率較低、成本較低的普通TCXO/OCXO,從而降低了總體解決方案成本。表2總結了2.5GHz VCBO基礎LMK05318網路同步器的其他優點。

(本文作者皆任職於德州儀器)