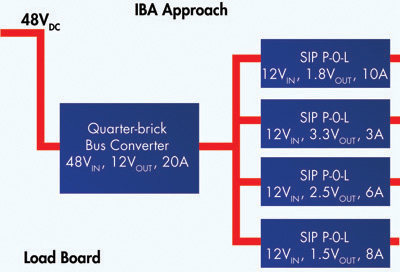

通訊電路板常常採用負載點(Point of Load, POL)直流對直流(DC-DC)轉換器來為數位晶片,如現場可編程閘陣列(FPGA)、數位訊號處理器(DSP) 及特定應用半導體元件(ASIC)供電。一般而言,一個48伏特的背板採用中間匯流排架構(IBA)作為電路板的輸入電源(圖1),為不同負載點供電,而中間電壓通常選為12伏特。

這種傳統方案包含一個離散式負載點轉換器,該轉換器是以離散的方式使用控制器、驅動器和金屬氧化物半導體場效電晶體(MOSFET)。由於這種架構需要額外的設計和製造時間,故半導體供應商現已開始轉為採用完全整合的調節器解決方案,以縮短上市時間,減小印刷電路板(PCB)空間,並使終端應用達到更高的效率水準。本文將對這兩種新舊方案進行探討,並深入分析新方案為設計人員和消費者帶來的優勢。

|

| 圖1 傳統POL供電架構採用大量離散元件 |

數位元件數量持續成長 傳統供電架構捉襟見肘

在過去兩年中,數位晶片的輸入電壓下降速度非常快速,例如內核電壓(Vcore)已經從1.8伏特降至1.2伏特,並將很快在2009年底或2010年初降至1伏特。此一趨勢使得本地POL調節器所扮演的角色更加重要。

為了因應內核電壓的下降所帶來的挑戰,轉換器必須減短印刷電路板上的銅布線長度,才能提供這種極小的壓降。因此,數位晶片的電源應該緊靠控制器/驅動器放置,而其所搭配的外部MOSFET則圍繞在數位晶片四周,以保證設計的尺寸小巧。

通常這類負載點供電電路設計都採用相同的線路布局,設計人員只須根據系統需求的負載電流不同而調整採用對應的MOSFET,以實現設計重用,縮短工程師耗費在供電電路上的設計時間。

然而,隨著電路板上數位晶片增加,供電系統所須支援的獨立輸出電壓數量也隨之上升,這意味著電路板上為供電目的所採用的元件數量將無可避免地成長,對系統的成本與尺寸帶來負面衝擊。

事實上,根據電源晶片商觀察,由於PCB板上整合的功能越來越多,目前許多電路板上的單路輸出電壓已從四路輸出倍增到八路以上,其所帶來的設計挑戰不言可喻。

電源模組SiP化帶來顯著性能優勢

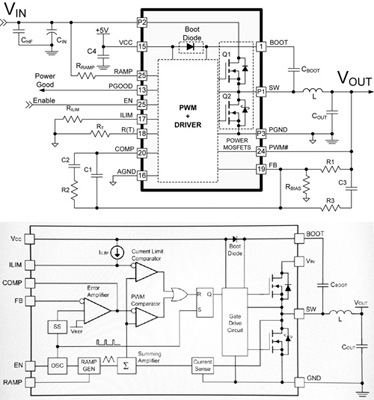

由於存在這些棘手的問題,許多同時擁有控制器和MOSFET專業技術的半導體供應商現在開始把這些功能整合在一個封裝,亦即所謂的系統封裝(SiP)技術(圖2)。

|

| 圖2 採用SiP封裝後,POL供電模組的外部電路變得非常簡潔 |

這類產品組合通常具有相同的封裝和接腳輸出,但能夠提供不同的負載電流。這種元件封裝方式讓系統設計人員可以在不更改電路布局的前提下靈活地改變供電系統的負載能力。設計人員現在基本上能夠選擇一個封裝尺寸,通過調換產品就可以滿足其系統的特殊負載要求。

利用這種整合式方案,供應商在進行晶片設計時,就可以將封裝時的內部打線(Bond Wires)最佳化納入設計考量,藉此將封裝阻抗減至最小,且由於供應商在控制器設計之初,就可以確認與之搭配的MOSFET規格,因此在設計過程中,即可針對常用的12伏特輸入和低於3伏特的輸出進行最佳化,以實現最佳效率。

例如在12伏特輸入電壓和1.2伏特輸出電壓的設計限制條件下,這類整合型方案的高側(High Side)MOSFET工作週期(Duty Cycle)可達到10%。這點在系統最佳化上具有非常重大的意義,因為晶片供應商若有能力將高側工作週期壓低到這個水準,就可以在高側端選用較小的MOSFET(適當的低Qg),連帶使得低側(Low Side)受益於大晶片尺寸,可把導通電阻(RDS(ON))降至最小,因為低側的傳導時間達90%。

除了MOSFET得以最佳化之外,若供應商在低側MOSFET晶片上整合了蕭特基(Schottky)二極體,還可提高寄生二極體的快速恢復時間,進一步提高效率。這些因素都有助於降低開關損耗和改善熱性能。最後,從模組性能的角度來看,由於控制器、驅動器和MOSFET更緊密地放置在一起,能夠使寄生效應最小化,從而減少開關雜訊、振鈴現象並縮短開關時間。

這些性能最佳化優勢對於設計人員而言非常關鍵,因為隨著眾多強制性的高能源效率標準相繼問世,效率已經成為設計中最關鍵的考慮事項。這些整合式元件可讓設計人員優化開關頻率和負載電流,從而改善熱性能。

這種方案能夠減少散熱、增強可靠性,並提高特定設計的可靠性。隨著半導體供應商持續推出這類具有高性能和高效率、更小封裝尺寸,而且更易於設計導入的方案,這些SiP化的新一代電源模組被市場採納的速度也將會越來越快。

SiP為電源模組帶來更多價值

除了性能面的改善外,電源模組改採系統級封裝也讓供應商可以進一步提升這類元件的附加價值,例如傳統的負載點方案必須採用離散式的方式才能實現過熱、過流、過壓等一系列保護功能,但新型的整合式電壓調節器方案可在不使用外部元件的前提下輕鬆實現上述保護功能。

縮小印刷電路板占用空間也是這類整合式方案所能帶來的價值。表1顯示採用完全整合方案所減少的占位面積,比較這類完全整合方案(以FAN2108為代表)和完全離散或部分整合的同類元件。

表1 各類負載點供電模組占用空間比較

從結果可知整合式方案所占用的電路板面積減少多達60%。這對於協助設計人員實現更精巧的產品設計或降低生產成本有莫大助益。

整合式方案勢在必行

電源設計人員在元件選擇時,不再只是單就成本或性能進行考量,不可或缺的要素還包括易於設計、有利於提高系統效率及節省電路板空間等。當電源設計人員在MOSFET和驅動器及控制器的匹配方面所花費的時間越少,那麼用於實際設計的時間就越多,這對於加快上市速度是非常重要的。這也是近來為何在負載點電源方案市場上掀起一股SiP風潮的主要原因之一。

此外,隨著業界的效率意識日益增強,而且必須滿足各種嚴苛的法規條例,高效率、高性能整合式解決方案對電源設計人員的吸引力也會越來越大。因此,對於像是負載點這類應用而言,SiP化的理念將會受到越來越多供應商認同,從而形成一股潮流。

(本文作者任職於快捷半導體)