為滿足日益增長的行動資料需求,第三代合作夥伴計畫(3GPP)長程演進計畫(LTE)標準已演進至LTE-Advanced,因而也為高能源效率行動元件設計工程師帶來新的挑戰。因此,嵌入式處理器、矽智財(IP)供應商安謀國際(ARM)與嵌入式數位訊號處理器(DSP)內核的供應商CEVA合作提出分析報告,共同探討實現下一代行動無線寬頻設備所須考慮的設計因素。

本文首先將探討3GPP第十版標準(亦即LTE-Advanced),在輸送量限制、低延遲以及低功耗方面的具體設計挑戰;而後,將檢視系統級設計,例如節能模式、除錯和追蹤,以及多模式操作的支援。

電信業者啟動LTE-A網路布建

LTE標準第八版於2008年12月由3GPP正式通過,提供無線寬頻接入,是第一波LTE設備的建構基礎。現在,LTE已獲包括美國、日本、韓國和中國大陸在內的一百零四個國家、超過三百四十七家營運商採用,讓該技術成為史上被採用速度最快的行動寬頻技術。

LTE-Advanced與3GPP標準第十版及更新的版本有關。該標準建立在現有的LTE第八版標準之上,並且保持向後相容性。LTE-Advanced增加可滿足上述所列許多新特性的要求,最關鍵的是,LTE-Advanced還符合國際電信聯盟(ITU)通過的4G無線技術正式定義。

表1說明3GPP第十版標準中定義的用戶端設備(UE)分類。從表中可看出,分類範圍很廣,這讓設備製造商可根據終端應用和市場提供產品。雖然Cat-8(UE Category 8)具有吸引市場目光的高資料輸送量,但事實上,在現實中很難部署Cat-8,因為該規格需要高達100MHz頻寬(LTE網路目前在10M~20MHz頻寬中部署),至今,沒有任何電信營運商具備此種寬廣的頻寬。從更實際的觀點來看,相較於Cat-8,UE Cat-7將是一種會被廣泛採用的案例。

|

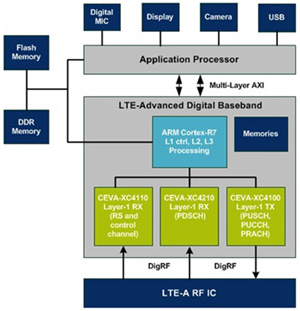

| 圖1 使用者設備的上層方塊圖 |

圖1簡單地呈現LTE-Advanced數據機如何在智慧型手機設計中連接,並為本文討論的數據機設計提供前後關聯安排。

LTE-Advanced數據機包含接收和傳輸訊號處理鏈,而該技術通過寬頻射頻(RF)收發器IC為無線介面服務。LTE-Advanced訊號處理分成數層,如3GPP規範中所定義的,其中Layer 1提供與訊號成功傳輸和接收有關的所有低階訊號調節,Layer 1的典型功能包括前向誤差改正、交錯和位元串流操作,星座-調變(Constellation-modulation)、MIMO編碼、OFDM訊號調變和射頻IC訊號調節。此處所描述的Layer 1全部功能均屬於DSP的範疇,同時需要在中央處理器(CPU)實現的控制和管理功能。

|

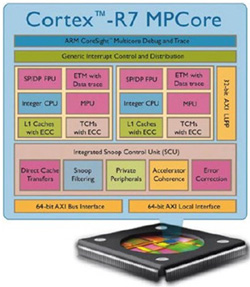

| 圖2 即時處理器方塊圖 |

上層處理在Cortex-R7處理器中執行,並且以圖1中的Layer 2和3表示。Cortex處理器執行媒體存取控制(MAC)、分封資料匯聚協定(PDCP)、無線鏈路控制(RLC)和無線資源管理(RRM)等功能,並與應用處理器介接。

兼具高傳輸速率/低延遲特性

即時處理器為數據機首選

Cortex-R即時處理器(圖2)可提供3.9G/LTE和4G/LTE-Advanced基頻任務所需的高性能、確定性回應時間和卓越的能源效率,並具有為高輸送量、低延遲無線系統提供尖端計算性能的能力,以及先進的低功耗設計,因而成為數據機設計的首選元件。與LTE-Advanced基頻架構特別相關的即時處理器特性如下。

| ‧ |

|

| |

即時處理器提供2.53DMIPS/MHz性能,可滿足最嚴苛的基頻處理要求。 |

| ‧ |

|

| |

即時處理器包含偵測控制單元(SCU),在饋入到記憶體內的數據機資料和處理器的資料高速緩衝記憶體間自動保持一致,可節省大量的軟體負擔,以及即時應用處理器間的一致性規定。 |

| ‧ |

|

| |

即時處理器特別針對數據機硬體的快速控制,額外加一個AXI(Advanced eXtensible Interface)匯流排埠,而不會被主AXI匯流排上的大量資料處理阻斷。 |

| ‧ |

|

| |

低延遲隨機存取記憶體(LLRAM)區域被用於保持關鍵軟體和資料,例如中斷服務程式(ISR)幾乎能夠立即執行,不須等待主AXI匯流排處理完成與/或ISR進入Layer 1的高速緩衝記憶體。 |

| ‧ |

|

| |

一種有限的記憶體資源(128KB),適用於可以存取的最關鍵代碼和資料,不存在因AXI匯流排埠所引起的延遲,為即時硬體如LTE Layer 1實體層提供最高層級的確定性回應。 |

| ‧ |

|

| |

在處理器間實現靈活的中斷分布及快速中斷,如從空中介面/CEVA域到ARM的路由。 |

| ‧ |

|

| |

特別適合即時處理器的中斷模式,在少至二十個週期內中斷,例如用於時間關鍵的空中幀處理。 |

| ‧ |

|

| |

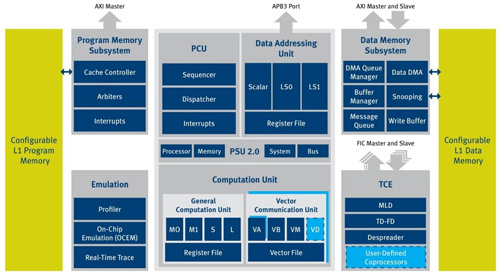

雖然即時處理器支援對稱多重處理(SMP),但還可在SCU模組內配置服務品質(QoS),每個處理器對選定範圍的記憶體與輸入輸出(I/O)位址擁有優先存取權,而不會被其他處理器阻斷。另外,業者推出的DSP內核(圖3)的特點是結合非常長指令字(VLIW)與透過先進向量處理提升典型DSP能力的單指令多資料(SIMD)引擎。這種可擴展的架構讓軟體定義的數據機設計可以最少的硬體實現。 |

|

| 圖3 DSP方塊圖 |

LTE-A UE數位基頻架構面面觀

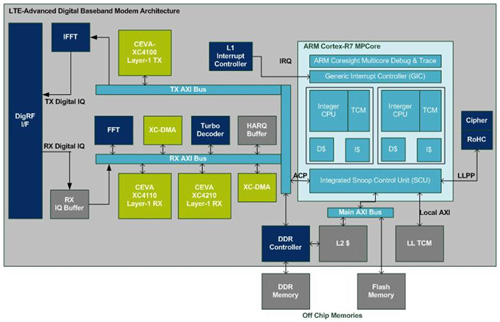

圖4是完整的LTE-Advanced數據機設計,該系統基本上是由雙核Cortex處理器上的Layer 1 Tx處理鏈、Rx處理鏈和Layer 2/3處理所組成。Layer 1的控制處理也在即時處理器上執行,並提供接收和發送功能的低階即時控制。

|

| 圖4 LTE-Advanced UE數位基頻架構實例 |

LTE-Advanced的布建帶來一些相當嚴苛的設計挑戰,特別是要滿足高輸送量支援、低延遲性能,以及低功耗要求,本文所提出的架構用到多種先進技術,可以幫助設計工程師因應這些挑戰,而不會犧牲性能。

減少外部記憶體存取以降低功耗

雙核即時處理器具有本地記憶體,是特別為加速Layer 2處理的即時功能及Layer 1的控制功能而設計。藉著利用低延遲本地記憶體,例如Layer 1和Layer 2的高速緩衝記憶體,晶片外記憶體存取次數可減到最少,從而顯著降低整體系統的功耗。

另外,每個即時處理器內核還具有TCM,可以儲存時間關鍵中斷程式,從而使其可以確定性方式執行,這在因應LTE-Advanced低延遲系統定時挑戰方面非常重要。即時處理器兩個內核均擁有各自本地Layer 1的指令高速緩衝記憶體,可協助提高各個內核的執行效率,使得系統能夠讓程式執行得更快,從而迅速回到節能模式。

此外,即時處理器內核藉著將成本昂貴的晶片外記憶體存取需求降到最低,讓各個內核停留在節能模式的時間更長,從而降低整體的系統功耗。

在設計系統單晶片(SoC)時,設計工程師必須要特別注意記憶體和匯流排架構,以避免因設計瓶頸而要在性能方面付出高額的代價,或者,因為增加規格不合適的晶片內部記憶體,而使得晶片面積增加,並提高功耗,從而使解決方案變得昂貴。

藉由細心的設計,利用各種晶片內和晶片外記憶體,即時處理器和DSP架構可實現性能、成本與功率的有效平衡。

主要的AXI匯流排提供對系統快閃記憶體和同步動態隨機存取記憶體(SDRAM)構件的存取,SDRAM通常是晶片外部資源,但通常會藉由晶粒堆疊整合到基頻封裝中,以節省印刷電路板(PCB)面積。快閃記憶體是用來啟動整個系統,在啟動期間,即時處理器將配置DSP子系統,並將所有的記憶體初始化。

表2歸納出在LTE-Advanced數據機設計中預期會看到的典型記憶體類型。從表中可以看出,HARQ緩衝記憶體和IQ接收緩衝器在基頻晶片中所占的面積越來越大。HARQ緩衝器是用來重組接收到的資料,由於資料以軟位元形式儲存(一個1或一個0的對數似然比),而不是二進位位元,因而對記憶體的要求快速擴展。至於在縮小HARQ緩衝器體積的壓縮技術方面,設計時工程師應考慮要將緩衝器放置在晶片外部SDRAM中,以縮小數位基頻晶片的尺寸及降低其成本。

DSP和即時處理器的結合有助於將通過系統的處理延遲時間縮到最短,還可以提供優化的匯流排互連,這也有助於實現此類記憶體的優化。

LTE-A軟體分層各有特性

|

| 圖5 LTE-Advanced數據機軟體映射 |

圖5是LTE-Advanced數據機的典型軟體映射。從圖中可以看出,Layer 1處理分為發送和接收,其中一個DSP管理發送路徑,接收器內有兩個DSP。

Layer 1用於對空中傳輸的資料進行編碼/解碼,可透過自我調整調變和編碼將輸送量最大化,以及透過多個方案,包括前向誤差改正、交錯和HARQ緩衝器等將最大化穩健性。

HARQ是一種管理選擇性重新傳輸(Selective Re-transmission)不正確接收資料的方案,為管理此一過程,UE須具有HARQ緩衝器。由於LTE-Advanced的高資率和低延遲要求,緩衝器必需相當大,並且須小心地管理,以將最終裝置的成本降到最低。

即時處理器中,低階Layer 1控制器可為Layer 1調度提供服務,該功能是非常具有時間關鍵性,通常在0.5毫秒(ms)的LTE子幀位準上運行。事件由源於Layer 1/空中幀(Air Frame)事件的通用中斷控制器(GIC)驅動,中斷用於Tx和Rx相關處理的即時處理器。中斷源的數量主要取決於Layer 1實施,但是,饋入Layer 1控制器的中斷數量範圍為十幾個至一百多個。

控制器的用途是管理進出Layer 1的資料流及提供從上方堆疊向下流動的所有必要控制資訊。對利用TCM和低延遲管道架構,以及為時間關鍵任務提供有保障的執行時間的任務而言,即時處理器就特別適合此一任務。

即時處理器管道架構和分支預測器,有助於優化中斷回應時間,提供確定性行為,在具有嚴格的即時限制時,例如在無線系統中,確定性行為非常關鍵,由於即時處理器沒有記憶體管理單元(MMU),因此,也不需要複雜的頁表行動操作,當中斷發生時,頁表行動操作將會進一步將回應向後推延。

AMP是Cortex-R7處理器中提供的功能,用來對服務品質進行配置,從而使每個處理器對選定範圍的記憶體與I/O位址擁有優先存取權,讓某種功能和內核比其他功能和內核擁有較高的優先權,因此不會被其他處理器阻斷。

CCI負責記憶體一致性管理

圖5所示各層映射是一個例子,可用來說明工程師如何充分利用即時雙核處理器的架構,在兩個處理器內核間載入平衡任務,進而協助在軟體中保證低階即時要求。

即時處理器的高速緩衝記憶體一致互連(Cache Coherent Interconnect, CCI)整合多處理架構,提供一致的可編程模型,並消除多核環境的設計複雜性。高速緩衝記憶體一致互連管理Layer 1和Layer 2的記憶體,使其保持一致性,而與即時處理器內每個內核各自的記憶體存取無關。這種架構的結果提供一種安全且穩健的記憶體系統,通過這種系統,程式設計工程師不須對高速緩衝記憶體一致性進行管理,從而在兩個內核實現無縫的任務轉移,保持最佳的負載平衡/功率效率。

VoLTE增加數據機軟體需求

傳統上,語音服務是以2G和3G網路以線路交換方式完成,但是,隨著營運商尋求重新劃分2G和3G頻譜到LTE,需要統一的機制傳輸語音。現在,VoLTE標準處於早期部署階段,有幾家營運商已進行部署,其中包括宣稱全球首家提供這種服務的韓國電信。VoLTE的優勢是,可從單一LTE網路提供語音和資料服務,而不須傳統標準的多模支援,由於頻寬能力更高,使得營運商能夠提供高解析度語音。加入VoLTE,增加對LTE-Advanced數據機的軟體要求。

降低功耗至關重要

對於任何蜂巢數據機設計來說,為最大限度地降低電池的消耗和外形尺寸(透過減少熱限制),降低功耗不可或缺。LTE-Advanced標準本身整合多種節能模式,如使UE在閒置狀態時進入節能模式,UE電源狀態可以簡單地歸納如下:

| ‧ |

|

| |

UE處於完全工作模式,所有或大多數模組均上電,一個典型的應用案例是視頻通話、視頻串流或TCP/IP資料傳輸。在此模式中,即時處理器和DSP子系統均上電,支援上行和下行資料傳輸以及相關的訊號傳輸。 |

| ‧ |

|

| |

VoLTE是由LTE空中介面上的標準化語音編解碼/分層訊號所組成。語音支援帶來小型分封傳輸和接收(小且偶爾的資料傳輸),使得UE在閒置時能夠執行節能操作,即時處理器將管理整體節能方案,因為其了解語音分封的調度,從而可據此相應地安排DSP進入和退出節能模式。此外,由於即時處理器的多重處理能力,VoIP軟體及LTE協定軟體可在同一台裝置上實施,藉由關閉其他處理器,可讓系統節能的範圍更寬廣。 |

| ‧ |

|

| |

在這種場景中,UE沒有任何主動的資料會話(Active Data Session),但是資料會話保留在網路上執行定期同步/位置更新操作,由於LTE標準是包括節能的架構,即時處理器可根據收聽廣播通道或傳輸位置更新資訊,將UE帶進及退出節能模式。 |

在節能模式期間,除被配置成在合適時間喚醒系統的低功率定時時脈外,UE幾乎全部關斷。

支援多頻多模 數據機全球漫遊非夢事

隨著LTE和LTE-Advanced的推出,伴隨而來的是在單一UE內支援舊網路連通性的需求,包括2G和3G寬頻分碼多重存取(WCDMA)/增強版高速封包存取(HSPA+)及TD-SCDMA在內的舊標準,將伴隨LTE繼續存在許多年。

隨著LTE標準繼續演進,舊的3G網路還會支援高速的連通性,這是網路營運商戰略的固有部分,在運行LTE的同時,也支援HSPA+等服務。

在實施基於高功效和小外形尺寸設計的基本要求的多模式UE時,工程師須滿足一些重要的設計因素。為支持覆蓋LTE和3G基頻的切換和多基頻RF,多模UE須支援至少兩個或三個並行的空中介面。

DSP和即時處理器可提供高效的多模式支援,並在同一內核支援2G、3G、LTE與LTE-Advanced的通用架構,為促進多模式運作,覆蓋各自的基頻,數據機需要更大的資料和可編程的TCM記憶體,以及三種射頻實例。

追蹤和除錯功能扮要角

隨著基頻SoC變得複雜,SoC須具備先進的即時除錯和分析能力。為使SoC整合和除錯變得簡單,DSP外部匯流排介面採用標準AXI和APB介面的開放式AMBA協定,這可以簡化系統連通性,不需除錯專用匯流排和在不同的處理器技術間進行橋接。

利用標準嵌入追蹤模組,DSP提供包括交叉觸發的多內核除錯、真正硬體平台的即時分析及支持即時追蹤等功能。利用多內核除錯器,DSP與即時處理器支持全面的共除錯(Co-debugging)功能,以簡化SoC設計。

標準通常會比進入市場的產品提早3~5年提出,因此,工程師須做出許多設想,如假設其他技術也將發展,從而有助提高新標準的經濟效益。一般說來,隨著製程的進步,晶片每平方毫米可容納更多的電晶體,但仍須創新,以確保方案具有最高效率。

(本文作者依序為安謀國際行動部門經理、資深產品經理、CEVA基頻與連通性產品行銷副總裁)