隨著科技的日新月異,消費者對電子產品的期待越來越高,促使業者不斷的推出更「聰明」的產品,也使得高度運算、高效能需求與日俱增。在這樣的趨勢下,8位元微控制器(MCU)已不敷使用,也因此32位元微控制器的成長動能受到相當大的關注。市場調查的資料顯示32位元微控制器的營收在未來1、2年將超越8位元微控制器,成為微控制器市場的主流。此外,隨著通訊、網路與多媒體的需求帶動消費性電子功能升級,數位訊號處理器(DSP)的重要性,也隨著MCU的升級而逐漸的被突現出來。

早在1996年,便有深耕於32位元微控制器的業者開始整合DSP與精簡指令集運算器(RISC),推出低成本、高效能、低功耗的微控制器。目前該系列微控制器已經應用於通訊、汽車的電機控制、工業控制、機器人應用、語音處理、生物識別、導航、NAND快閃(Flash)記憶卡、數位相機、IP攝影機(IP-CAM)等。

屏棄雙核心架構 成本/設計簡化有優勢

由於此類控制器在開發初期即以成本為主要考量,因此除了少數對效能要求較高的關鍵部分外,其他設計都盡可能簡化。圖1為新式32位元MCU的基本架構。

|

| 圖1 在RISC單核心架構中增加DSP執行單元的新式32位元MCU架構 |

不同於以往業者採用的DSP加上RISC的雙核心技術,該控制器在RISC單核心架構上增加一個DSP執行單元,這樣的架構毋須考慮雙核心架構彼此的溝通問題,也不必為了共用記憶體與周邊裝置而增加額外的硬體線路,這個架構大約只需要三萬五千個邏輯閘便能夠實作出來,如此一來,不但降低硬體設計的難度,也節省了許多的成本。

精簡指令集提供同等效能

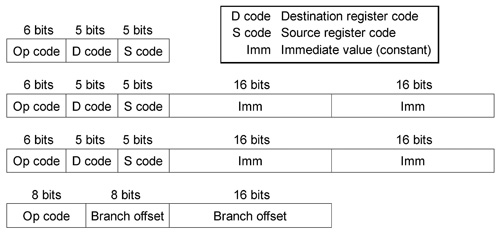

除了架構精簡,在RISC單核心架構上增加一個DSP執行單元的MCU指令集也有獨到之處。指令長度主要為16位元,但是可以根據立即運算元(Immediate Operand)或移位(Displacement)的需求而擴充為32位元或48位元(圖2)。這種指令格式編譯出來的結果比一般固定為32位元指令的RISC架構來得小。

|

| 圖2 不同位元之指令格式 |

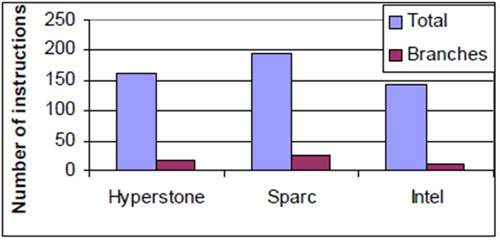

Papaefstathiou et al. (IEEE 2004)在針對可程式化通訊協定處理器(Programmable Protocol Processor, PRO3)架構的測試中,同樣的程式片段在針對編碼尺寸(Code Size)作最佳化之後,這類簡化的MCU與複雜指令集(CISC)架構已相差無幾,也比同為RISC架構的Sparc系統來得好(圖3)。編碼尺寸小除了意味著可以節省記憶空間外,還代表減少對外部記憶體的讀取次數而提高效能,也可以在固定的指令快取(Instruction Cache)中存放較多的指令。

|

資料來源:Papaefstathiou et al. IEEE 2004

圖3 不同架構下的指令數 |

與一般追求高速的處理器不同,為了降低成本,這類精簡型MCU指令快取記憶體並不大。但是該MCU把指令快取設計成同時具有快取跟緩衝區(Buffer)的功能,配合高效率的預取(Prefetch)演算法,加上處理器每一次都從記憶體讀取兩道16位元的指令,它的擊中率(Hit Rate)可以媲美擁有大快取記憶體的系統。

一般而言,越高速的處理器其管線(Pipeline)架構會越複雜,也會分越多級。但是也有產品能只用二級的管線架構就達到一樣的效能。由於指令格式的一致性相當的高,指令的提取(Fetch)跟解碼(Decode)在一個周期就能完成,第二個周期就開始執行,而且幾乎所有的標準指令只需要一個周期就可以執行完畢。

另外,因為此類32位元MCU的運算與邏輯單元(ALU)與DSP被設計成相互獨立的執行單元,所以標準指令與DSP的指令可以平行執行。二級管線架構的好處是可以在分支(Branch)指令後很快的將管線重新填滿。而多級的管線架構需要更久的時間才能重新填滿管線,這意味著執行效能降低,否則就是要增加硬體線路度與成本在系統中加入分支預測(Branch Prediction)以維持所需要的效能。

靈活運用暫存器

暫存器的使用相當有彈性,採用新微控制器架構的方案,提供了六十四個32位元的區域暫存器,這些暫區域存器通常會被規畫為堆疊空間。在呼叫副程式時,系統會分配六個暫存器給堆疊使用,返回位址與要傳遞的參數會自動的存入堆疊暫存器中;而從副程式返回後,被占用的堆疊空間會自動被釋出。然而每次呼叫副程式後堆疊暫存器的數目並不是固定不變,使用FRAME這個指令可以設定堆疊暫存器的數目,最高可以有十六個。

這種設計的好處是只須要填寫暫存器就可以執行副程式,不需要Push或Pop運算,尤其在處理中斷時,這樣的架構可以得到相當短的反應時間。以圖4為例,(a)假設主程式分配了十個暫存器來作堆疊,而Parameter 1與2是要傳給副程式的參數。(b)在呼叫副程式之後,預設的情況是系統會分配六個暫存器給副程式使用,也就是新堆疊器的大小,堆疊底部的指標(FP)也自動移到新堆疊器的底部,而要傳遞的參數依然存放在原來的暫存器中。(c)接著呼叫FRAME指令,把堆疊長度設為9(假設需要九個),並將堆疊底部的指標也指到新的位置以便將欲傳遞的參數包含進來,如此一來,副程式的呼叫與參數的傳遞就完成了。另外,編譯器會根據FRAME指令的設定值,自動將暫存器的使用做最佳化,如果堆疊暫存器的數目不足,系統會自動將較舊的堆疊內容備份到外部記憶體去,需要時也會自動從記憶體取回,完全不需要使用者操心。

|

| 圖4 呼叫副程式時的堆疊架構 |

除了區域暫存器外,採用新架構的MCU還具備全域暫存器與特別暫存器。全域暫存器有程式計數器,狀態暫存器等,一般而言,全域暫存器可以當成區域暫存器來使用,並不需要特殊的指令來存取。特別暫存器主要是用來設定計時器、看門狗(Watchdog)、中斷及匯流排介面的一些行為,此外還能透過特別暫存器來讓處理器進入低電壓(Power-down)模式來達到省電的功能。

記憶體的存取也被設計成二級的管線架構,這意味著一筆32位元的資料可以在一個時脈周期就可以完成讀取或寫入。記憶體位址或是待寫入的資料都會被轉移到位址管線或是資料管線中,執行時跟實際的記憶體存取無關。處理器只有資料在載入(Load)指令之後馬上須要用到該筆資料,或是資料管線仍被占滿的情況下,才會插入等待的指令。

將DSP執行單元融入單核心架構中是採用新架構的32位元MCU的一個特色,設計團隊在規畫DSP運算單元時便與軟體開發人員以及數學家密切合作,遵循RISC的原則來開發適合數位訊號處理的指令。

為了建立最佳化的DSP指令集,設計團隊研究了許多的數位訊號處理演算法,並分析這些演算法使用暫存器的情形、記憶體需求量、還有執行迴圈時所消耗的資源。這些努力成就了這個能夠與其他運算單元密切合作的DSP運算器。設計團隊更針對濾波器、快速傅立葉轉換、離散餘弦轉換與反轉換等運算來最佳化這個DSP指令集,而這些演算法幾乎在所有多媒體應用中都會遇到。

另外,因為是主攻低價市場,這個RISC/DSP架構針對16位元的定點運算做最佳化。在多媒體的應用中,16位元是最有用的格式,例如醫療影像須要處理12位元的畫素,而在低階的影片中用的是8位元的畫素,這些都可以用16位元的格式來涵蓋。

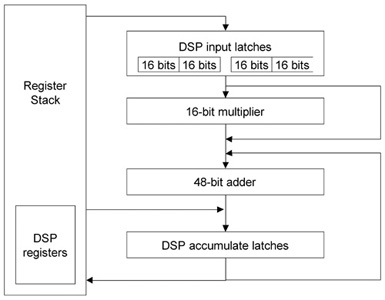

DSP的核心是一個乘法-累加器,在管線的架構中針對數種資料格式提供乘法、乘法-累加、乘法-減法、加法-減法運算(表1與圖5)。雖然這個架構針對16位元運算作最佳化,但仍允許32位元的運算,而且效能依然相當好。另外還有32位元以及64位元的累加器各一個,並且從一般暫存器中分配兩個暫存器供累加器使用。此外,與記憶體的整合是DSP架構很重要的部分,此基於新架構的MCU備有內部記憶體(On-chip RAM),這是微處理器邏輯位址空間的一部分,內部記憶體的存取時間為一個時脈週期。

表1 DSP指令概觀

|

| 圖5 DSP的架構圖與資料路徑 |

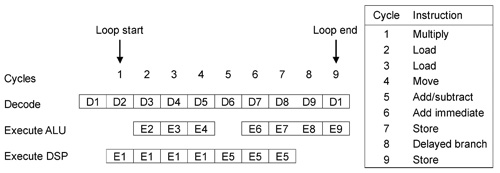

為了讓效能更上一層樓,新的32位元微處理器架構中,邏輯運算(ALU)與DSP是獨立平行運作的。ALU執行載入(Load)/儲存(Store)運算、迴圈計數、位址運算,而同一時間DSP可以做乘法、乘法-累加、加法-減法等運算。圖6用一個常見DSP演算法的內部迴圈來描述平行運算時管線中的情形。

|

| 圖6 執行FFT某內部迴圈時管線狀態示意圖 |

周邊匯流排同扮要角

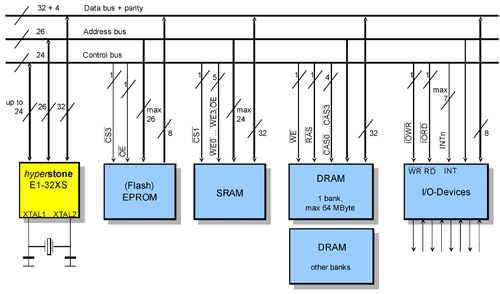

要設計出擁有良好成本效益的系統,功能齊全而架構精簡的匯流排介面也是很重要的一部分。在控制系統或嵌入式系統中,一個有效率的介面必須在不增加額外硬體的情況下而能加入特殊功能的元件。為了讓系統盡可能的精簡,精簡的32位元MCU提供了所需的訊號來連接外部記憶體與周邊設備,不需要額外的硬體線路或元件。圖7所顯示的是一個常用的建構方式。

|

| 圖7 新MCU的系統架構範例 |

在這個架構下,記憶體空間被切成四個區塊,每個區塊有1GB。其中一區專門用來對應到動態隨機存取記憶體(DRAM),內部的控制器能夠直接提供存取DRAM所需要的訊號,因此外部的DRAM可以直接與處理器連接而不須增加任何的邏輯線路或硬體。至於DRAM的分頁大小(Page Size),更新速率(Refresh Rate)等其他參數,都可以透過內部的控制暫存器來加以設定。其他的區塊可以用來連接SRAM或ROM,存取的時脈參數一樣可以依需求設定或變更。

此外,所有區塊資料匯流排的寬度也可依照系統需求設為8、16或32位元。常見的做法是把速度較慢開機用的ROM掛在8位元匯流排上,而把速度需求較高的主記憶體匯流排設成32位元。

除了先前提到的四個記憶體區塊,處理器還提供獨立的輸入/輸出位址空間。即使是連接周邊設備,處理器一樣會產生所需要的訊號,這樣更能使系統設計更加的簡化。

除了成本與效能,產品的開發週期也是客戶在選擇微處理器時的一個主要考量。目前已有業者不僅可以提供客戶相關產品的矽智財(IP),還能提供標準的IC產品。因此,客戶可以先採用標準IC進行小量測試或出貨,等到產品經過相關認證後,再採用IP開發自己的系統單晶片(SoC)或特定應用積體電路(ASIC),不但縮短開發時程,更節省許多開發成本。這也是一般IP業者尚未提供的服務。除了提供標準的IC,廠商亦提供完整的軟硬體開發環境與免費的即時作業系統(表2),可供運作。

| 表2 位準轉換技術比較 |

| elopment board |

Software profiler |

| Serial connector interface |

Source-code debugger |

| ANSI C Compiler |

Real-time system |

| Assembler |

DSP-Library |

| Linker |

System configuration tool |

| Library manager |

Third-party tools and software |

整體而言,採用新架構的32位元系列微處理器的主要目標是追求價格與性能的最佳化,盡其所能的保持簡單的架構而不犧牲效能,藉由可延伸的指令長度(16、32或48位元)、二級管線架構,以暫存器來實作堆疊、整合DSP運算單元、記憶體存取管線架構、內部記憶體以及低耗電模式來實現低成本、高效能與低功耗。表3為此系列其中一個型號的效能評比。

| 表3 新式32位元MCU XSRU的性能評比(0.18μm製程與16Kbyte on-chip RAM) |

| Clock: up to 240 MHz @ 1.8 V internally |

| Performance: 240 MIPS, > 900 MOPS |

| 1 k CFFT in less than 0.21 ms |

| Current at full speed: 50 mA |

| Power-Down Current < 0.5 mA @ 1.8 V |

| Sleep Mode Current < 50 μA |

| < 0.41 mW / MHz |

| 2 mm2 die-size excl. pads |

優異的性價比、在商用領域與利基市場的測試與考驗,以及成熟、高效率的開發平台等優點,對於想從8位元微控制器進階到32位元微控制器的客戶相當有吸引力。而這類MCU也為嵌入式系統與消費性電子產品提供了理想可靠的選擇。

(本文作者為海派世通研發部協理)