現場可編程閘陣列(FPGA)與高速串列器/解串列器(SERDES)兩種技術結合之後,開發出經SERDES改善的FPGA,若印刷電路板(PCB)、背板或電纜內需要Multi-Gigabit數據連結,可做為符合成本考量的特定應用積體電路(ASIC)替代方案。此種新式可編程元件正改變許多產品設計方式,進一步追求低功耗與低成本。這種彈性、可客製化裝置不僅能縮短開發時程,亦方便工程師設計「敏捷型」產品,可依據快速變遷的標準升級,或隨客戶需求調整。

為運用經SERDES改善的FPGA獨特功能,設計師必須稍加理解其運作原理,以及溫度、電氣、訊號完整性需求。採用嵌入SERDES的FPGA產品系列後,幾種重要議題可能會影響以SERDES為基礎的元件性能,本文將協助讀者認識這種新式元件及其優點,並介紹成功應用所需的設計方式,同時提供可用於設計內的實用解決方案。

本文介紹的諸多議題,均使用3.25Gbit/s SERDES收發器核心,可應用於市面上許多經SERDES改善的FPGA產品內,同時亦會討論新一代FPGA的獨特功能,以改善系統效能與設計彈性。

成本媲美傳統設計 FPGA整合SERDES功能更強

結合嵌入式SERDES收發器的FPGA已問世10餘年,原本是為營運商網絡設備的高效能封包處理及路由元件開發。這些功能強大的大型元件內,採用製造商旗艦級的產品線架構與製程,每一片要價數百甚至數千美元。後來製造商運用10年來次微米半導體製程的進步成果,才得以進一步滿足對成本更加敏感的新興應用市場需求。

這些超值中低密度FPGA具備前代頂級產品多數效能與功能,且容量選擇更具彈性。新一代的FPGA優點包括低耗能、定價具競爭力、封裝密度高,方便設計師選擇產品所需的可編程元件與應用硬體核心數量,故FPGA的設計解決方案總成本與許多應用的傳統設計相當。

此外,若FPGA策略運用得當,設計師能擺脫傳統開發循環內許多障礙。藉由降低開發成本、縮短開發時程、排除與特定應用IC相關的彈性及特定應用標準產品(ASSP)供應商的供應鏈問題,FPGA將能幫助設計師迅速因應浮現眼前的市場商機。

SERDES助臂力 FPGA擴大進軍網通/工業應用

低功耗multi-Gigabit SERDES收發器核心與價格合理的FPGA結構相結合,能為各種應用建立多功能解決方案平台,擴大使用各種以SERDES為基礎的介面,例如乙太網路(XAUI, GbE, SGMII)、PCIe(PCI Express)、SRIO(Serial Rapid IO)和通用公共射頻介面(CPRI)等。其中包括小型基地台無線基礎架構、微型伺服器、寬頻存取、工業影像及大量要求低成本、低功耗和小封裝的設計應用。

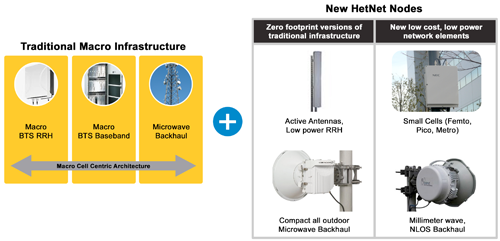

|

| 圖1 異質網路主要構成架構 |

早期許多應用若採用經SERDES改善的FPGA,均屬於創新射頻(RF)、基頻(Baseband)與回程(Backhaul)網路產品,以滿足無線網路營運商需求。世界各地營運商雖大舉投資升級基礎架構,但仍難以趕上行動數據與影音流量需求增長速度,因此,除升級現有基地台以支援高容量4G無線標準外,許多營運商亦開始發展異質網路(HetNet)結構,並在傳統大型基礎架構之外,另搭配新式低功耗節點(LPN),如小型基地台、低功耗遠端無線電站和繼電器等(圖1)。

這些小型、低功耗(通常介於100毫瓦(mW)~10W之間)無線節點能為高流量地區增加容量,或延伸無線覆蓋範圍至一般基地台難以企及的建築物、公共空間及都市峽谷。低功耗節點因此必須極具彈性,同時支援多種空中介面標準與射頻,具備體積小、不易損壞的特點,隱身於都市環境內;還得價格低廉,滿足廣泛建置的需求。

經SERDES改善的FPGA在許多方面對小型基地台的設計都有利。在某些低功耗毫微微型蜂巢基地台(Femtocell)(100mW~200mW)內,運用小型經SERDES改善的FPGA,搭配基頻系統單晶片(SoC)功能,或許比較符合成本效益,再加上JESD207介面,可連接至射頻類比前端。

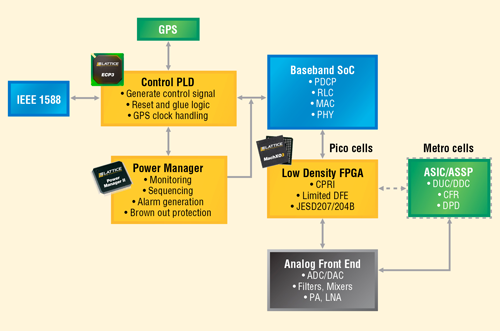

|

| 圖2 一般超微型/大型基地台功能簡圖 |

另一方面,室內超微型基地台(~1W)幾乎總能從FPGA中獲益,在小封裝內可結合高速邏輯、SERDES、彈性輸入/輸出(I/O)介面、數位訊號處理器(DSP)功能(圖2)。可編程邏輯元件可用於有限數位前端(DFE)功能,如峰值因數縮減(CFR)。在使用基頻系統單晶片的超微型基地台設計中,FPGA的SERDES功能可提供必要的CPRI,連接至射頻類比前端。

在以DSP為基礎的超微型基地台設計中,FPGA更可搭配訊號處理器,其I/O元件可應用於低電壓差動訊號(LVDS)/JESD204B介面,連接DSP輸入/輸出處的數據轉換器與射頻類比前端。

大型基地台傳輸功耗最高達5~10W,通常需完整的數位前端解決方案,例如數位預失真(DPD)等功率放大器線性化技術。以成本及耗能觀點而言,合理的方式是在ASIC內加強高運算強度的數據路徑功能(DUC/DDC/CFR/DPD),同時在低密度經SERDES改善的FPGA內,保留可編程連接功能(CPRI、JESD204B、LVDS等)。

在任何低功耗節點產品中,具備SERDES功能的FPGA可用於數據路徑橋接與接入,以封包為基礎的網絡介面(GbE、10GbE/XAUI、XGMII)常用於連接小型基地台叢集與回程網路基礎架構;亦常用於寬頻存取設備內,智慧小封裝可插拔收發器產品的XGMII介面及多數數位功能。

除通訊之外,這些裝置為微型伺服器提供低成本、低功耗的PCI Express旁波帶連接。在用電量低於2W的工業攝影機內,經SERDES改善的FPGA可滿足所有影像處理功能。

SERDES融入FPGA 實現客製化介面

因應市場對小型經SERDES改善的FPGA導入需求,萊迪思(Lattice)已開發出新款ECP5 FPGA系列產品,其與市面上多數經SERDES改善的FPGA相同,使用嵌入式SERDES收發器,提供所需的基線功能,支援多數常用的高速串列介面。

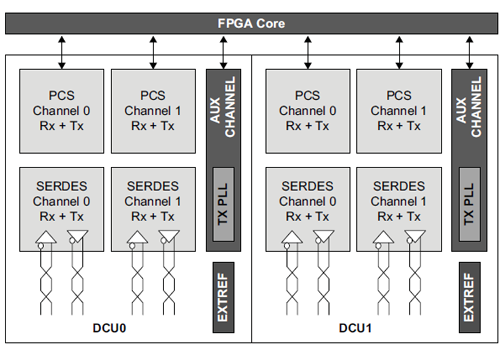

|

| 圖3 雙通道SERDES單元簡圖 |

ECP5系列產品內含的可編程邏輯單元數量不一(最高達85k LUTs),最多包括四部收發器,可兩兩置入雙通道單位(DCU)內,其中包括單一共用參考時脈輸入與輸出鎖相迴路(圖3)。每一SERDES通道均可獨立配置,發揮高速、全雙工串列數據傳輸,數據速率介於270Mbit/s與3.2Gbit/s之間。

經SERDES改善後,FPGA各通道的實體編碼子層(PCS)配置,可支援多種乙太網路介面及常見網路與系統互連標準,由於收發器用電量隨配置及功能而異,並無單一正確數值。若以ECP5的第一階近似值而言,在PCle x1單通道和PCle IP核的用電量約為0.25W;而PCle x4單通道和PCle IP核心的用電量為0.5W以下,為目前業界最低功耗。

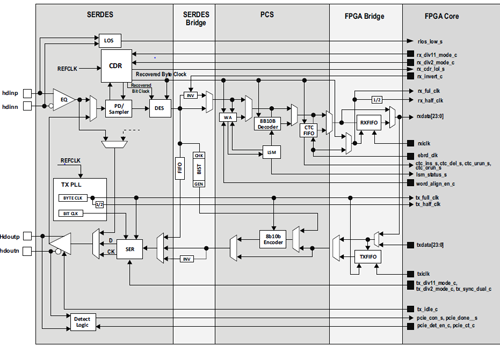

|

| 圖4 LFE5UM SERDES/PCS通道詳細圖解 |

與此同時,FPGA內建軟體矽智財(Soft IP)可搭配SERDES通道使用,以支援高速串列資料連結的協定級功能,例如PCIe、CPRI、SD-SDI、HD-SDI、3G-SDI等。在客製化應用內,使用者可自行決定協定級邏輯,提供高速數據介面設計最大彈性。實體編碼子層亦提供旁路模式,讓SERDES與FPGA邏輯可直接使用八位元或十位元介面,落實自訂數據編碼(圖4)。

運用TRx均衡技術 SERDES克服訊號干擾問題

SERDES訊號橫越印刷電路板或電纜時,常會遇到訊號間干擾(ISI)、衰減、反射等現象,故收發器可透過元件組態暫存器設定,來運用多種發送器與接收器均衡技術。發送器的高速線性驅動器內,擁有可調整的振幅設定與終端電阻值,能依據通道長度造成的衰減來控制,以符合通道走線阻抗,降低訊號反射;也能利用可調整的前後標記解加強設定,發揮傳輸均衡效果,減少因傳輸位元互動或前次傳輸剩餘位元能量殘餘所造成的ISI問題。

在數據率範圍內,有些頻率元件通過印刷電路板或背板時會明顯衰減,接收器內含線性等化器,能刻意放大與補強這些元件,減少接收訊號內可能發生的訊號間干擾。接收器提供四種均衡級別,可依據個別通道輸傳特性選擇。

多數現代FPGA內的SERDES收發器均擁有實體編碼子層(PCS)邏輯,可支援多種特定應用協定如下:

掌握FANOUT製程 密集腳距排列難題有解

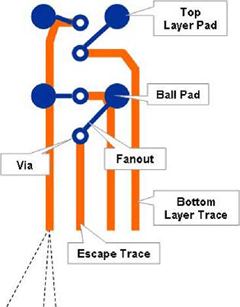

|

| 圖5 現代BGA封裝的密集腳距排列情況,導致高速SERDES通道須特殊設計及PCB規畫難題。 |

經SERDES改善的FPGA實際運用時,多數難題源自於應用空間受限時常採用的球閘陣列(BGA)封裝。雖然本文介紹內容是針對ECP5系列產品封裝的高接腳數及密集腳距(圖5),其實無論是否採用BGA封裝或其他高接觸密度選項(例如TQFP或QFN),任何以SERDES為基礎的裝置均可參考這些訣竅。

若要採用密集腳距(0.8mm以下)的BGA封裝,一大難處在於設計FANOUT模式路線,既要提高I/O用途,同時降低構裝成本。以此接觸密度而言,從內圈球腳規畫跡線時,幾乎勢必得增加額外PCB路由層,或是得犧牲部分球腳。此外,SERDES或DDR3/LPDDR3等高速訊號必須更仔細維持相同間距,以控制跡線阻抗,源極同步匯流排的訊號組跡線也得等長,確保印刷電路板內具備適當接地與隔離層,維持訊號完整性。

|

| 圖6 BGA外接路由特色 |

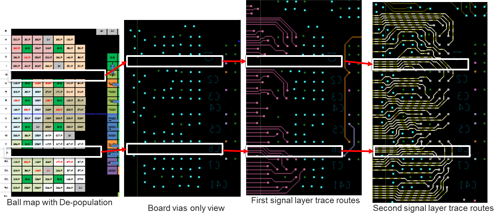

密集腳距封裝兼具優缺點,密度增加就得提高跡線與空間限制。許多設計在BGA下選用跡線較窄,FANOUT時稍微加寬。此時,PCB構裝設備業者必須了解設計目標,並確認可支援的最小跡線寬度,跡線愈窄,就得花愈多時間檢查、檢驗與調校,跡線與空間若調至下限,必須仔細監控蝕刻。混合FANOUT跡線、外散孔與外散跡線後,路由可從BGA接腳陣列下擴散至裝置邊緣,並統整為「BGA外接」(圖6)。FANOUT模式將安排外接路徑、外接層與堆疊,增加最高可使用的I/O數量。

|

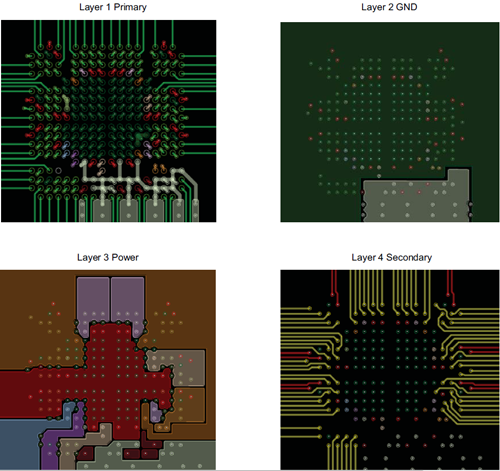

| 圖7 兩百八十五接腳csfBGA四層PCB的CAM配置圖 |

圖7的範例為10毫米×10毫米、0.5毫米間距、兩百八十五接腳csfBGA封裝(LFE5UM-25F-MG285)的ECP5 FPGA,其置入最大I/O應用數量的四層PCB堆疊。在BGA外散路由中,運用4-mil跡線與4-mil間隙,並使用雙內部層做為參考板。本案例不須盲孔或埋孔,可節省成本。

如前所述,只要謹慎安排PCB配置,即可改善諸多訊號完整性與路由問題。不過隨著接觸數量增加,從內圈球腳規畫跡線時,幾乎勢必得增加額外PCB路由層,或是得犧牲部分球腳。以ECP5的caBGA封裝採用0.8mm間隙而言,若未特別考量球腳排列,恐怕很難大幅改善情況。

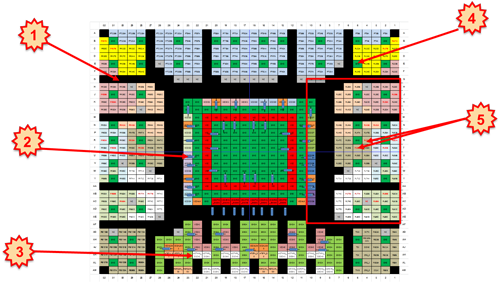

因應這項問題,FPGA業者為0.8毫米間隙的caBGA554與caBGA756設計封裝,並提供新式封裝球腳外接圖樣,繪製自內圈球腳的跡線,其中刻意減少不必要的球腳位置,藉以簡化路由。此外,謹慎安排訊號/電源/接地接腳後,可改善偏斜匹配問題、降低高速訊號匯流排串音,電源/接地接腳配置亦可允許晶片供電接腳實現低電感去耦電容。

FPGA結合SERDES 實現高彈性介面設計

|

| 圖8 caBGA756改善封裝後的接腳配置圖,已標註新特色,可改善跡線路由與訊號完整性。 |

圖8顯示新封裝系統幾項特色,可改善PCB跡線路徑、高速與SERDES訊號完整性、電源接地去耦:

|

| 圖9 上圖為BGA球腳減量後,可減少PCB層,建立更簡潔的跡線路由;下圖為未受干擾的SERDES訊號跡線,更能控制影響訊號完整性的通道特質。 |

雖然經SERDES改善的FPGA目前已大幅減少用電量,冷卻仍可能是一大問題,尤其部分產品多設於戶外,故新封裝設計亦增加鄰近FPGA晶片的接地貫孔數,為PCB提升傳導散熱功能。

圖9上側範例設計中,充分利用接腳減量的優點,縱然加上貫孔,亦僅使用兩個PCB層訊號。圖9上側顯示封裝內排除整列接腳,亦排除接腳所需的貫孔,為訊號路由層建立不受干擾的區域,讓訊號路由彈性更大,可外接至封裝邊緣(圖9左側邊緣)。

此一設計最大優點在於SERDES訊號路由,圖9下側顯示,刻意排除部分接腳後,FPGA高速SERDES訊號將可不受干擾,每一對SERDES訊號跡線長度相當,亦維持準確的跡線間隔,以嚴格控制阻抗。每一對跡線之間,以及與FPGA訊號之間,也受到仔細控制,以壓低串音。

顯而易見,結合可編程邏輯與高速串列資料收發器後,經SERDES改善的FPGA可支援眾多網路及系統介面,同時提供可編程邏輯元件,能彌補或甚至排除一般設計內的ASIC或ASSP。可編程功能不僅建立快速開發週期,也能推出易於升級的產品及彈性平台,支援多種網路及通訊標準。

各種SERDES裝置都對設計流程造成多種挑戰,大多涉及封裝、PCB配置、訊號完整性。不過結合優越設計與新封裝技術後,可確保經SERDES改善的FPGA完全發揮潛力,進而展現在高速傳輸介面設計中的各項優點。

(本文作者任職於萊迪思)