硬體設計並不容易。隨著需要支援的標準越來越多,以及高效能應用的複雜性呈現指數成長,開發人員因此致力於在不斷擴展的標準、協定、規範以及結合更高速的串列資料傳輸之間取得適當的平衡。

無線基礎架構、網路、資料中心、廣播視訊、測試與量測以及工業自動化領域的挑戰,也將影響時脈元件的選擇,因為時脈抖動會對高速串列資料傳輸應用中的誤碼率以及資料轉換器應用中的訊噪比和有效位元數產生負面影響。有鑑於時脈的重要性,一些硬體開發人員和架構師,在設計之初就做出時脈決策,而不是等到後期階段。

每種硬體設計都需要一定程度的時脈解決方案。根據應用需求,解決方案的範圍從簡單的石英晶體振盪器到更高整合度的時脈元件。在元件選擇方面並沒有一體適用的策略。

一個常見的問題是,如何決定何時使用振盪器或時脈,因為每種方法都有利弊。另一個同樣具有挑戰性的問題是,如何為特定應用選擇適當的時脈元件?最好的方法是按照時脈數量、頻率和訊號格式(例如差動或單端)列出所有系統層級時脈需求。對時脈性能要求嚴格的資料轉換器、乙太網路交換器、PHY以及FPGA收發器來說,重要的是了解每個時脈的相位雜訊或抖動規範。有了這些資訊,就可以使用簡易的清單準確找到適合應用的元件。

選用振盪器之時機

最簡單的時脈產生來源是振盪器(XO),它產生單個輸出時脈。通常,當系統只需要一個或兩個時脈參考時,最好選擇XO。XO選擇標準是基於所需頻率、下游裝置的抖動容許量和ppm穩定性。除了關注封裝尺寸和效能之外,另一個越來越重要的標準是電源雜訊抑制能力。傳統的石英晶體振盪器通常需要外部低壓差(LDO)穩壓器提供穩定的電源和低抖動時脈。在開關模式電源應用中,使用基於PLL的振盪器是有利的,因為這些振盪器內建電源調節,消除離散式LDO。另一個考量因素是PCB布局。在某些設計中,最好在本地產生所有時脈,如緊鄰下游的SoC、FPGA、ASIC與PHY。這種方法能夠優化傳輸線和訊號完整性,並且無需在高密度封裝的電路板上布線時脈。

最後,不能忽略交貨週期這項因素。傳統客製化頻率振盪器的交貨週期可能將近14周以上。PLL振盪器的另一個好處是它們的交貨週期較短(1周以內)。

選用時脈之時機

根據一般經驗,當應用需要三個或更多時脈參考,且目標IC都在同一電路板上時,時脈元件優於振盪器。如果所需的時脈具備相同的頻率和訊號格式(單端或差動),則可以使用簡單的時脈扇出緩衝器。若是應用需要多頻率和/或訊號格式,則應使用PLL時脈產生器。在許多FPGA、ASIC應用中,這些元件有多個時脈域,用於資料路徑、控制層和記憶體控制器。這些應用非常適合時脈產生器。大多數時脈產生器應用都是自由運行的,其中內部PLL及其相關的輸出時脈與石英晶體或XO輸入同步。自由運行時脈的應用範例包括處理器、記憶體控制器、SoC和周邊元件(例如PCI Express、USB)等。

某些應用需要同步時脈確保來源和目的以相同的頻率運行。對於同步應用,建議使用抖動衰減時脈鎖定參考時脈,衰減時脈訊號上的抖動,以消除不需要的雜訊,為下游裝置提供低抖動輸出時脈。時脈IC內的窄頻PLL實現了抖動濾波功能。這些抖動消除器通常用於有線和無線基礎設施應用,以及需要多個攝影機和視訊來源以在導播室內保持適當同步的廣播視訊應用。

開發者選用時脈方案時的主要考量。

開發者選用時脈方案時的主要考量。

整合時脈元件提升系統可靠度

使用整合時脈元件相較於使用多個晶體振盪器有許多優點。透過單個元件替換系統中的多個潛在故障點,可以簡化設計,提升整體層級可靠度。此外,用單個IC替換多個元件也具備成本優勢。但是,必須考慮一些需要權衡的因素。集中式時脈元件所產生的所有時脈訊號仍然需要在整個電路板上進行路線布線和分配。設計者應該使用優化訊號完整性的最佳作法,例如時脈路線用差分的方式布線,利用差分對共模的抑制能力。另一個考量因素是多重來源採購。XO採用工業標準封裝和接腳排列,而時脈元件通常是單一供應商。如果需要考慮多來源採購,則建議使用XO基礎的解決方案。

高性能時脈元件可透過提供整數和分數時脈合成的任意組合來簡化XO替換。一個重要的設計考慮因素是仔細檢查每個元件的分數時脈抖動性能。一些解決方案遭受有易變的分數時脈抖動,時脈元件可能無法在性能敏感的應用中提供足夠的抖動設計餘量的風險。要求時脈供應商為性能關鍵的時脈提供抖動量測,以確保元件滿足應用需求始終是一個安全的選擇。應配置所有輸出時脈,以便抖動量測考量輸出時脈之間的串音干擾。

另一個關鍵的設計考慮因素是展頻時脈,這是一種用於減少運算和工業應用中電磁干擾(EMI)的常用技術。如果一個應用需要混合展頻和非展頻時脈,則必須仔細檢查每個時脈資料手冊,確保元件可以同時產生展頻時脈和方波時脈。

在某些應用中整合時脈元件提供了其他有意義的優點。例如,可以在某些時脈元件上更改每個輸出時脈的頻率,簡化設計驗證期間的頻率餘裕測試。在某些時脈元件上可以類似的改變每個輸出時脈的相位,輕鬆排列時脈輸出邊緣,並補償時脈訊號之間因PCB布線長度不同而造成的不匹配。雖然並不總是需要這些功能,但這可以讓開發者高枕無憂,因為這些功能能在需要優化設計時提供支援。

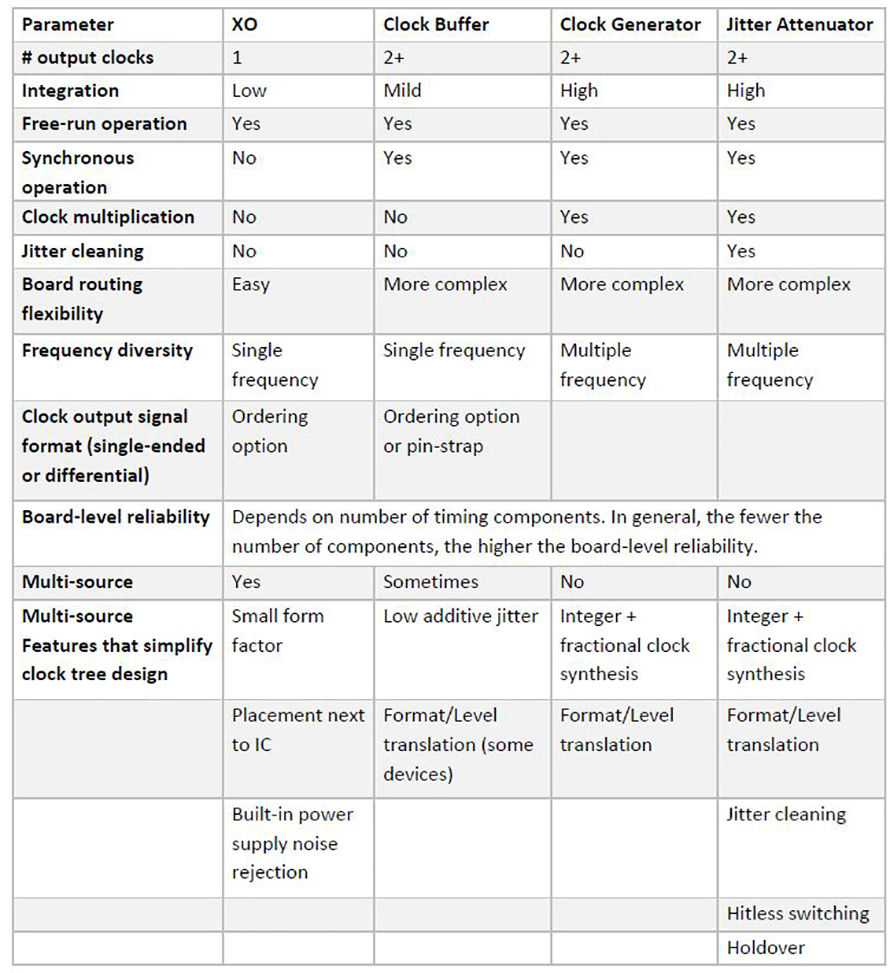

表1總結了在做時脈決策時,應該考慮的選擇標準。依照表中列出的指導原則,可以更輕鬆為即將到來的設計,選擇適合的時脈或振盪器。而因應多元的應用需求,Silicon Labs提供各種抖動衰減時脈、時脈產生器、時脈緩衝器、XO和VCXO。

表1 選用時脈方案時應考慮的條件與標準

表1 選用時脈方案時應考慮的條件與標準

(本文由Silicon Labs提供)