5G毫米波技術擁有比4G更大的頻寬,提供更高的傳輸速率與容量,但卻有著傳輸容易衰減的挑戰,故須透過相位陣列的方式予以解決,而實現相位陣列技術,相控整合晶片扮演重要角色。

隨著高數據傳輸應用的爆炸性成長,為了應付越來越多的數據吞吐量和無線網路應用需求,第五代行動通訊(5G)應運而生。5G頻譜主要分為sub-6GHz和毫米波頻段,其中毫米波頻段最大的優點是具有比sub-6GHz數倍的頻寬,但需克服毫米波訊號在空氣中傳遞損耗大的問題,而相位陣列是目前最被接受的解決方案,它是藉由將多路訊號聚焦於空間中一特定方位,形成指向性的波束來增加訊號傳遞的距離。在此相位陣列前端系統中,最為關鍵之零組件即是相控電路。

雙極化毫米波相位陣列

相位陣列在毫米波通訊上之使用,主因為克服毫米波於空間中傳播高損耗之問題。多路多天線同頻同時發射相同訊號,藉由在不同路之相同訊號加上權重(Weighting),在空間中之特定方位同相(In-phase)相加,產生建設性干涉,使能量形成指向性波束,增加傳輸端的等效全向輻射功率(Equivalent Isotropically Radiated Power, EIRP)與接收端的訊雜比(Signal to Noise Ratio, SNR),進而延長訊號傳遞的距離。

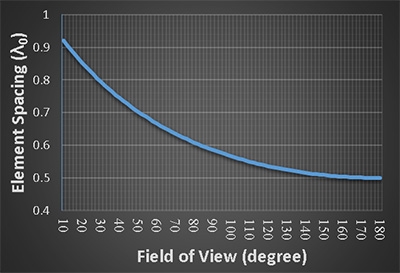

考量架構的複雜程度與成本,目前應用於毫米波之相位陣列,在射頻調整相位與振幅權重為大宗,即為射頻波束成形(Radio Frequency Beamforming)[1]。透過射頻前端類比電路的實現,可進行相位與振幅權重之調整,產生波束成形之效果。若要執行彈性較高的波束成形,每一陣列之天線單元須包含功率放大器、低雜訊放大器、收發切換開關、相移器與衰減器/可變增益放大器等類比控制電路,且天線單元之間間距需小於特定操作頻率之波長。而天線單元之決定,取決於系統欲掃描之視角,如圖1所示。為避免相位陣列進行波束掃描時,在非主波束方位產生不必要之光柵旁波瓣(Grating Lobe),造成波束能量不集中與干擾等問題,一般天線單元之間的間距會限制小於或等於半波長。

圖1 相位陣列掃描視角與天線單元間距之關係圖

圖1 相位陣列掃描視角與天線單元間距之關係圖

由上述可想而知,在毫米波波長小與每一天線單元包含多電路之情況下,整合會是一大難題。此時,相控電路採用積體電路設計整合較為最佳解決方案,藉由整合多路前端相控電路,支援數個天線單元,同時整合相關數位電路,由於部分數位電路與周邊電路皆可共用,簡化數位控制介面,亦可減少所需晶片面積。

另外,毫米波與sub-6GHz最大的不同在於損耗增加,這也使得原在sub-6GHz高秩(High Rank)的情況,在毫米波不易存在。在sub-6GHz可輕易達到4×4多重輸入多重輸出(Multi-input Multi-output, MIMO),甚至8×8 MIMO,於毫米波中將不易做到。因此,在毫米波低秩的情形下,要增加通道容量,使用極化分集(Polarization Dversity)方式,透過雙極化天線同時收或送兩正交的訊號(正交訊號其相關度低),可達到2×2 MIMO單一用戶端趨近2倍數吞吐量。射頻前端系統整合為節省面積,天線單元採用雙極化之設計,同一陣列天線可同時支援兩極化之輸入與輸出[2]。

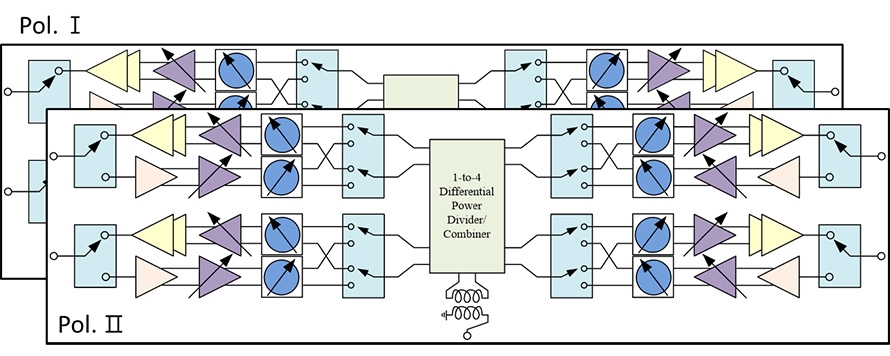

在相控電路中為創造兩獨立之路徑來支援極化分集之運作,射頻前端類比電路則須複製兩套,如圖2所示。可想而知,在有限的面積下,電路增加一倍,其在整合上勢必面臨困難,再加上需兼顧兩路徑之獨立性或隔離度,且散熱問題也隨著功率放大器的倍增而增加。綜合上述,簡單歸納幾個重點:

圖2 雙極化前端相控電路方塊圖

圖2 雙極化前端相控電路方塊圖

1. �米波無線傳輸衰減大,射頻前端須採用相位陣列,以增加傳輸/通訊距離。

2. �毫米波波長短、天線單元間距小,空間有限情況下相控電路將以整合積體晶片為主。

3. �毫米波低秩環境下,將採用極化分集方式實現2×2MIMO。 4. �為節省印刷電路板繞線面積與減少線路損耗,相控晶片整合兩組獨立前端電路,以支應雙極化前端設計。

5. �在有限面積下,相控晶片之整合與散熱問題,隨著電路元件倍增而加劇。

相控整合晶片設計

在[1]已簡述相控晶片各元件之關鍵指標,以下將介紹各元件在文獻上之實現方法。

・功率放大器(Power Amplifier, PA)

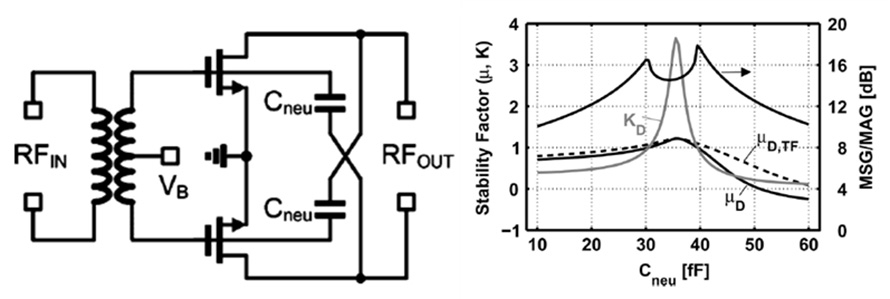

在PA的電路設計上,差動對(Differential)為一常見之電路架構,其好處是訊號之能量較能集中在差動線上,因此對於雜訊的抗干擾能力較好。而在毫米波段,電晶體本身的寄生效應會對特性具有較為嚴重的影響,尤其是閘極到汲極之電容(Cgd)會使得增益及穩定性下降許多。因此,常見的做法為增加一補償電容(Neutralization Capacitor)來將Cgd抵銷,如圖3[3]所示,藉此提高增益與穩定性。

圖3 Differential Type放大器及補償電容效應

圖3 Differential Type放大器及補償電容效應

而為了有效提升效率,一兩級功率放大器偏壓點分別操作在Deep Class-AB與High Class-AB被提出[4]。其中,Deep Class-AB可以提供AM-AM之預失真使P1dB及PAE的性能提升,然而其卻會導致AM-PM之特性較差,在輸入端加上一並聯之PMOS電容可補償AM-PM之失真。另外,也可採用偏壓控制網路(Adaptive Bias Network)來提升PA之效率[5],透過該偏壓網路使輸出電壓在小訊號與大訊號操作時有所不同,進而使整體放大器的效率提升。

・�低雜訊放大器(Low Noise Amplifier, LNA)

LNA扮演接收端第一級放大之角色,其雜訊指數(Noise Figure)與增益將支配整體接收機的靈敏度,因此設計良好的前級可以有效抑制雜訊並提升訊雜比。

如前段所述,在晶片內部以差動形式布局有利於抑止雜訊,然而為了簡化印刷電路板上之線路布局,在晶片輸入/輸出之引腳與天線端(一般於印刷電路板上)皆採用單端單端(Single-Ended)。因此,目前應用於差動毫米波系統的LNA做法主要分為兩種,一種是設計成單端(Single-Ended)輸入,差動(Differential)輸出的架構,第二種則是輸入輸出都為差動,最後在輸入端加入巴倫(Balun)的架構。

使用單端輸入、差動輸出的架構,其電路第一級通常為共源極(Common-source, CS)放大器,第二級為主動巴倫所構成[6],此架構的好處在於CS放大器可以有效的抑制雜訊。輸入輸出都為差動的架構,其電路第一級為共閘極(Common-gate, CG)放大器,後方兩級為疊接(Cascode)電路串接而成[7],此架構在抑制NF的能力雖然沒有CS放大器來的優異,輸入阻抗匹配、消耗功率、線性度卻比CS優秀,因此也較容易匹配,但使用此架構需額外再加上巴倫,因此NF會再加上巴倫的損耗。

・�可變增益放大器(Variable Gain Amplifier, VGA)

可調式增益放大器常見分為類比電壓控制及數位控制。常見類比電壓控制的可調式增益放大器架構為電流導引[8]以及偏壓控制[9],藉此控制偏壓的調控,造成電晶體的電流變化進而影響電路的增益變化以及增益的調整。

而數位控制的可調式增益放大器則是利用多組電晶體的偏壓(0及Vdd)切換,來影響電流變化實現增益控制[8]。另外,採用共柵極(Common-Gate)電晶體長寬比率(Aspect Ratio)[10, 11],亦可藉由切換不同電晶體之間的偏壓狀態來達到不同電晶體長寬比率的變化,將改變電晶體直流(DC)操作點,形成不同的阻抗增益,進而做到輸出不同增益變化的目的。

・相移器(Phase Shifter)

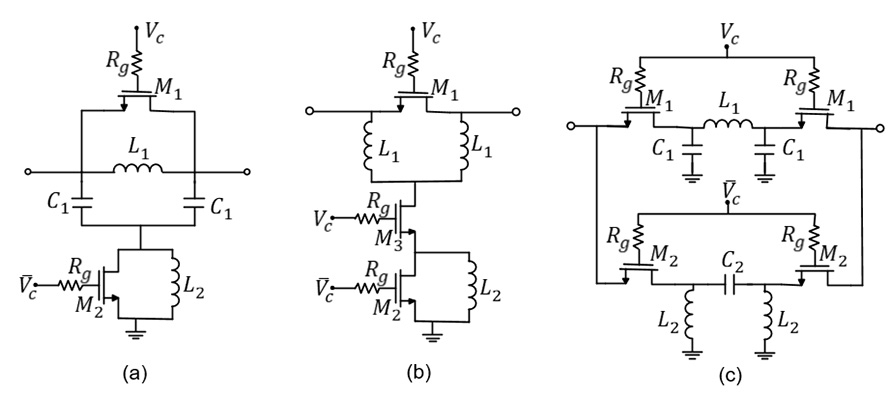

目前相移器大致上分為三類,分別為向量和相移器、反射式相移器和切換式相移器。向量和相移器是透過不同大小的I/Q訊號相加實現相移功能[12]。反射式相移器包含一90o耦合器和對稱的可調反射負載,透過調整反射負載進而影響訊號的相位變化[13]。第三類為切換式相移器,由多個不同相移單元串接而成,相位解析度由相移單位數量所決定,藉由切換訊號經過的路徑來改變相位。在路徑上有不同的相移電路,常見的相移電路是由電容電感組成的T型High Pass和Low Pass以及π型High Pass和Low Pass四種結構,衍生出的切換式相移器有多種,在此舉些例子。圖4為三種不同的切換式相移器,分別採用π型Low Pass結構、T型Low Pass結構以及同時採用π型High Pass和Low Pass的結構來達成[14,15]。由於切換式相移器有無功耗、無方向性的限制和控制簡單的優點,所以目前選用切換式架構作為相位陣列系統中的相移器。

圖4 三種切換式相移器電路架構圖

圖4 三種切換式相移器電路架構圖

掌握5G潛力股 毫米波相控晶片受倚重

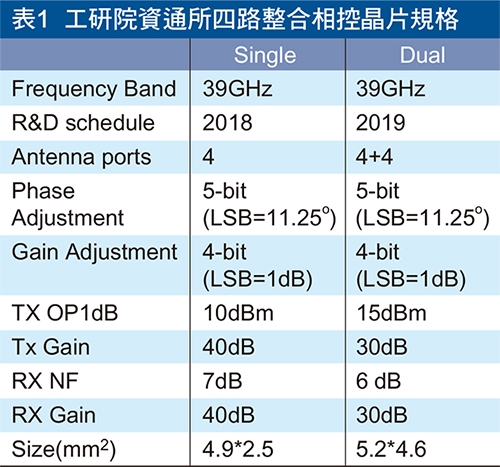

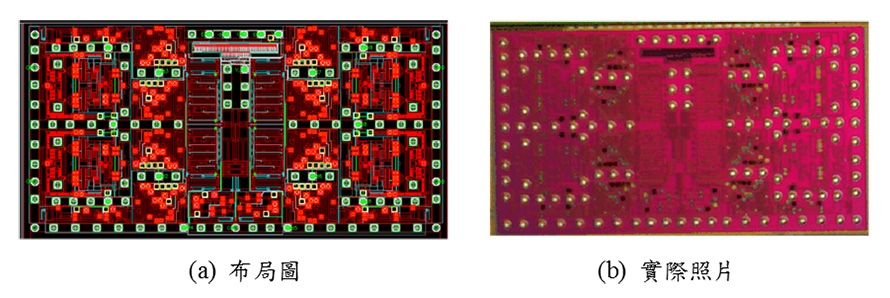

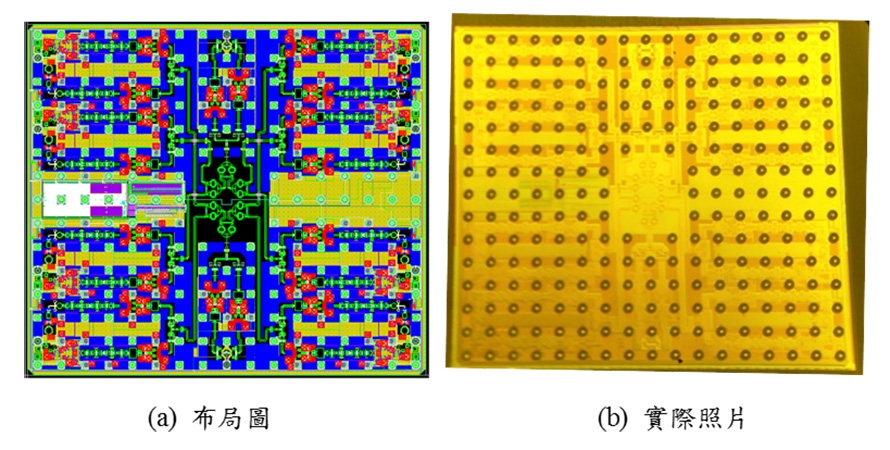

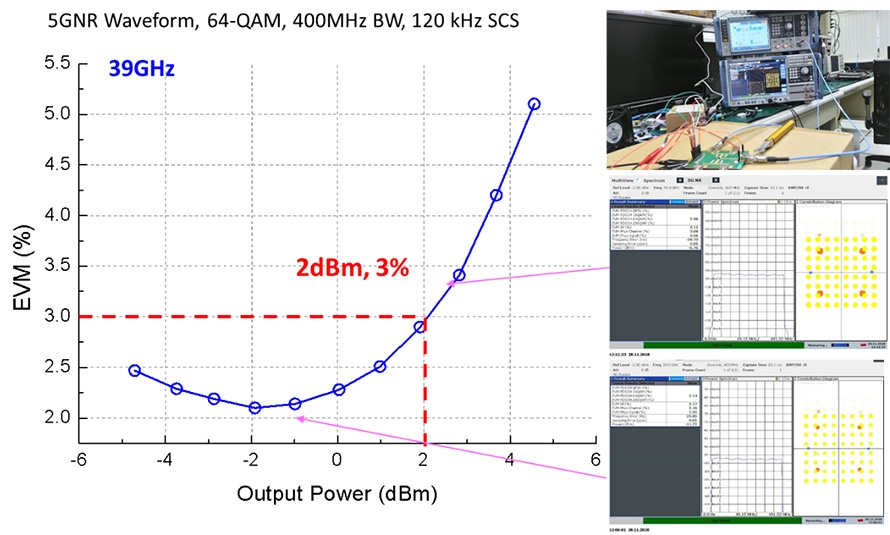

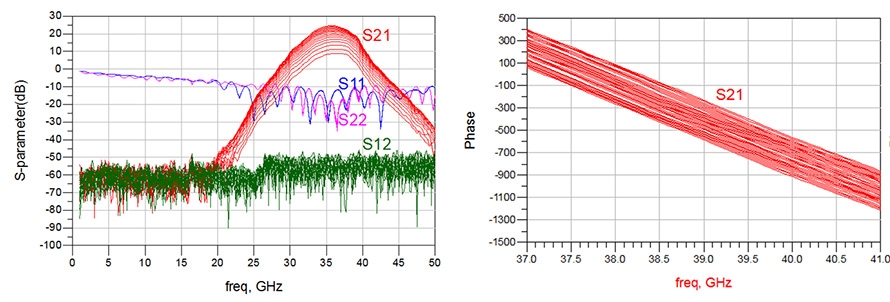

工研院資通所團隊於2017年初投入毫米波相控整合晶片開發,初期以GaAs製程之電路設計為主,已累積相關設計技術與成果。然而過程中發現GaAs在整合與散熱面臨很大的問題,在成本與可靠度尚無法滿足5G小基站之需求,於是在2017年底轉往CMOS發展。圖5與圖6分別為2018年與2019年的四路整合相控晶片開發成果,皆採用TSMC 65nm CMOS製程,前者為支援單極化設計,後者為雙極化,表1為其基本規格。以R&S的向量訊號產生器與訊號分析儀,產生的5G調變訊號測試單路單極化之輸出,線性輸出功率可達+2dBm,如圖7。在S參數量測結果顯示,雙極化相控晶片具有完整之相位與振幅控制功能,如圖8。工研院團隊除了致力於晶片開發上,更在毫米波模組上有多年的實績[2],圖9為上述相控晶片應用於相位陣列天線模組之實例,包含(a)電路板正面8×4天線陣列與(b)背面之相控晶片與數位、電源介面。

圖5 工研院開發之支援單極化四路整合相控晶片(晶片面積:4.9×2.5 mm2)

圖5 工研院開發之支援單極化四路整合相控晶片(晶片面積:4.9×2.5 mm2)

圖6 工研院開發之支援雙極化四路整合相控晶片(晶片面積:5.2×4.6 mm2)

圖6 工研院開發之支援雙極化四路整合相控晶片(晶片面積:5.2×4.6 mm2)

圖7 以5G調變訊號測試單路單極化整合相控晶片

圖7 以5G調變訊號測試單路單極化整合相控晶片

圖8 雙極化整合相控晶片之單路振幅與相位調控量測結果

圖8 雙極化整合相控晶片之單路振幅與相位調控量測結果

圖9 工研院開發之相控晶片暨雙極化相位陣列天線模組

圖9 工研院開發之相控晶片暨雙極化相位陣列天線模組

總結來說,為達成使用毫米波頻段進行通訊,相位陣列係目前較佳之解決方案,其中相控電路為關鍵不可或缺之零組件。前端相控電路需緊密與天線單元結合,並搭配整體系統,針對整合、功耗與散熱等問題做電路架構之優化。工研院資通所團隊已經成功開發毫米波39GHz相控晶片,可支援雙極化陣列設計,具備波束成形與波束掃描技術,未來將持續進行晶片面積與效率之最佳化,希冀能克服目前毫米波通訊成本與功耗/散熱之問題。

(本文作者皆任職於工研院資通所;該文也於工研院資通所《電腦與通訊》期刊刊登)