複數混頻器(Mixer)、零中頻(Zero IF)架構和高級演算法開發之間存在一種有趣的聯繫。本文旨在釐清以上三者各自的基本概念,包括工作原理以及它們為系統設計帶來的價值,並闡述彼此之間的相互依賴關係。

射頻(RF)工程常被視為電子領域的黑魔法。它可能是數學和力學的某種奇特組合,有時甚至僅僅是嘗試錯誤法(Try and Error)。它讓許多優秀的工程師不得其解,有些工程師僅瞭解結果而對細節毫無所知。現有的許多文獻往往不建立基本概念,而是直接跳躍到理論和數學解釋。

複數射頻混頻器揭秘

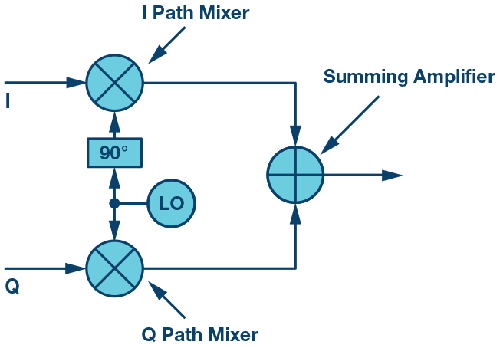

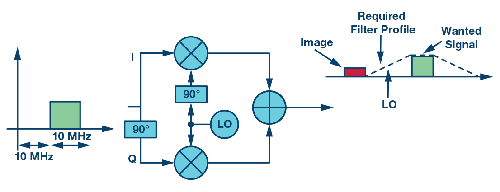

圖1是採用升頻轉換器(發射器)配置的複數混頻器原理圖。兩條並行路徑各有獨立混頻器,一個公共本地振盪器(本振)向這些路徑饋送訊號,本振與其中一個混頻器的相位相差90度。兩個獨立輸出隨後在求和放大器中求和,產生所需的RF輸出。

|

| 圖1 複數發射器基本架構 |

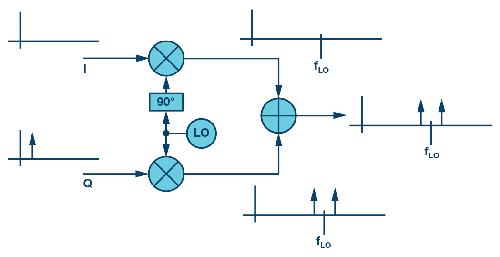

該配置有一些簡單但非常有用的應用。假設僅在I輸入上饋送一個訊號音,而不驅動Q輸入(圖2)。假定I輸入上的訊號音訊率為x MHz,則I路徑中的混頻器產生LO頻率±x的輸出。由於沒有訊號施加於Q輸入,此路徑中的混頻器產生的頻譜為空,I混頻器的輸出直接成為RF輸出。

|

| 圖2 I路徑分析 |

或者,假設僅向Q輸入施加一個頻率為x的訊號音。Q混頻器進而產生訊號音為LO頻率±x的輸出。由於沒有訊號施加於I輸入,其混頻器輸出靜音,Q混頻器的輸出直接成為RF輸出。

|

| 圖3 Q路徑分析 |

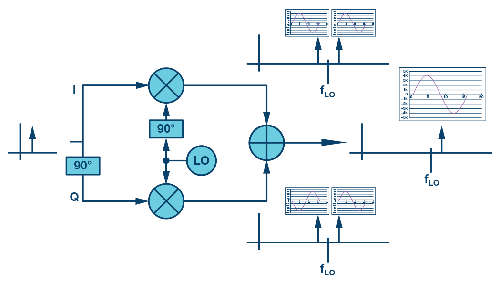

乍看起來,圖2和圖3的輸出似乎完全相同。但實際上,兩者有一個關鍵差異,那就是相位。假設將相同訊號音同時施加於I和Q輸入,並且輸入通道之間存在90度相移(圖4)。

|

| 圖4 同時施加I和Q訊號的路徑分析 |

仔細審視混頻器輸出,可觀察到:LO頻率加輸入頻率的訊號是同相的,但LO頻率減輸入頻率的訊號是異相的。這導致LO上側的訊號音相加,而下側的訊號音相消。沒有任何濾波,所以便消除了其中一個訊號音(或旁帶),產生的輸出完全位於LO頻率的一側。

在圖4所示例子中,I訊號比Q訊號超前90度。如果變更配置使得Q訊號比I訊號超前90度,那麼可以預期會有類似的相加和相消,但在這種情況下,所有訊號將出現在LO的下側。

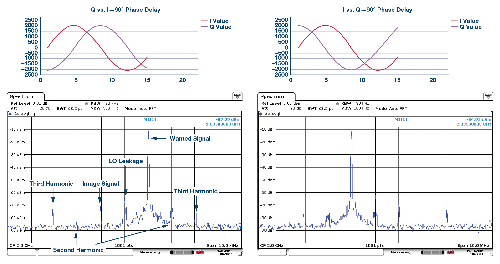

圖5顯示了一個複數發射器的實驗室測量結果。左邊顯示的是I比Q超前90度的測試案例,其導致輸出訊號音位於LO的上側。圖5右邊顯示了相反的關係,即Q比I超前90度,由此得到的輸出訊號音位於LO下側。

|

| 圖5 訊號音位置取決於I和Q的相位關係 |

理論上,應當可以讓全部能量僅落在LO的一側。然而,如圖5中的實驗室測量結果所示,在實踐中完全相消是不可能發生的,有一些能量會留在LO的另一側,這就是所謂鏡像。還應注意,LO頻率的能量也是存在的,稱為LO洩漏(LOL)。結果中還可以看到其他能量,這些是所需訊號的諧波,這裡不予討論。

為了完全消除鏡像,I和Q混頻器輸出的幅度必須完全一致,而在LO鏡像側上彼此之間的相位恰好相差180度。如果不能滿足上述相位和幅度要求,那麼圖4所示的相加/相消過程就會不太理想,鏡像頻率的能量仍會存在。

濾除不良鏡像但不影響訊號

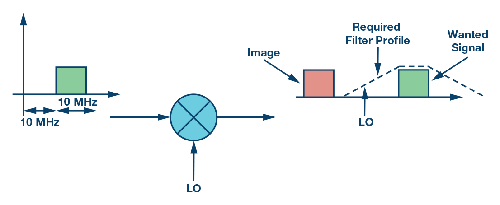

採用常規單混頻器架構時,會產生LO±產物。發射之前須要消除其中一個旁帶(Sideband),通常是透過增加帶通濾波器來消除。濾波器的滾降頻率必須適當,使其既能消除不需要的鏡像訊號,又不會影響需要的訊號。

鏡像和所需訊號之間的間隔會直接影響到對濾波器的要求。如果間隔較大,可使用滾降較緩的簡單低成本濾波器。如果間隔較窄,設計必須實現具有陡峭回應的濾波器,通常採用多極點或表面聲波(SAW)濾波器。因此可以說,鏡像和所需訊號之間必須保持適當的間隔,以便可以濾除鏡像而不影響所需訊號;該間隔與濾波器的複雜度和成本成反比。此外,如果LO頻率可變,濾波器必須可調諧,這會進一步增加濾波器的複雜度。

鏡像和所需訊號之間的間隔,由施加於混頻器的訊號決定。圖6例子顯示一個與DC相距10MHz的10MHz頻寬訊號。相應的混頻器輸出將鏡像置於與所需訊號相距20MHz的地方。在這種配置中,為在輸出端實現10MHz的所需訊號頻譜,必須讓一條20MHz基頻訊號路徑連接到混頻器。10MHz的基頻頻寬未使用,混頻器電路的資料介面速率高於必要水準。

|

| 圖6 單混頻器鏡像濾波器要求 |

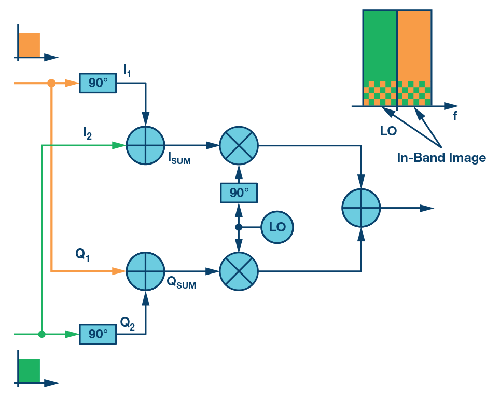

回到圖5所示的複數混頻器,可知其架構消除了鏡像而無需外部濾波。而且,在零中頻架構內可以優化效率,使得訊號路徑處理頻寬等於所需訊號頻寬。圖7所示的概念圖說明其實現原理。如上所述,如果I比Q超前90度,則僅LO上側會有輸出。如果Q比I超前90度,則僅LO下側會有輸出。因此,如果產生兩個獨立基頻訊號,其中一個設計成僅產生上旁帶輸出,另一個設計成僅產生下旁帶輸出,那麼這樣一來便可以在基頻中將其相加並施加於複數發射器。結果將是具有不同訊號的輸出出現在LO上側和下側。在實際應用中,組合基頻訊號以數位方式產生。圖7所示求和節點僅是為了說明此概念。

|

| 圖7 零中頻複數混頻器架構 |

利用複數發射器產生單旁帶輸出具有相當大的好處,可減少為消除鏡像所需要的RF濾波。然而,如果鏡像相消性能足夠好,使得鏡像可忽略不計,那麼可以使用零中頻模式來進一步發揮該架構的優勢。

零中頻模式特性 強化複數發射器優勢

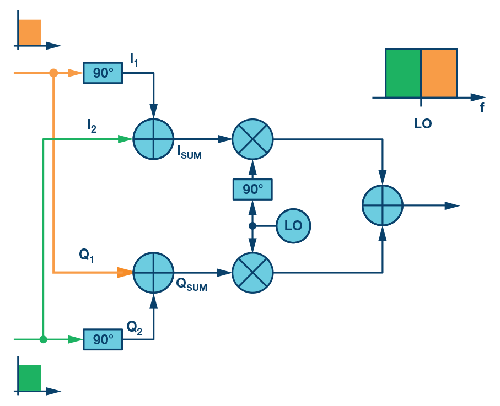

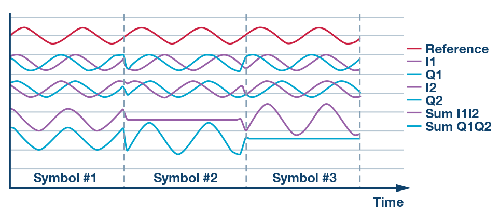

零中頻允許使用特別創建的基頻資料來產生RF輸出,從而在LO兩側出現相互獨立的訊號。圖8有兩組相互獨立的I和Q資料,用符號資料編碼,接收器可以根據基準載波的相位進行解碼。

|

| 圖8 深入考察零中頻複數混頻器配置中的I/Q訊號 |

初始觀測顯示:Q1比I1超前90度,兩者的幅度一致。類似地,I2比Q2超前90度,其幅度同樣一致。將這些獨立訊號合併,使得I1+I2=SumI1I2,Q1+Q2=SumQ1Q2。相加後的I和Q訊號不再表現出相位和幅度相關性,其幅度在所有時候都不相等,兩者之間的相位關係不斷變化。所得的混頻器輸出將I1/Q1資料置於載波的一側,將I2/Q2數據置於載波的另一側,如上所述及圖7所示。

透過將彼此相鄰的獨立資料塊置於LO的任一側,零中頻使複數發射器的優勢得到加強。資料處理路徑頻寬絕不會超過資料頻寬。因此,理論上在零中頻架構中使用複數混頻器便提供一種解決方案,其不需要RF濾波,同時還能優化基頻功率效率,降低不可使用訊號頻寬的單位成本。

到目前為止,本文的重點是複數混頻器用作零中頻發射器。同樣的原理反過來也成立,即複數混頻器架構可以當作零中頻接收器。針對發射器說明的優勢同樣適用於接收器。使用單混頻器接收訊號時,首先必須利用RF混頻器濾除鏡像頻率。在零中頻工作模式下,毋須擔心鏡像頻率,高於LO的訊號接收與低於LO的訊號接收是相互獨立的。

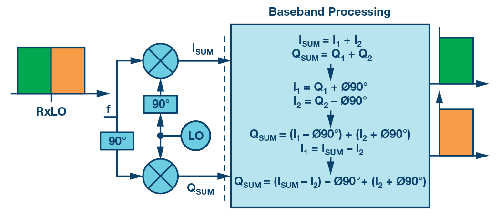

複數接收器如圖9所示。輸入頻譜同時施加於I和Q混頻器。一個混頻器通過LO驅動,另一個混頻器通過LO+90度驅動。接收器的輸出為I和Q。對於接收器來說,要想由經驗證明給定輸入對應的輸出將會如何並不容易,但如果輸入訊號音高於LO,如圖所示,那麼I和Q輸出將處於(訊號音–LO)頻率,並且I和Q之間會有相移(I比Q超前)。類似地,如果輸入訊號音低於LO,那麼I和Q輸出同樣是在(LO–訊號音)頻率,但這時是Q比I超前。透過這種方式,複數接收器可以區分高於LO的能量和低於LO的能量。

|

| 圖9 零中頻複數混頻器接收器配置 |

複數接收器的輸出將是兩種I/Q資訊之和,一種代表接收到的高於LO的頻譜,另一種代表接收到的低於LO的頻譜。此一概念已在前面針對複數發射器做過說明,其中是將相加後的I訊號和相加後的Q訊號施加於複數發射器。對於複數接收器,接收相加後的I資訊和相加後的Q訊息的基頻處理器可利用複數快速傅立葉轉換(FFT)來輕鬆區分較高頻率和較低頻率。

收到相加後的I訊號和相加後的Q訊號時,有兩個已知量(相加後的I訊號和相加後的Q訊號),但有四個未知量,即I1、Q1、I2和Q2。由於未知量多於已知量,因此似乎無法解出I1、Q1、I2和Q2。然而,還知道I1=Q1+90,I2=Q2–90,有了這兩個已知關係後,便可利用收到的相加後的I訊號和相加後的Q訊號解出I1、Q11、I2和Q2。事實上,只須解出I1和I2,因為Q訊號是I訊號的副本,不過相位偏移±90度而已。

實踐中,複數混頻器試圖完全消除鏡像訊號,此一限制對無線電架構設計有兩個重大的影響。

零中頻與複數混頻 催生最優設計方案

即使有性能限制,複中頻仍能帶來切實的好處。試著考慮圖10所示的低中頻例子。由於性能限制,確實能看到鏡像。然而,同對單混頻器設計的預期相比(圖6),該鏡像已大為衰減。雖然複數混頻器仍需要濾波器,但對該濾波器的要求可以放鬆很多,其實現也較簡單,成本較低。

|

| 圖10 複數混頻器的實際實現注意衰減的鏡像 |

濾波器複雜度與鏡像和所需訊號之間的距離成反比。如果使用零中頻配置,該距離將變為0,鏡像位於所需訊號頻段中。零中頻理論的實際應用無法完全實現,產生的帶內鏡像導致性能降低到不可接受的水準(圖11)。

|

| 圖11 零中頻實現的限制 |

只有滿足I和Q資料路徑的相位和幅度要求,複數發射器和接收器的原理才成立。訊號路徑的不匹配,會導致LO兩側的鏡像訊號不能精確相消。此類問題的例子參見圖10和圖11。在不使用零中頻的情況下,可以採用濾波來消除鏡像。

然而,若使用零中頻架構,不需要的鏡像會直接落在所需訊號的頻譜範圍內,如果鏡像功率足夠大,就會發生故障狀況。因此,只有設計能消除訊號路徑上的相位和幅度不一致時,使用零中頻和複數混頻才能提供最優系統設計方案。

高級演算法提供必要支援

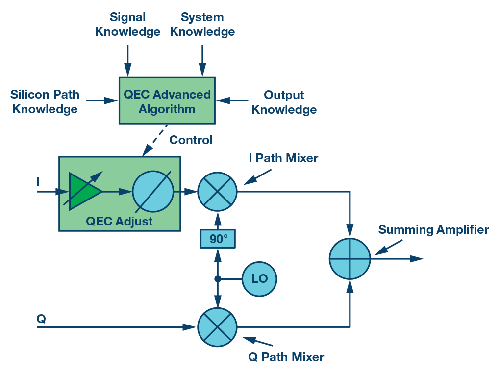

複數混頻器架構的概念已存在很多年,但在動態無線電環境中滿足相位和幅度要求的挑戰限制了其在零中頻模式下的使用。亞德諾(ADI)綜合運用智慧晶片設計和高級演算法,克服了這些挑戰。設計允許存在影響訊號路徑的因素,但智慧矽片設計將這些影響降至最低。剩下的誤差通過自優化正交糾錯(QEC)演算法消除(圖12)。

|

| 圖12 高級QEC演算法和智慧晶片設計支援零中頻架構 |

在AD9371等收發器上,QEC演算法內建於安謀國際(ARM)處理器中。它持續掌握晶片訊號路徑、經調變的RF輸出、輸入訊號和外部系統環境的資訊,並利用此資訊以受控的預測方式智慧適應訊號路徑輪廓,而不是做出本能式被動反應。該演算法性能出色,可將其視為以數位方式輔助類比訊號路徑發揮最佳性能。

在這些收發器內部有多種高級演算法駐留並發揮作用,動態QEC校準演算法只是其中一個較突出的例子。其他與之共存的演算法還有LO洩漏消除等,這些演算法將零中頻架構的性能提升到最優水準。此類第一代收發器演算法主要用於支援實現相關技術,而第二代演算法如數位預失真(DPD)不僅能增強收發器的性能,還能提升整個系統的性能。

所有系統都有一些不足之處會限制其性能。第一代演算法主要聚焦於透過校準消除晶片內限制,而新一代演算法則利用智慧手段來消除收發器外部的系統性能和效率限制因素,例如功率放大器(PA)失真和效率(DPD和CFR)、雙工器性能(TxNc)、被動交互調變(PIM)問題等。

高級演算法加持 無線電設計更靈活

複數混頻器已存在很多年,但其鏡像抑制性能不允許將其用於零中頻模式。但智慧晶片設計和高級演算法的結合,消除了原先阻止高性能系統採用零中頻架構的性能障礙。性能限制消除之後,採用零中頻架構對降低濾波、功耗、系統複雜度、尺寸、熱量和重量都有好處。

對於複數混頻器和零中頻,可以考慮將QEC和LOL演算法用作支援功能。但是,隨著演算法開發範圍的擴展,它給系統設計人員帶來更高的性能水準,使他們能更靈活地設計無線電。

(本文作者為亞德諾收發器產品部門的應用經理及利默里克通信系統工程團隊的演算法開發經理)