電動化及自動駕駛正改變汽車領域的需求。即使是引擎、變速箱及車輪速度感測器等標準應用,都有很大的創新空間。OEM和第一級製造商希望在現場試驗新的演算法、架構及感測器技術,因此要求提供硬體原型。硬體原型一般可在幾個月內開發完成,並以動態變更要求的方式判定特性,找出最適合搭配應用的狀態。

汽車業要求感測器原型在設計初期時,測試新演算法及應用可能性。因此目前市場上已有業者,如英飛凌(Infineon)開發全新方法,可順利由概念轉移至實作階段。這種方法能在非常短的時間內,向客戶提供可運作的原型,快速因應客戶要求。此外,這種方法還可以在取得測試晶片或最終矽晶片之前,提升設計的信心水準,對概念、設計及驗證工程師而言是一大利多。

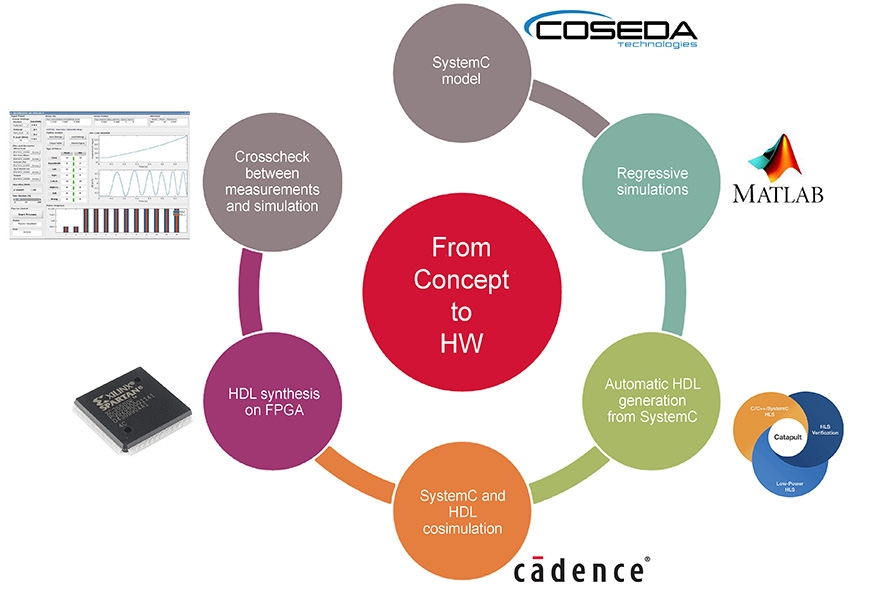

本文將以SystemC作為案例分析,在SystemC概念及可行性研究期間開發的產品模型,可自動轉譯至HDL,並準備好合成至FPGA,以便由客戶建立原型。產生的HDL首先會與SystemC共同模擬進行自動驗證,然後FPGA原型會在實驗室系統測試台進行測試,最後測量結果將再次自動與模擬結果比對。這是高度自動化的流程,可減少開發原型時的時間及工作量,不會犧牲效能及可靠性。

一開始模型會透過模擬廣泛驗證,以高階合成(HLS)工具產生硬體描述語言(HDL),然後與作為理想參考(Golden Reference)的SystemC模型共同模擬。模擬顯示通過時,程式碼會合成至真實的現場可程式閘陣列(FPGA)硬體,並於實驗室及現場進行測試。

這裡的目標是開發完整方法,以快速、彈性及精簡的方式由概念轉移至實作階段。產品模型於SystemC/SystemC AMS(通常於概念階段開發)提供後,就會自動轉譯至HDL,虛擬原型則成為真實原型,不但可提供給客戶,甚至能在應用之中測試。

方法流程(圖1)可簡單歸納為下列要點:概念、驗證概念、從概念到實作、驗證實作、從實作到真實硬體,以及驗證真實硬體。

圖1 新型設計方法可更快速由概念進展至原型

圖1 新型設計方法可更快速由概念進展至原型

感測器模型開發於SystemC之中完成。感測元件、類比路徑及數位核心於SystemC及SystemC AMS之中建模,然後會透過迴歸模擬驗證模型。上千次的模擬將反覆執行,涵蓋各種使用案例及真實輸入資訊。下一步就是自動將程式碼轉譯為HDL,準備在FPGA進行合成。寫入的VHDL或Verilog程式碼會儲存,並將數位核心自動由SystemC轉譯至HDL。

自動共同模擬HDL及SystemC完成後,就會重複使用寫入的測試設定以驗證模型。用於驗證SystemC的相同刺激產生器及評估器,也會用於模擬HDL。如果提供相同輸入,SystemC及HDL輸出應會相符。之後會在FPGA進行合成,然後自動比對測量與模擬結果。對特定使用案例而言,可以向硬體及模型提供相同的輸入刺激。如果提供相同輸入刺激,SystemC模型及真實硬體的輸出應會相符。

SystemC感測器模型開發

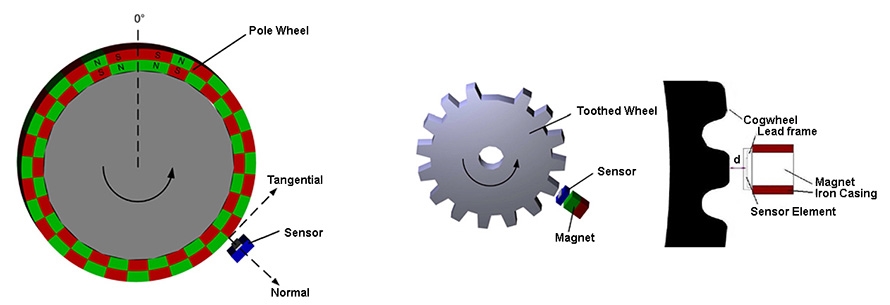

本文所述方法已應用於汽車變速箱應用之中的磁性速度感測器。磁性速度感測器會感應旋轉車輪的速度及旋轉方向,用於各種應用(車輪速度、變速箱、曲柄軸及凸輪軸),提供非接觸式且堅固耐用的低成本解決方案。磁性編碼器一般應用於車軸,由感測器感應旋轉時產生的磁場變異,或是使用回授偏壓磁鐵產生恆定磁場,由鋼輪旋轉調整。以上兩種選項於圖2顯示。

圖2 設計範例:磁性編碼器及工具輪搭配回授偏壓磁鐵

圖2 設計範例:磁性編碼器及工具輪搭配回授偏壓磁鐵

為了感測磁場,需要使用不同類型的感測元件。其中最常見的就是霍爾原則,或測量改變磁場的電阻器,例如巨磁阻(GMR)、穿隧磁阻(TMR)或異向性磁阻(AMR)。以SystemC為基礎的產品模型,普遍用於模擬積體電路行為,可靠地評估需求定義的明確度及完整度,探索不同的可能架構,並驗證各個區塊的硬體需求。 下一代變速箱感測器的SystemC模型已經開發完成,其中參考了內部方塊圖及產品需求。此外特別要說明的部份是SystemC AMS使用的類比模組,以及SystemC已經選擇的數位領域計畫。

為了正確說明感測器行為,需要詳細說明數位演算法,而SystemC能夠非常妥善地說明數位行為。此外,相較於Verilog或VHDL等硬體描述語言,模擬可更快速輕鬆執行,並可於Windows或Unix執行。最後,一旦完成編譯,就可以與客戶共用模型,以保護智慧財產。

迴歸模擬進行模型模擬與驗證

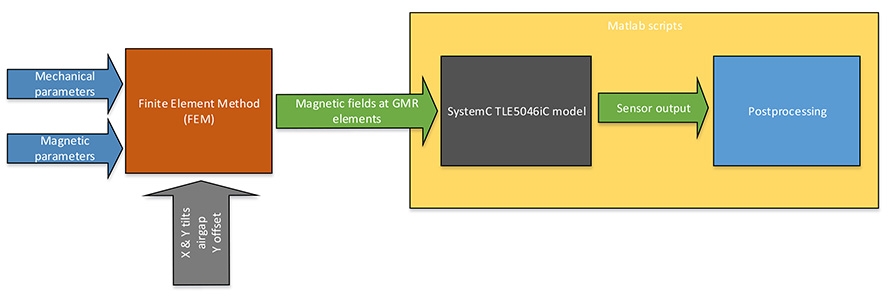

SystemC模型會以上千次的模擬,依據真實使用案例進行驗證。模擬流程於圖3說明。

圖3 簡化模擬流程

圖3 簡化模擬流程

有限元法(FEM)模擬用於取得磁場向量,作為SystemC模型的輸入。這項作業的流程已獲得改善,增加使用案例數量及自動化層級,特別是刺激產生及輸出評估目前於SystemC進行,可提升模擬速度。Matlab指令碼控制模型參數,並測試案例組態。

刺激產生器能夠產生下列使用案例,並以FEM模擬的磁場作為輸入:向前/向後旋轉、改變方向、突然改變氣隙、角度及氣隙振動、車輪偏心及雜散磁場影響。

自動將程式碼轉譯為HDL

數位核心的SystemC程式碼已經寫入,並將VHDL轉譯需求列入考量。就此觀點而言,SystemC中所有可能但無法合成的語言建構均已遭拒絕,此外也拒絕使用「雙精度」資料類型及複雜的C++結構。

Mentor Catapult軟體用於將數位核心的每個SystemC模組轉譯至VHDL。結果將產生一組VHDL模組,與SystemC模組具有相同階層。

總計約轉換了15個SystemC模組,每個模組的複雜度約為500行程式碼。數位設計人員專家可能要花好幾個月的時間,將SystemC模型行為轉換至HDL,以便在FPGA進行合成。使用Mentor Catapult之後,轉譯程序大約一天就可完成。高階合成方法可節省各種的人月工作負荷。這是原型建立活動的關鍵點,因為速度是其中的基本要素。

自動共同模擬HDL/SystemC

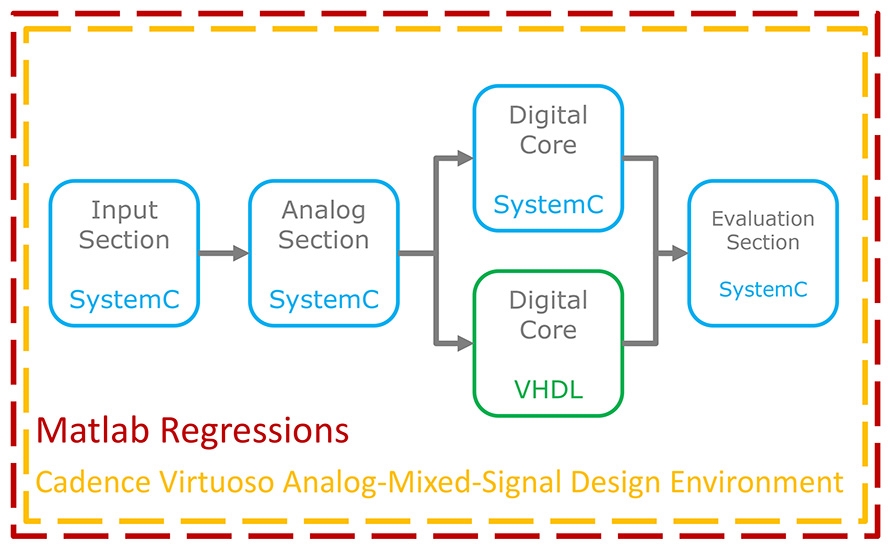

為了驗證轉譯結果,使用Cadence Virtuoso環境共同模擬數位核心的VHDL轉譯及SystemC模型。其中在Virtuoso建立圖示,將SystemC的「輸入區段」模組具現化。感測器的類比部分則是位在SystemC模組的「類比區段」,在其中饋入輸入區段的訊號。類比數位轉換器(ADC)SystemC模組也一樣比照辦理。類比區段及ADC的輸出會連接至SystemC數位核心模組及其VHDL轉譯。兩個數位核心實作的輸出(VHDL及SystemC)則連接至兩個類比介面SystemC模組。兩個「評估區段」SystemC模組則具現化,以評估兩個類比介面模組的輸出(圖4顯示簡化結構)。

圖4 共同模擬設定

圖4 共同模擬設定

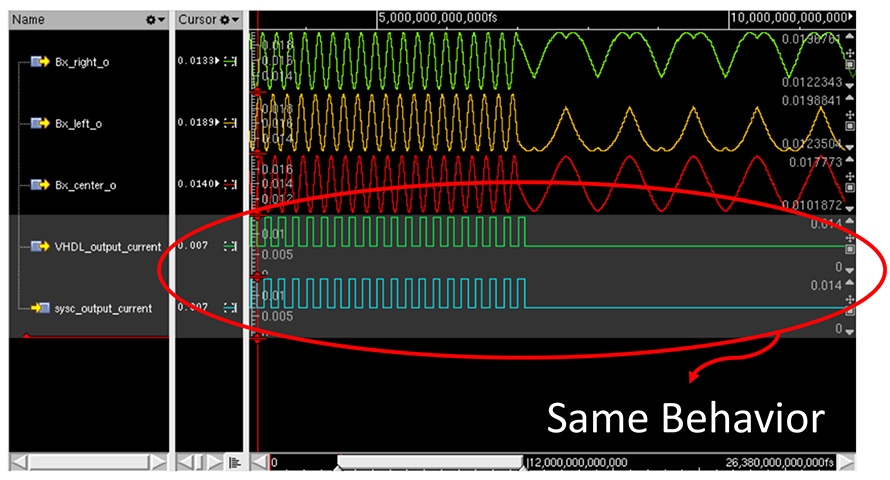

這項工作流程可共同模擬數位核心的SystemC及VHDL程式碼,方式為針對兩者使用相同的輸入及評估邏輯。共同模擬結果將分為兩份不同報告,一份為VHDL,另一份為SystemC,其中將描述兩個輸出訊號輸出脈衝的特性,以便進行比較。圖5顯示共同模擬範例。

圖5 共同模擬結果範例

圖5 共同模擬結果範例

結果顯示VHDL轉譯具有適當行為,與SystemC行為相符程度良好,其中只有因為工具執行高階合成的方法,造成部分少許的時間差異。如果使用Catapult工具,就可以完全相符。

在FPGA進行合成

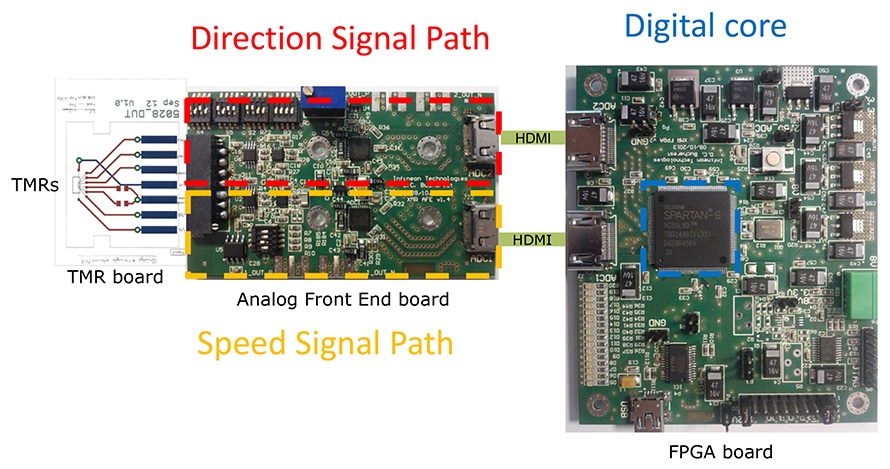

前一個步驟驗證HDL程式碼之後,就可以將設計移往真實硬體。目前在實驗室使用的硬體包含三個板:xMR板、類比前端(AFE)板及FPGA板(圖6)。

圖6 硬體原型:xMR、AFE及FPGA板

圖6 硬體原型:xMR、AFE及FPGA板

xMR板包含裸晶矽及一個以上的感測元件(GMR或TMR電阻器),黏合在小型PCB;PCB則連接至類比前端。AFE板對速度感測器的類比前端進行建模,其中有串級放大器及ADC。這個板可使用DIP交換器進行部分配置,而放大器增益及感測元件組態均可變更。最後,感測器數位核心會在FPGA板實作。其中使用Xilinx Spartan 6 FPGA,並提供部分輸入及輸出接腳,用於感測器設定及除錯。

未來將有部分其他選項可列入考量,例如以可編程前端取代AFE板,或系統單晶片(SoC)取代簡易的FPGA。

自動比對測量與模擬結果

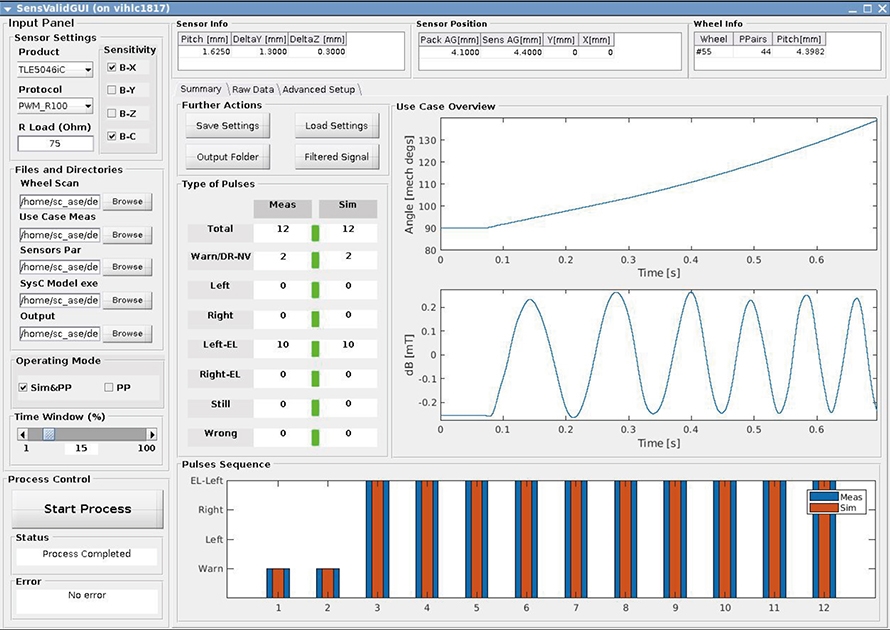

最後在新方法中,會依據理想參考(Golden Reference)的SystemC模型,自動執行硬體共同驗證。驗證方法以下列工作流程說明:測量系統輸出及刺激(輸出來自感測器,磁性刺激則由車輪動作產生)。進行模擬時,會向模型提供之前在真實測試台測量的刺激。演算法會對硬體及軟體資料執行後處理,以用於產生刺激和最終比較等用途。之後將收集經過後處理的資料,並依據預先定義的驗證標準進行評估,以交叉檢查硬體與模型的比較結果,找出最終需要修正的不符之處。圖7顯示共同驗證環境的圖形使用者介面(GUI)。

圖7 感測器驗證工具的GUI

圖7 感測器驗證工具的GUI

本文所述方法已經實施,目前用於所有下一代的變速箱感測器及部分其他產品。舉例來說,結合測量與模擬的方法,已證實能非常有效地支援新型車輪速度感測器的設計活動。 最終矽晶片之中合成的VHDL,能夠與參考SystemC模型共同模擬,以減少錯誤數量及驗證工作。原型(及最終矽晶片)可於實驗室測試台進行測試,測量結果則可與模擬結果比較。結論是虛擬及真實原型建立是非常實用且強大的工具,可透過模擬及實際測量驗證應用需求。

(本文作者皆任職於英飛凌)