隨著半導體製程技術能力不斷向上提升,半導體晶片的功能日益強大,以致半導體晶片訊號的傳輸量及晶片的接腳數亦隨之增加,過去以導線架(Lead-frame)的封裝形式已逐漸無法滿足市場需求,因而讓封測產業一路由低階的DIP(Dual In-Line Package)、SOP(Small Out-Line Package) 、TSOP等逐漸走向以IC載板的閘球陣列(BGA)、覆晶(Flip Chip, FBGA),乃至於晶圓尺寸封裝(CSP)等高階封裝形式,這全因為終端應用市場的需求,使得封裝技術必須不斷翻新。

封裝技術演進史,可以說每10年就會出現一次主流封裝技術更換,1970年代的主流技術為DIP,這種封裝技術是接腳插入技術為基礎,大多是應用於六十四支接腳以下的電子元件封裝。到了1980年代,主流封裝技術隨著終端市場的需求,改由雙邊接腳的DIP進化到周邊接腳且以表面黏著技術為基礎的QFP(Quad Flat Package)及LCC(Leaded/Leadless Chip Carrier);此外,還有CPU是以面陣列接腳型態的PGA及因應消費性電子商品所產生的SOP小型化封裝技術。

近10年來,隨著IBM高舉系統級封裝(SiP)大旗,與英特爾(Intel)對於系統單晶片(SoC)的宣告;加上台積電積極建置晶圓凸塊生產線與3D IC技術,到現在日月光、安可(Amkor)、矽品等國際半導體封裝大廠紛紛以SiP為主軸擘畫宏籌,開啟了IC設計公司與整合元件製造商(IDM)訴求SiP產品設計,一時間SiP躍升成為眾所競逐的熱門技術。

近年來半導體產業積極朝SoC與SiP方向發展,以求達到產品效能與便利性的提升,而SoC和SiP的孰優孰劣也成為長久以來各家的爭論的焦點;隨著電子工業竭力滿足小型化和複雜電子產品在成本和上市時間的要求,這個爭論變得日益貼近現實。在最近10年,出現了眾多的趨勢,對於電子產品的設計方式衝擊很大,因為產品不僅須在性能和設計要與眾不同,而且許多產品的壽命往往只有一年以下,使得電子產品的成本上升及上市時間縮短。

上述現象導致SoC的問世,然而使用SoC設計電子產品最大的問題就是成本,因為整個設計流程所需從設計工程、驗證、工具成本、光罩等來看,針對一個消費性電子產品的SoC設計很容易花費約1,000萬美元,假定該製造商將賣出一百個晶片,那麼在每個元件的非再生工程(NRE)成本將高達10美元。

若一個消費性電子產品在批發銷售時約只有幾美元的利潤,那麼非再生工程占整個材料成本比重將相當大;但如果該產品在設計後段發生一些差錯必須重新設計時,成本除了將進一步惡化,同時還要負擔上市時間的損失,這些問題都與SoC相關的長設計週期脫離不了關係。

從開發單一消費性電子產品來看,從撰寫硬體描述程式(HDL),到經過重重驗證(Verification)與光罩繪圖檔(GDSII),最後到晶圓廠投產過程,至少須經過8~12個月,也就是說開發先期產品從投入到回收資金將超過1年以上,而複雜的網路晶片甚至將拉長為18個月以上。

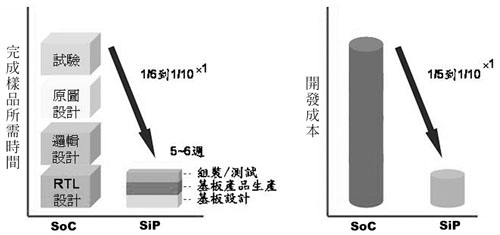

根據以上的業界經驗與最近10年趨勢的綜合作用,SiP在許多應用中成為較SoC更具吸引力的替代品,不過在一些案例中仍顯示SoC可滿足許多市場需求;而SiP成為更佳的解決方案在於SiP不但具有成本和上市時間優勢,且SiP能帶給新一代產品更具創新性,因此成為越來越多電子產品開始採用的因素(圖1)。

|

資料來源:Renesas

圖1 SiP與SoC相關技術示意圖 |

SiP的堆疊式晶片級封裝技術須將不同晶片或其他電子元件,整合於一個封裝模組內,用以執行某種相當於系統層級的功能,具有高效能與低成本的優勢,另外,這樣將減少並消除客戶對高速電路的設計需求,且系統級封裝產生的EMI噪音將更小,往往將開發和製造週期降低到1~2個月,使得SiP現階段擊敗SoC成為業者目前最常使用的技術主因。

SiP多元架構滿足各種需求

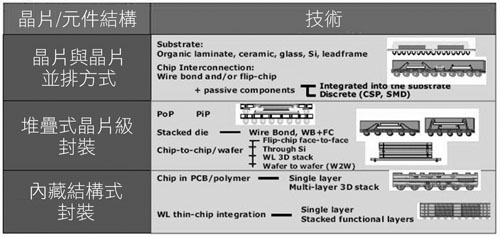

根據國際半導體技術藍圖(ITRS)的定義(圖2),SiP是指任何由一個以上具不同功能之主動電子原件,適當搭配被動元件或其他微機電、光、電等元件,組裝成的一個標準封裝,在一個系統或是次系統提供多工機能。目前SiP主要可以分為三種類型,第一種為晶片與晶片的並排方式(Side by Side);第二種為晶片與晶片的堆疊,亦稱為堆疊式晶片級封裝(SCSP);最後一種為兩個或數個已完成封裝的晶片,利用SMT製程,將已完成單一晶片封裝的產品堆疊,成為一複合式的封裝體,稱立體式封裝(3D Package)或內嵌結構式封裝(Embedded Structure)。

|

資料來源:ITRS

圖2 ITRS定義之SiP三種類型 |

堆疊式晶片級封裝有兩種封裝型態,分別是兩顆堆疊式封裝及三明治結構的堆疊式封裝;兩顆堆疊式封裝是上層晶片尺寸小於下層晶片尺寸之封裝方式,而三明治結構堆疊式封裝型態為封裝體為晶片尺寸相近,或是上層晶片尺寸大於下層晶片者。

不過堆疊式晶片級封裝也並非沒有問題,因為要能適應堆疊式晶片級封裝的厚度,晶片都須經過研磨過程,中間可能產生晶圓翹曲易碎與打線(Wire Bonding)問題,特別是當晶片變薄後將會削減晶片本身的強度,增加打線時的困難度。此外在銲線的製程中,當堆疊式晶片的上層晶片的尺寸大於下層晶片時,便會產生懸空(Overhang)的情形,此情況將造成上層晶片震動而將增加打線時的困難度。

立體式封裝則將主動或被動元件內埋於電路基板內層,以達節省電路板面積;目前發展出兩種方式,分別是PoP(Package on Package)及PiP (Package in Package)。PoP為典型的3D封裝,將經過完整測試的封裝的單晶片FBGA或堆疊晶片FPGA,堆疊在另外一片單晶片FBGA或堆疊晶片FBGA的上部。而PiP則是在BAP的基礎裝配封裝上部堆疊,經過完全測試的內部堆疊模組(ISM),以形成單晶片級封裝(CSP)解決方案的3D封裝。

以上三種的SiP技術相比都各有優劣,首先是堆疊式與立體式封裝受惠於晶片堆疊後較省面積,且封裝後晶片大小約在16平方毫米以下,但並排式封裝卻因為晶片並排排列,封裝後的晶片面積約16~34平方毫米;其次為堆疊式與立體式封裝面積較小,適合用於輕薄短小的電子產品,如數位攝影機、數位照相機、手機等行動裝置,反觀並排式封裝則適合應用於對體積要求較低產品,如印表機、數位電視等。最後為並排式封裝的製作成本較堆疊式與立體式封裝低,因為堆疊式與立體式封裝產品多為記憶體,雖然可以節省體積、功耗並加快時脈,但封裝的堆疊層數不斷向上遞增時,將導致製程難度增大與良率降低,成為變相的增加製造成本。

需求劇增以期SiP突破瓶頸

因為手機同時須要讀取程式碼、基頻應用緩衝及多媒體儲存三種功能,使得手機同時需要NOR Flash、NAND Flash及Pseudo SRAM三種晶片,由於記憶體晶片具有類似尺寸與打線、標準化電器的特性,所以手機上的IC晶片成為SiP最廣泛的應用。然而SiP仍須面對一些不易突破的困難點,包括已知良裸晶(KGD)與IC載板的成本、裸片黏接製程及封裝方式。

首先是良好裸晶,主要在於SiP多晶片封裝的特性,其產品良率是透過將所有元件的良率相乘來估算的,因此任一個裸片的失敗都將導致成本大幅度提高。早期的多晶片模組(MCM)成本特別高,因為產品必須在最後組裝完成後才能進行全面測試,因此就算發現錯誤但都為時過晚,當模組中只要出現任一元件故障,整個模組就須丟棄,且該晶片的損失是由封裝廠還是晶片商承擔都有爭議。

舉例而言,假定IC載板經測試且封裝技術都無問題,封裝良率以100%計算,而當一顆良率只有90%的IC若封裝同樣五顆IC成SiP,最後相乘後得出的SiP良率僅有59%,業者將無法進行量產。這將導致各晶片商須妥協於封裝廠,放棄自家晶片原有的熱性、機械特性,並告知封裝廠凸塊節距、材料及焊墊座標,只為提高封裝廠做SiP設計整合。

第二個困難點在於IC載板占封裝成本的高低,在過去導線架時代,導線架成本占總封裝成本約30~40%,但是BGA封裝的載板已提升到50%,且FC封裝甚至已達55~60%,因此無論是BGA堆疊還是FC堆疊的SiP,載板自有產能的取得成為關鍵,因為SiP是眾多載板的總合,所以占封裝成本會超過本單一晶片封裝的60%,對SiP廠商的成本競爭力形成影響。

第三個要考慮的問題點則是裸片黏接製程,目前採用90微米或更高階製程的GaAs晶片,由於處理的功率很大,晶片處理過程將遭遇過熱問題,使晶片對引線接合長度和周圍電路十分敏感。因為這種製程必須支援很薄的晶片,它必須具有超過90%的晶片黏接覆蓋率、不會污染晶片表面的全倒角(Full Fillet)、厚度在30和60微米間的黏結線,及能夠疏導裸片產生的1~4瓦功率的導熱性晶片黏接,導致製程控制極困難,因此在外形尺寸較小的產品,對SiP製造的製程要求更是十分苛刻。

最後一個困難點是封裝形式,由於SiP通常包含多顆晶片,而晶片與晶片間訊號的連接技術更顯重要,現階段主要是以傳統打線及覆晶封裝技術的晶片連接封裝型態為主,但矽穿孔電極晶片連接技術近兩年來開始受到業者重視。

過去的封裝型態,多半以打線作為內部接合的方式,將晶粒正面的電極與基板的內接點以金屬線連接,之後再將晶粒與基板以環氧封膠樹脂模封成型。打線接合的內部接合技術發展目前已技術相當成熟,成本亦相對較低。

覆晶技術則將IC具有線路的正面直接以凸塊和基板連接,且整個晶片表面均可製作接點,封裝效率接近1,因此具有更高的I/O密度,且電性佳、可靠性好,有更好的散熱能力,相對也允許較大製程誤差。

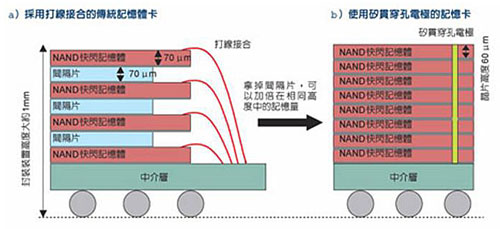

不過打線和覆晶等傳統互連方式,在互連晶片上面臨了各項的限制;由於打線通常都是幾毫米長,因此打線的路徑長度都太長,而在打線數和可重疊的晶片數方面也有架構上的限制。覆晶互連的路徑長度非常短,只能在一個凸塊上,但它只可以用來將兩個重疊的晶片相互連接,使得矽穿孔電極晶片連接技術的誕生,因為一旦採用打線,就必須在記憶體晶片之間插入一個隔離片,若使用了矽貫穿孔電極將可以拿掉隔離片,以達增加記憶體晶片的數量。

其實矽貫穿孔電極早在1980年代就被日本定位成國家級的研究計畫,但由於當時的成本高以致從未被商業採用。所謂矽貫穿孔電極是從上到下貫穿晶片,然後電路於晶圓上形成之後會被磨成100微米或更薄,接著把晶圓上的這些晶片打通許多貫穿孔,再電鍍內孔導通孔,形成幾微米到幾十微米的極小直徑之洞孔,而這些穿孔電極可以互連包封在單一封裝內的多個晶片,利用最短路徑長度在多個點將它們連接起來,建立經過所有晶片的訊號路徑,消除理論上晶片重疊的限制,目前東芝(Toshiba)已開發出利用矽貫穿孔電極來提升容量密度(圖3)。

|

資料來源:NIKKEI

圖3 東芝發展之矽貫穿孔電極封裝 |

手機應用為SiP主要商機

由於SiP不僅可增強單一封裝體的功能,並可大幅縮減系統產品的體積,進而提供符合客戶需求的解決方案。所以SiP已廣泛運用於RF、手機元件、影像感測器、記憶體等產品。目前手機仍將是推動SiP研發的主要動力,因為未來手機皆要求低成本、小體積、多功能及快速上市以符合產品生命週期短之特性,而這些主要訴求都是促使手機大量使用SiP之關鍵。現今手機市場當中,幾乎每支手機皆會有晶片堆疊封裝存在,特別又以Flash及SRAM的記憶體堆疊為主,主要是希望可以藉由晶片的堆疊,騰出多餘的空間,容納更多的手機晶片,滿足手機愈趨複雜的功能要求。

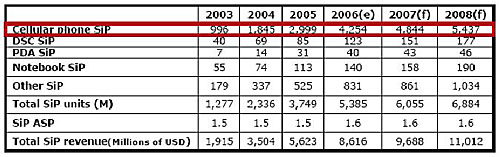

|

資料來源:ITRI

圖4 2003~2008年SiP市場需求 |

根據市調機構Prismark Partners分析,2005年SiP市場規模為43億美元,其中用於手機的射頻模組占42%為最大,第二大應用為堆疊式Die-in-Package封裝占28%。對於未來朝整合前進的趨勢下,PA Module整合Switch將成為最大的RF端應用產品;而包括Transceiver、VCO、LNA等元件的Module,為未來第二大的RF端應用產品,SiP市場整體規模可望於2010年突破100億美元。