為符合早期電視制式架構和其他媒體串列資料傳輸的要求,最早的影像感測技術使用被稱為捲簾式快門(Rolling Shutter)的電子快門機制。捲簾式快門及其相關的列並行(Column-parallel)讀出方式(即同時讀出同一行像素的讀出方式)有著悠久的歷史,這使其成為在互補式金屬氧化物半導體(CMOS)影像感測器內實施快門操作的自然選擇。

全域快門像素技術通常應用於電荷耦合器件(Charge-coupled Device, CCD)影像感測器,具有突出的技術優勢,藉著同時捕捉整個畫面的影像,以避免捲簾式快門帶來的偽像(Artifact)。然而,使用全域快門像素要求增加一個像素級記憶體,這是影響全面普及全域快門應用的一個障礙。

隨著CMOS影像感測器日益普及,機器視覺(Machine Vision)、電影製作、工業、汽車和掃描等應用越來越重視以高品質影像捕獲快速移動物體的能力。影像感測器供應商已開始解決在CMOS影像感測器上使用全域快門相關的技術難題,這種CMOS影像感測器能夠實現先進的機器視覺、掃描及電影成像。

今日,CMOS影像感測器供應商正在解決幾個技術難題,包括填充係數/量子效率(Quantum Efficiency, QE)、全域快門效率(Global Shutter Efficiency, GSE)和暗電流等問題,以便縮小捲簾式快門技術和全域快門技術之間的性能差距。在解決這些難題後,CMOS影像感測器供應商已可提供具有更小像素尺寸、更大填充係數、更高GSE、更低暗電流和雜訊的全域快門像素技術,使得CMOS影像感測器具備更好的性能以加速取代CCD影像感測器。

捲簾式快門技術不適合快速移動應用

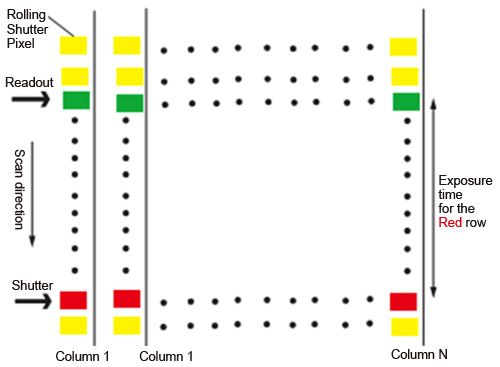

捲簾式快門也稱為焦平面快門(Focal-plane Shutter),利用行復位和行讀出(Reset and Readout)兩個掃描來控制曝光時間。實現行復位的快門脈衝在行讀出之前將某一行像素重定(圖1)。快門和讀出脈衝的時間間隔決定了曝光時間。

|

| 圖1 典型的捲簾式快門工作原理 |

然而,在使用捲簾式快門感測器時,因為不同行的曝光是在不同時點進行的,因而拍攝快速移動物體的靜態影像時會產生失真,這使得捲簾式快門不適合條碼讀出、機器視覺或自動檢驗系統等應用,因為這些應用要求對快速移動物體進行成像。

人們經常在使用某些膠卷相機及CMOS數位相機和攝影機時會發現,其中的捲簾式快門無法在單一時間點記錄整個畫面,而是透過垂直或水平掃描整個畫面來捕獲連續的像素條。

捲簾式快門的優點是影像感測器可以在拍攝期間連續收集光子,如此增強了光感度。然而,在運動或閃光等極端條件下成像時,捲簾式快門有明顯的缺點,那就是快速移動物體或閃光所帶來的失真,比如模糊(Smear)、扭曲、晃動和局部曝光。

在過去,人們一直在探索如何從捲簾式快門轉變到全域快門。但CMOS影像感測器供應商發現增加額外的儲存單元將會犧牲太多的光敏(電二極體)區域,對量子效率產生負面影響。而且,根據當時的半導體製程技術、應用層面的要求、市場需求、成本和其他因素的考量,無法斷定其產品可行性而未能有所進展。

全域快門技術影像品質較優

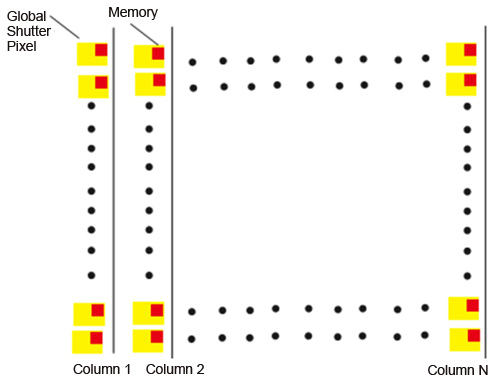

CCD影像感測器需要類比記憶體來進行工作,自然可以使用全域快門技術,因此採用全域快門技術的CCD相機和攝影機已相當普遍。全域快門藉著同時捕獲整個畫面的影像來消除捲簾式快門偽像(圖2)。

|

| 圖2 典型的全域快門工作原理 |

|

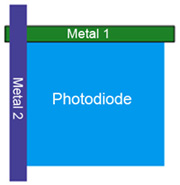

| 圖3 捲簾式快門像素 |

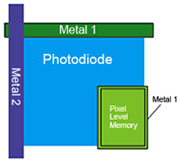

然而,對於CMOS影像感測器來說,全域快門實施方案的主要缺點是需要增加像素級記憶體,這對於某些應用是比較昂貴的方案選擇,如圖3~4所示。尤其對於成本敏感的行動應用,全域快門技術一直未受到青睞,因為行動應用並不像其他應用那樣重視影像品質或消除偽像,而是更重視成本。

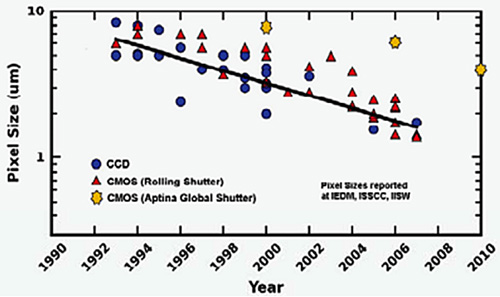

全域快門技術的其他缺點還包括低填充係數(Fill Factor),這導致量子效率的降低。為補償此一影響,全域快門像素的尺寸通常比捲簾式快門像素的尺寸大(圖5)。

|

| 圖4 全域快門像素 |

另一個重要問題是儲存節點的暗電流。暗電流指的是即便像素處於完全黑暗狀態時像素中產生的微小電流。典型的暗電流產生區域包括PN結的耗盡區和矽片表面。暗電流是像素雜訊的主要來源之一,並且在全域快門像素中比在捲簾式快門像素中更為嚴重。

最後,還要注意在背照式(Backside Illumination, BSI)像素技術中實施全域快門的問題。因為在光路中既沒有金屬層也沒有電晶體,BSI像素量子效率高於其前照式(Front Side Illumination, FSI)對應方案。然而,也正因為沒有金屬層,為BSI全域快門技術帶來顯著的缺點。由於缺乏金屬層來保護儲存節點避免曝光,全域快門效率(Global Shutter Efficiency, GSE)通常會降低。一個可能的解決方案是在背面沈積金屬,但採用此方法的問題是所產生的堆疊高度變高,以致雜散光仍然可以干擾儲存在這裡的訊號。儘管業界仍在探索,但這個問題一直未能解決。

|

| 圖5 捲簾式快門像素與全域快門像素的發展趨勢 |

在沒有電子全域快門的情況下,可以使用機械快門。然而,採用機械快門不僅增加系統成本,而且幾乎難以在行動產品內實施。另一個可選的方案就是使用偽像的數位校正;不過,這個方法會增加功耗和成本,並可能引入重建偽像(Reconstruction Artifact)。

CMOS影像感測器擁抱全域快門

在2000年至2001年,對於CMOS影像感測器供應商來說,全域快門技術提供的顯著優勢變得清晰,但須要仔細考慮實施方案。最流行的方法就是像素記憶體(Memory-in-pixel, MIP),除光電二極體和讀出電路外,其中的每個像素包含額外的儲存單元來臨時儲存光生(Photo-generated)電荷。

|

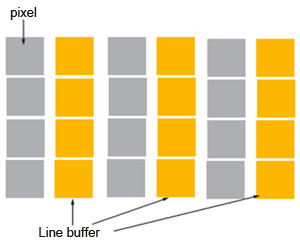

| 圖6 行間轉移型CCD |

在此方案中,感測器在每一行同時啟動曝光。在曝光結束時,光生電荷全部從光電二極體傳輸到像素級記憶體,然後透過讀出掃描逐行讀出。本質上,額外的像素級記憶體允許在每個像素上完成光生電荷累積和讀出操作,因此無需捲簾式快門脈衝。這個方法類似於行間轉移型CCD(IT-CCD)(圖6),行緩衝區緊鄰像素陣列的每一列,發揮與像素內記憶體相同的功能。因為每一行曝光開始於同一瞬間,不會出現捲簾式快門偽像。由此更進一步藉著對電荷累積和讀出進行流水線操作,可在完成當前的讀出操作後啟動下一次曝光,從而實現極高的畫面更新率(Frame Rate)。

留意填充係數和量子效率

在全域快門像素技術中增加儲存節點,導致填充因數永遠小於相應的捲簾式快門方案。為緩解量子效率的降低,儲存單元必須占最小面積。

另一方面,它的電荷儲存容量必須足夠大,以便保存從光電二級管傳輸過來的所有電荷。最理想的是,儲存節點的儲存容量必須設計為與光電二極體相同,從而使像素完全不受儲存節點的限制。此外,還應該把微透鏡最佳化,以便光電二極體可以捕獲全部的入射光。

全域快門效率攸關影像品質

|

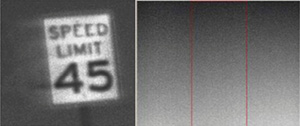

| 圖7 儲存節點上的漏光所引起的類似模糊和陰影偽像 |

全域快門效率(Global Shutter Efficiency, GSE)是全域快門像素技術的一個重要品質參數,用於衡量儲存節點中儲存的訊號電荷抗干擾能力。干擾可能來自多方面,例如因為存在光衍射和散射機制,實際上入射光永遠不會100%聚焦在光電二極體上,有些可能落到儲存節點上。圖7顯示在電荷儲存期間因強光照射而導致的漏光是如何影響儲存訊號的,看上去像是模糊和陰影之類的偽像。

|

| 圖8 全域快門像素橫截面突顯GSE問題 |

如圖8所示,儲存節點充當寄生光電二極體,在入射雜散光下可產生電子空穴對,因而干擾原先儲存的訊號。矽片深處產生的電子會擴散進入儲存節點中,並成為訊號污染的第二來源。

金屬遮光罩應盡可能接近儲存節點,以便保護節點免受大角度雜散光的影響。須要仔細設計矽片內的摻雜和位能曲線,以便矽片內產生的雜散電子被導引至光電二極體、而不是儲存節點。

留意暗電流問題

採用捲簾式快門像素技術,電荷會累積並儲存在低暗電流的表面固定(Surface-pinned)光電二極體中,直至讀出像素。相反的,全域快門像素技術通常須將累積電荷儲存在矽片中實現的儲存節點。

根據2003年Krymski和Tu的研究顯示,像素的浮動擴散區被用作儲存節點。類似於一個3-T像素結構,即使像素處於完全黑暗中,也存在與表面相關的大漏電流。而且,事實上浮動擴散區必須是高濃度摻雜結,這導致大PN結漏電流,而成為另一個暗電流來源。這些非常不受歡迎的暗電流,會影響儲存在儲存節點內的訊號。為緩減該現象,必須開發一種製程來鈍化或隔離儲存節點表面。

為替代使用浮動擴散作為儲存單元,開發廠商在像素中利用表面固定儲存節點來應對暗電流挑戰。如Aptina在其最新的全域快門感測器內,儲存節點使用自相關雙取樣技術,將讀出雜訊減少到四個電子,獲得出色低光照下性能。透過使用在貼近儲存節點的防反射金屬遮光罩,結合仔細的摻雜和位能曲線設計技術,可以獲得高GSE,而光電二極體和儲存節點的電荷儲存容量也得到有效平衡。

CIS影像感測器未來可期

傳統上,全域快門像素技術主要用於CCD影像感測器。由於CMOS影像感測器不斷普及,並且機器視覺、電影製作、工業、汽車和掃描應用要求必須以高影像品質捕捉快速移動的物體,影像感測器供應商已致力於克服在CMOS影像感測器上使用全域快門像素技術的相關傳統障礙。因此所提供的全域快門像素技術具備更多優勢,讓CMOS影像感測器在更多應用中成為CCD感測器的替代方案。

(本文作者任職於Aptina)