近來AI應用遍地開花,敲響先進製程投資競賽的戰鼓。然而,半導體製程微縮至7nm以下開始面臨到物理限制,而半導體業者也試圖跳脫摩爾定律,開創新的晶片設計與製造架構,以滿足新世代的運算需求。

近來全球掀起一陣人工智慧(AI)浪潮,2018年上半年舉辦的CES、Computex以及CES ASIA等國際性電子大展皆將AI列為重點主題,輝達(Nvidia)、高通(Qualcomm)、亞馬遜(Amazon)以及Arm等大廠也相繼發表AI相關產品。AI技術與應用不斷演進,運算機制漸趨龐雜,也掀起半導體產業在晶片設計與製造上的變革。

AI應用帶動高運算需求

近幾年AI應用遍地開花,也帶動高效能運算需求,單一型CPU已漸無法負荷AI所需的高運算量,如何整合硬體面的晶片設計與製造以提升運算效能,並同時應對軟體面的演算法革新,成為AI晶片設計的技術挑戰。現階段晶片設計多朝異構計算發展,以對應多重的演算機制。而隨著應用產品漸趨成熟,未來各應用領域也有機會發展專用化晶片。

談到AI晶片發展趨勢,工研院產經中心(IEK)分析師范哲豪表示,專用晶片的運算效能優於通用晶片,不過專用晶片的演算法固定,無法針對其他演算法進行加速,因此只適用於發展成熟、演算法已固定的產品。考量到這點,現今有許多廠商採用異構計算,讓ASIC處理演算法已固定的運算,而還須進行參數調整的運算,則採用CPU、GPU、FPGA進行處理,以提升整體運算效能。

進一步觀察各類晶片在市場上的發展,工研院產經中心分析師劉美君指出,目前晶片市場以Nvidia為首的GPU陣營、Google為首的TPU陣營以及Intel的Nervana NNP陣營在數據中心(Data Center)應用領域形成三國鼎立的局勢。而不同於上述廠商鎖定數據中心等級的應用,Arm則將家電、感測器等強調低功耗的應用領域納入布局藍圖,力圖將AI技術導入所有終端裝置中。

龐大運算需求敲響先進製程投資競賽戰鼓

為了將更多電晶體整合在晶片中以提升運算效率,各廠商皆冀望透過更先進的製程提升電晶體集積度,實現更高整合度、低功耗、低占位空間的晶片。如蘋果(Apple)、高通等公司皆對7nm世代的製程有極高的期待,而這股市場需求也敲響先進製程投資競賽的戰鼓。

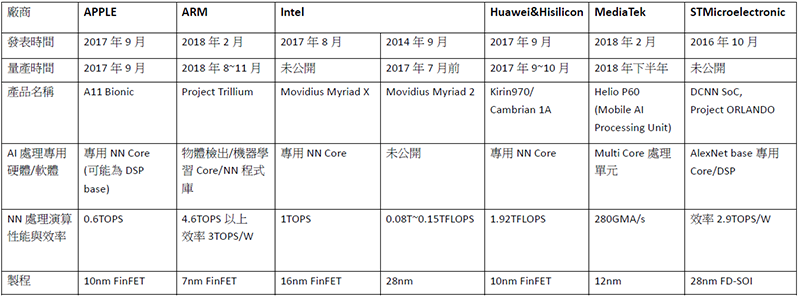

雖然目前AI晶片的生產以10nm以下的製程為主流,不過實際上廠商仍會依照其布局策略來選擇適當的製程。劉美君舉例說明,Arm鎖定終端/行動裝置領域,在提升晶片運算效能的同時,還必須兼顧功耗問題,因此會需要達7nm等級的先進製程;而意法半導體(ST)主要鎖定汽車市場,在體積、功耗上的要求沒有行動裝置那麼高,因此會選擇發展較為成熟、成本也相對較低的28nm製程(表1)。

表1 各廠商AI晶片發展概況

表1 各廠商AI晶片發展概況

EUV技術需求/挑戰

晶片中整合了數以億計的電晶體,電晶體由源極、汲極與位於兩者間的閘極所組成,電流會從源極流入汲極,並透過閘極的電壓控制電流的通斷。而半導體製程節點指的是晶片上形成的互補氧化物金屬半導體場效應電晶體(CMOS)閘極的寬度,亦稱線寬。線寬越短可在相同尺寸的晶圓上整合更多的電晶體,在晶片電晶體整合度相當的情況下,使用越先進的製程技術,晶片的面積與功耗就越小。而極紫外光(EUV)技術透過高能量、波長短的光源,將電路圖案轉印到晶圓,其光源波長比目前深紫外線微影的光源波長短約15倍,能達到微縮線寬的目的,因此備受各廠商矚目。

隨著7nm製程需求出現,現有浸潤式(Immersion)微影技術瓶頸造成良率低下的問題跟著浮現,若不尋求新的解決方案,晶圓代工(Foundry)業者將在微細化的議題上陷入苦戰。為了突破微縮製程在7nm的瓶頸,許多廠商紛紛投入EUV技術研發。

廠商紛紛投資EUV製程,盼能藉之提升生產良率,不過劉美君表示,實際上EUV微縮製程發展到7nm以下也面臨到許多技術難題。首先,由於EUV技術發展尚未成熟,因此可能會有產能(Throughput)下降的問題。以目前的情況而言,ArF浸潤式製程(一重曝光)產能可達275wafer/hr,而廠商公布的EUV測試產能只有85~125wafer/hr,不到前者的一半。儘管ASML預估EUV產能在2021年可進展至185wafer/hr,產能仍然不及浸潤式製程。

EUV技術還面臨曝光裝置耗電量過高的問題,以二氧化碳雷射放大器而言,EUV的光源效率約0.1%,若要輸出150W的EUV光源,就必須耗費150kW的電力。此外,光具有波粒二象性,當波長縮短時粒子性就會增加,而EUV光源波長短、粒子性強,會導致光源強度降低,並形成照射光源不均的問題。目前廠商正藉由金屬氧化物以及高功率光源的開發,尋求解決方案。

最後,劉美君還提到光罩防塵薄膜(Pellicle)的問題。光罩防塵薄膜可防止灰塵掉落至光罩上,但光罩防塵薄膜會使EUV光源變弱,導致整體產能下降。若為了維持光源強度而將功率提高至250w以上,則會有燃燒的風險,且光罩防塵薄膜在高功率的EUV光源下可能會產生微粒,造成光罩汙染。為解決此問題,廠商也積極開發高機械強度的光罩防塵薄膜,如AMSL選用信越化學的無機矽薄膜,而比利時微電子研究中心(IMEC)則朝CNT等奈米碳材進行研究。

摩爾定律恐失效 先進製程另覓出路

英特爾共同創辦人Gordon Moore在1975年提出摩爾定律(Moore's Law),預測單一矽晶片的電晶體數目,每隔18月將會增加一倍。而過去40年以來,半導體製程也確實按照著摩爾定律的腳步持續微縮。不過,除了前面提到的EUV技術挑戰,隨著電晶體線寬微縮至7nm以下時,還會面臨量子特性所導致的物理限制,其中最為棘手的即穿隧效應(Quantum Tunnelling Effect)。

劉美君說明,當單位面積上所整合的電晶體數量提高,電子移動的距離也會縮短,容易導致電晶體內部的電子自發通過電晶體的矽底板,導致漏電。隨著晶片中電晶體數量增加,二氧化矽絕緣層也會變得更薄,進而洩漏更多電子,增加晶片額外的功耗。而採用現有晶片材料,電晶體線寬一旦低於7nm,電晶體中的電子就很容易產生穿隧效應,導致半導體元件失靈,為晶片製造帶來極大的挑戰。

此外,先進製程所需的曝光機、刻蝕機等設備研發技術難度也提高。以10nm的光罩成本來看,根據英特爾(Intel)官方估算,該公司研發10nm製程的光罩成本至少耗費10億美元,若10nm製成晶片的產量低於1,000萬片,分攤到每片晶片的光罩成本就高達100美元。如此推估7nm以下的製程,若良率與產出無法提升,單顆晶片成本將十分高昂。

由上述可知,先進製程發展到7nm以下將面臨重多考驗,如何突破物理限制以跟上摩爾定律的腳步,或是要跳脫摩爾定律找尋其他可行的發展方向,也成為半導體業者在規畫未來發展方向時的重要考量。

異質整合克服摩爾定律失效

2017年台積電就曾預估摩爾定律發展至2025年會面臨挑戰,因應此趨勢,台積電創辦人張忠謀也提出「超越摩爾定律(More than Moore's)」的概念,跳脫摩爾定律對於集積度的執著,改從應用層面來看半導體的整合,透過橫向/異質整合來縮小半導體占積。

異質整合的概念是,利用先進的封裝技術將射頻、輸入輸出控制等不需要高階製程的產品與其他需求的半導體整合在同一封裝上。在單一封裝內整合更多功能,達到節省空間的目的。其優點是在進行IC設計時,不須把所有功能設計在同一個晶片上,可藉此提高設計開發的效率;另外,還可以突破矽的物理限制,將矽應用到各種不同領域。異質整合的應用包括台積電的整合型扇出(InFO)封裝技術,以及矽光子技術(Silicon Photonics)、微發光二極體(Micro LED)等。

半導體產業尋找新材料迴避矽物理極限

面對摩爾定律在物理上的限制,也有業者選擇跳脫原有以矽為基礎的CMOS元件製程,以新材料、新技術來開發更高性能、低功耗、相容於現有製程且具備成本優勢的製造型態。而目前較具發展性的材料技術包括量子電腦晶片、石墨烯(Graphene)FET以及矽光子元件等。

奈米碳管FET

據悉,奈米碳管(Carbon Nanotube)管壁僅有一個原子大小的厚度,因此有望取代矽來提升電晶體的性能。在技術發展方面,目前美國能源部旗下勞倫斯伯克利國家實驗室(Lawrence Berkeley National Laboratory)已使用奈米碳管與二硫化鉬(MoS2)開發出1nm以下的電晶體。

石墨烯FET

石墨烯是目前已知最薄、最堅硬的奈米材料,此外石墨化學結構穩定,導電性與耐久性也更優於矽材,因而成為用於電池的理想電極材料。日前,三星也已研發出基於石墨烯材料的電池技術,並宣稱其能提升45%的電池容量。

寬能隙材料

隨著AIoT的發展,未來將邁入兆級感測器(Trillion Sensors)的時代,如何減低電子元件功耗也將成為半導體技術發展的重要課題。而碳化矽(SiC)與氮化鎵(GaN)等寬能隙(Wide Band-gap)材料,具備耐高溫、耐高壓、電阻小、電流大與低功耗等特性,不但能滿足感測器對於功耗的要求,亦適合用以製造5G所需的高頻元件,是備受矚目的技術之一。

矽光子元件

相較於電子,光子沒有電荷與質量、不容易受外界干擾且傳輸速度較快,而以光訊號取代電訊號來提升整體傳輸速率也躍升為熱門的技術議題。現有的半導體工業皆以矽材料為基礎,因此許多廠商將矽材料整合發光元件進行光波導(Waveguide)的晶片訊號傳輸技術,視為面對摩爾定律瓶頸時所致力的新方向。

雖然目前已有廠商做出部分矽光子積體電路的元件,但劉美君表示,如何將被動元件與主動元件整合到同一晶片內,仍是一大難題。另外,矽本身無法發光,因此必須將發光材料透過晶圓接合(Wafer Bonding)機制整合進晶片中,才能實現矽光波導傳輸。針對此問題,有研究指出,Micro-LED技術有望透過晶圓結合機制與現有半導體製程整合,同時達到光源縮小化的目標,未來有望藉之解決矽光子元件發展所遇的技術瓶頸。

量子電腦技術

量子具有狀態疊加以及量子糾纏的特性,量子糾纏時量子就可能進入疊加狀態,因此一個量子位元(Qubit)可以同時處於0與1兩種狀態。而此特性也使量子計算不同於古典的運算法則,可以平行運算的方式進行模擬與檢索,同時處理龐大的資料量。因而吸引許多廠商投入量子電腦系統的發展。

不過,目前研究結果僅能顯現出量子效應的現象,還未能進行實際的運算。此外,量子易受外界環境影響導致量子態不易維持,必須在接近絕對零度的環境運作,且量子晶片技術原理與現行由電子傳輸機制所建構的半導體技術有很大的差異,高昂的製造成本將是其發展的阻礙之一。

AIoT的發展不但掀起晶片設計與製造的變革,更可能進一步改變過去晶片製造產業的供應鏈結構。劉美君表示,AIoT趨勢發展下,電子產業開始發生變化,傳統元件製造業者因產品單價快速降低,導致獲利銳減,因此必須結合軟體業者開創新的合作模式。未來,晶片製造可能會由AIoT服務業者提出應用端的需求,再由硬體與軟體業者一同進行開發,創造更高的獲利。