穿戴式裝置世代已經來臨。為因應日益變化的市場,半導體商早已馬不停蹄開發新的超低功耗晶片製程技術,來創造高度整合及低功耗SoC解決方案,以賦予穿戴式產品更好的性能。

穿戴式裝置世代已經來臨。為因應日益變化的市場,半導體商早已馬不停蹄開發新的超低功耗晶片製程技術,來創造高度整合及低功耗SoC解決方案,以賦予穿戴式產品更好的性能。

穿戴式電子產品市場在過去的一年中迅速崛起,經歷重大進展,重要性與日俱增。根據市場研究機構Futuresource Consulting近期的資料顯示,消費者對穿戴式裝置的需求正快速成長,2014年出貨量約達5,200萬台,較2013年成長32%,2015年則將達到7,400萬台,成長幅度達44%,未來數年,智慧手表和運動追蹤器等新興應用的成長將更加迅速。現在市面上的產品越來越多,用途也相當多樣化,從剛開始著重在健康和運動的裝置,逐漸擴展到智慧手機警示和多媒體中央控制等產品。

相對於手機,穿戴式裝置算是較新的市場,但卻十分多元繁雜,然而可以看到更清晰的前景逐漸成形,過去分散在各種不同裝置上的功能正整合到下一代的穿戴式裝置上,像是智慧眼鏡或腕戴式設計等產品。重要的是,領先業者現在可以透過技術構建模組來達成穿戴式裝置的下一階段發展,開發出運動健身、資訊娛樂、醫療保健、工業應用和企業應用等新型應用案例。

隨著近年穿戴式裝置市場逐漸演化,穿戴式裝置製造商或供應商越來越清楚知道穿戴式裝置該具備哪些功能,才有可能成為成功的商品進而被市場接受,半導體供應鏈業者也開始有所認知,各種不同種類穿戴式裝置分別有各自的封裝需求,例如,除了運作複雜作業系統(OS)和複雜使用者介面的高階裝置外,還會出現輕薄短小、無任何使用者介面、用作智慧型手機配件的裝置。

儘管有眾多不同的產品,所有類型產品間也具備共通關鍵實現技術,相較於智慧型手機,穿戴式裝置必須具備較高處理效能但功耗卻必需更低,這不表示智慧型手機對於功耗的要求不重視。然而,在多數的狀況下,穿戴式裝置對於功耗和效能間的最佳平衡通常會傾向對功耗更為要求;另一方面,特別是在較低階的穿戴式裝置市場上,成本亦是關鍵考量要素之一。

在電池續航力上,穿戴式裝置中使用的電池要比智慧型手機中的電池約小二十倍,但同時要能持續提供150毫安時(mAh)的電力並待機長達數周而非數天;較大的智慧型手機或其他行動裝置則需要3,000mAh的電池電力。

超低功耗製程為穿戴應用發展關鍵技術

事實上,目前多數市場上的穿戴式裝置均是使用ARM的低功耗晶片和技術,早在穿戴式裝置出現前就已經被廣泛使用。ARM及合作夥伴能定義和最佳化底層技術,進而為穿戴式裝置帶來更長的電池續航能力和更佳用戶體驗,其底層技術可透過為穿戴式裝置及應用所量身打造的定制系統單晶片(SoC)所呈現,經由下一代穿戴式裝置發展來具體實現這些先進技術。

要能夠達到兼具高度整合與低功耗的SoC解決方案,超低功耗晶片的製程技術至為關鍵。以晶圓代工領導廠商台積電為例,近期已將其低功耗(ULP)低漏電技術加以擴展,提供55、40和28奈米(nm)節點上的製程技術。這表示正常操作電壓將可顯著降低20%到30%,使穿戴式裝置的運作和待機功耗大幅降低,電池續航時間延長兩倍到十倍之久,儘管此製程支援最高至1.2GHz的速度,但SoC的時脈將僅會在500到600MHz範圍內運作,以獲得更低的功耗。此外,台積電ULP工藝也可在單個晶片上,部署嵌入式快閃記憶體和射頻(RF)功能與邏輯處理電路,能夠讓產品以更小巧的外形同時達到高度系統層級的整合。

對SoC業者來說,第二大關鍵要素則是如何選擇最佳的處理器功能、架構和軟體開發生態系統,這些通常是由ARM這類的IP廠商所提供。事實上,ARM處理器和架構已在穿戴式裝置領域有穩固的根基,目前多數的穿戴式裝置設計都是以既有處理器和微控制器所建立,而這些都是以該公司的技術為基礎。該公司生態系統包含豐富的處理器核心、IP和架構,可以讓SoC廠商獲得所有基本的需求,開發出色的低功耗穿戴式裝置。

現有的ARM處理器有多種選擇,包括Cortex-M系列處理器核心,該系列包含M0、M0+、M3、M4和M7,能滿足各個不同的效能需求。此系列核心均非常適用於穿戴式裝置,因為超低功耗核心能夠達到「隨時待機」和「隨時聯網」的感測機制,可在本地處理資料,盡可能縮小無線資料傳輸流量並延長電池續航時間,而目前在低成本智慧型手機中,被廣泛採用的Cortex-A5或Cortex-A7單核應用級處理器,也能夠應對Android Wear等複雜作業系統或複雜使用者介面的需求。此外,針對需要更多功能的穿戴式裝置,ARM亦有ARM Mali系列繪圖、影像和顯示處理器等IP,使可用的IP組合更為完整。

選擇合適設計架構

晶片業者可以針對不同的功能與價格區間來使用及組合IP,例如針對定價和低功耗來配置IP,這時效能就不是最主要的考量,晶片製造商可以採用Cortex-A5或Cortex-A7,當它們部署在智慧型手機上時通常會以1.2GHz時脈運行,不過,在40奈米ULP製程中,可以使Cortex-A5僅以500MHz時脈運行。由此所設計出的處理器不僅擁有很小外形、低廉成本和很低功耗,而且還保留根據系統要求執行類似智慧型手機複雜作業系統的能力。除了廣泛的IP選擇,ARM還有健全和廣泛的軟體開發生態系統,涵蓋包括行動和消費性應用等各個面向,該公司的商業模式讓晶片廠商能夠專注於差異化和特殊應用功能,同時還能利用取得業界最大軟體生態系統的支援。

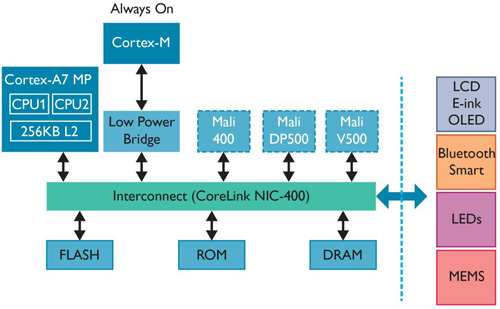

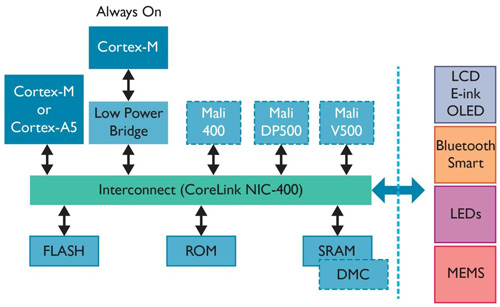

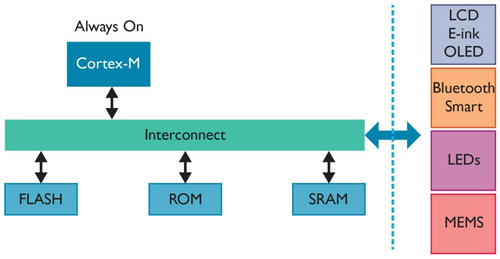

晶片製造商必需有全面性的設計思維,採用廣泛技術,才能開發針對穿戴式裝置優化的SoC,提供穿戴式裝置中必要的長效電池續航力、或在小巧外形下系統高度整合等全新功能。要成功設計出中階和高階裝置,關鍵是在多核設計中能夠具備高度整合並達成最佳系統架構分割,以便能高效處理來自感測器的即時資料,並且僅在必要時啟動應用處理器以運行複雜作業系統或使用者介面,同時還要輔以通訊功能的最佳組合(圖1和圖2)。至於低階產品,其不需要複雜使用者介面,而僅作為應用配件,因此可能不會部署應用處理器,此類系統配置(圖3)的關鍵在於,篩選從感測器輸入的資料,因為太多資料傳輸到智慧型手機將大幅提高功耗,儘管採用低功耗藍牙(BLE)傳輸協定對於延長電池續航力應該有所助益。

|

| 圖1 高階穿戴式裝置架構 |

|

| 圖2 中階穿戴式裝置架構 |

|

| 圖3 基礎穿戴式裝置架構 |

低階裝置中的處理器不會「隨時待機(Always on)」。通常它會在記憶體中累積感測器資料期間保持休眠狀態,然後再啟動。雖然對使用者來說感測器傳輸過程可能是連續性的,但處理器的使用只會由使用者互動等事件啟動,或者在已準備處理一組資料時產生。

穿戴式裝置市場已經日趨成熟,下一代穿戴式裝置將會要求創造新的定制、高度整合和低功耗SoC解決方案,實現此願景的模組已經問世,如最近推出的超低功耗晶片製程技術,連同ARM龐大的軟體開發生態系統和各種低功耗微控制器與應用處理器,可以為全系列的穿戴式裝置配置高效能SoC。

(本文作者為ARM競爭策略副總裁)