無線通訊產品設計整合度不斷提升,高頻元件與IC的微小化需求讓許多不同的創意構想不斷被提出,其中系統單晶片(System on Chip, Soc)的概念很早就被提出。但隨著IC技術從微米(μm)邁入到奈米(nm)等級,SoC所面臨的技術瓶頸也越來越難以解決。同時,微小製程成本快速提升,SoC晶片開發商所需的成本與時間壓力變大,使得有系統封裝(System in Package, SiP)技術概念的提出。

SiP是一種高整合的封裝技術,在單一包裝體中可以包含多個晶片、被動元件、天線和其他任一元件以上的封裝。也就是說,透過一個封裝大小的範圍就可以建構出複雜的功能,甚至是一個完整的系統。SoC與SiP都是為了縮小產品面積、降低整體成本而延伸出來的技術。而SiP在成本控制與產品搭配的彈性上比SoC更具優勢,在現階段的市場應用還有很大的空間可以發揮。

此外,數位(Digital)SiP與射頻(RF)SiP所考慮的技術問題也不太類似(圖1),Digital SiP通常是整合記憶體、處理器與輸入輸出(I/O)晶片等,並且是以晶片堆疊的方式來完成架構;而RF SiP是整合基頻(Baseband)晶片、收發器(Transceiver)、放大器(PA)與其他被動元件,通常是在基材當中堆疊被動元件。本文將針對RF SiP的模擬流程與技術做說明。RF SiP雖然是整個系統當中的一個子系統,但在無線通訊的應用上是相當重要且技術困難度較高的部分。

|

| 圖1 左邊是數位SiP堆疊方式,右邊為射頻SiP堆疊方式 |

RF SiP設計面臨三大挑戰

將RF晶片整合至一個封裝體中,有許多設計的挑戰,這些挑戰大致可以分成三個部分。第一是系統層級的模擬,工程師在此階段必須先確定系統的架構,不只要設計出最佳的系統效能,還必須考慮封裝布局與生產成本。第二是封裝架構與連接線的設計,三維(3D)封裝和基底堆疊都必須透過模擬來選出最佳化的結構與材料參數,Die to Die/Die to Package的連接方式都必須確實掌握。

|

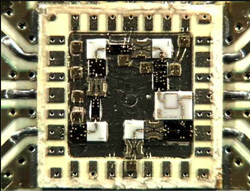

| 圖2 Quadrupled LO Down-Converter的照片 |

第三個部分則是被動元件的配置與設計,透過供應商提供的元件資料庫(Component Library)或軟體內建的行為模型(Behavior Model)可以模擬表面黏著技術(SMT)元件(Device)的現象,而在某些空間很小同時要求元件Q值很高的設計中通常會使用整合式被動元件(Integrated Passive Device, IPD)技術。

透過多種階層共同模擬驗證RF SiP

|

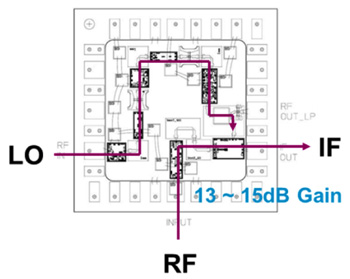

| 圖3 在封裝內部的訊號路徑圖 |

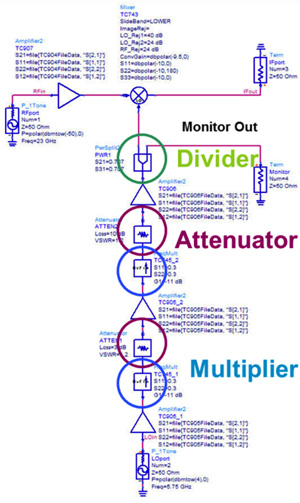

以一個Quadrupled LO Down-Converter SiP為例(圖2),這是一個將22G~4GHz RF輸入訊號降至1950MHz中頻(IF)的降頻器。而本地振盪器(LO)訊號是透過兩個倍加器放大四倍。RF和LO的訊號路徑如圖3所示。而在主動晶片部分,包含放大器、混波器和多功器。除了這些主動晶片外,還有八條薄膜被動電路特別設計在這個以氧化鋁的基底,用來連接這些主動晶片,並且提供如衰減和功率分流的作用。

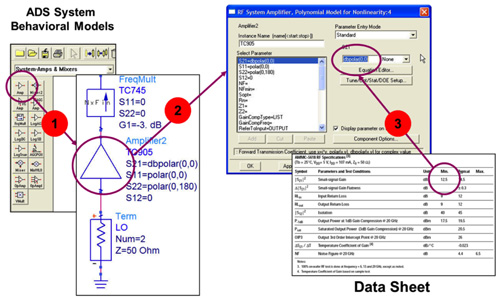

通常RF SiP會從系統架構的設計開始做分析,多種不同的架構和主動電路的搭配,就會花費工程師許多的心思來模擬及思考如何用最少的成本達到規格要求。由於每一段晶片的參數與需求都必須被計算,工程師需要有適當的模擬軟體來完成複雜的計算,例如安捷倫(Aglient)的ADS(Advanced Design System)就可以用於規劃及優化系統規格。

圖4~5說明了如何使用ADS內建的RF Behavior Model來完成Quadrupled LO Down-Converter的系統架構設計。而某些主動晶片商提供量測結果來當成晶片模型,將可以大幅提供系統設計的準確度,透過ADS的DAC(Data Access Component)就可以匯入如MDIF(Measurement Data Interchange Format)和S參數格式的量測結果。

|

| 圖4 如何使用ADS Behavior model |

|

| 圖5 ADS Schematic for Quadrupled LO Down-Converter |

若是晶片設計商,當系統規劃透過Behavior Model驗證完成後,系統內每一個晶片的區塊(Block)都可以使用真正的電路模型來取代,當使用越完整的電路模型,就可以得到更接近真實量測的結果。

然而,在一個功能複雜的SiP中不太容易拿到所有晶片的真實電路圖,因此結合Behavior Model與電路圖這兩種不同層級的協同模擬(Co-simulation)就是模擬軟體必須有的功能。ADS當中的Circuit Envelope和Ptolemy模擬器提供了系統模型+數位訊號處理(DSP)+晶片電路模型的共同模擬功能。而主動電路以外的被動元件與3D封裝模型,也是整體模擬非常重要的一環。

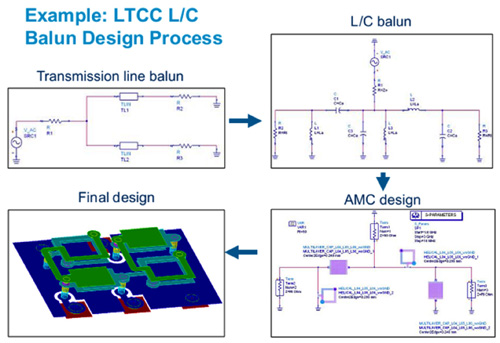

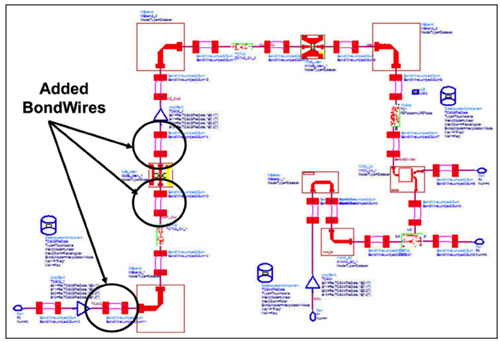

以一個L/C Balun為例(圖6),從一開始的傳輸線模型到最後使用真正布局(Layout)的電磁模擬,就可以快速地設計出符合要求的巴倫(Balun)。而3D封裝的方式通常依據不同需求有不同的封裝方法,而無論哪一種封裝方式,SiP的設計通常都會使用打線(Bond Wire)來完成晶片與封裝間的訊號傳輸,Bond Wire模型的萃取必須透過3D電磁模擬演算法依據匯入的結構分析得到一組S-par,最後再把被動線路與3D線路的電磁模擬結果一併帶入系統電路圖,取代原本完美的傳輸線模擬。

|

| 圖6 L/C Balun design process |

坊間有許多電磁模擬的工具,在本文傳輸線Layout和Balun等多層PCB板結構的模型萃取是使用ADS Momentum來完成,其演算法採用MOM(Method of Momentum),而3D Bond Wire是使用安捷倫EMPro的FEM演算法來完成萃取。

平面結構不使用FEM,是因為FEM本身演算法的特性和處理流程需要較多的記憶體與模擬時間,因此多層平面結構使用同樣是Full Wave演算法的MOM,可以花更少的時間但得到同樣準確的模擬結果。

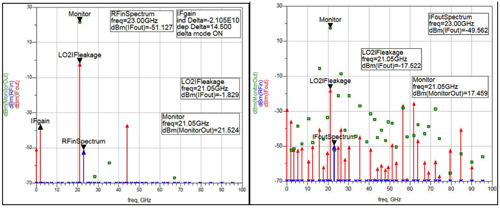

圖7就可以看到在這個Down Converter最後的電路圖,包含系統層級的Behavior Model、晶片電路圖、DAC匯入量測結果,以及傳輸線與Bond Wire的S-par模型。從圖8就可以看出,最後完整的模擬才可以更精準地觀察到其他寄生(Spurious)頻段的內容,而一開始Behavior Model的模擬結果太過理想,並無法準確預估諧波(Harmonic)的結果。

|

| 圖7 最後含有不同層級模型的電路圖 |

|

| 圖8 比較系統Behavior Model和最後電路的模擬結果(Harmonic Balance 2 Tone Simulation) |

Quadrupled LO Down-Converter SiP應用於雷達系統

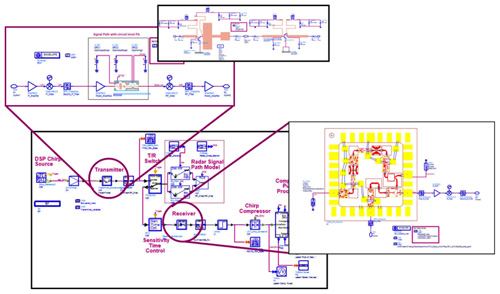

圖9是一個雷達系統設計的模擬圖,其中在接收器(Receiver)採用Quadrupled LO Down-Converter這個雷達系統,包含雷達訊號產生器、發射器(Transmitter)、T/R交換器、雷達訊號通道、接收器和壓縮突波訊號處理單元等。這個雷達設計就包含各種不同形式的模型,有電路模型、DSP模型和電磁模擬模型,透過ADS Ptolemy平台可以完成不同模型的共同模擬,並且驗證整體系統的結果是否符合雷達的標準規範。

|

| 圖9 SiP應用於雷達系統的模擬 |

|

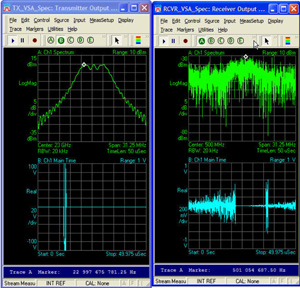

| 圖10 雷達系統Tx and Rx的模擬結果 |

從圖10可以觀察在發射器和接收器輸出端點都可以透過安捷倫VSA軟體得到時域和頻域的結果。Ptolemy分析完的結果可以透過Ptolemy當中的VSA模塊,及時地把計算結果傳到VSA,並且透過VSA轉換出時域與頻域的結果。

模擬軟體完成全系統分析

在本文中,RF SiP設計流程透過一個Quadrupled LO Down-Converter的例子做說明,透過業界成熟如ADS等的模擬軟體,就可以整合不同層級的模型與電路來完成整個系統的分析。透過如此共同模擬的技術,能夠幫助RF SiP的設計提高研發效率,並且能設計出更優化的產品。

(本文作者任職於安捷倫)