由於工程師正致力將多種射頻(RF)通訊標準整合至獨立裝置中,且軟體開發週期不斷緊縮,因此RF測試工程師首先必須採用完整定義,且可調整的軟體架構。工程師一定知道測試一組無線功率放大器(Power Amplifier, PA)的功率值需要約數秒的時間,但透過最新提出的創新RF量測架構,卻能將每一組測項縮短至5毫秒(ms)以內。其實量測速度的快慢除了儀器本身效能外,最大的瓶頸經實務驗證,關鍵卻是在儀器的溝通介面傳輸上。

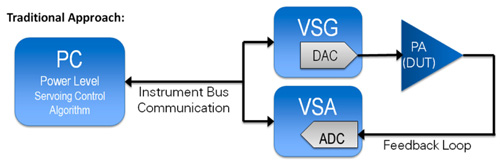

以功率放大器的校正為例,整體量測與校準效能的關鍵在於電腦與向量訊號產生器(VSG)、向量訊號分析儀(VSA)間匯流排的速度(圖1)。

|

| 圖1 整體量測與校準效能的關鍵,在於電腦與向量訊號產生器和向量訊號分析儀間匯流排的速度。 |

PXI平台加快測試進程

以傳統箱型儀器連接通用介面匯流排(GPIB)進行儀器控制與讀值,則整體的執行速度將卡在速度較慢的序列通訊上;若以PXI平台,模組儀器間以背板的高速匯流排交換資料,同時將資料傳回到電腦進行運算,可以大幅縮短十倍以上的量測時間。

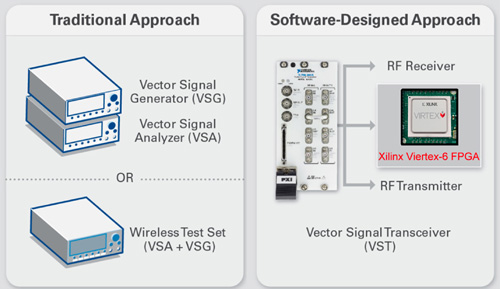

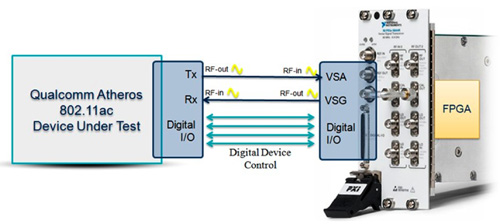

美商國家儀器(NI)推出新的PXI向量訊號收發器(Vector Signal Transceiver, VST)還能將原本PXI平台的測試速度再大幅推升二十倍,原因就在於使用嶄新的RF儀器架構,其整合使用者可自行撰寫的現場可編程閘陣列(Field Programmable Gate Array, FPGA)於RF儀器內(圖2)。

|

| 圖2 新的PXI平台向量訊號收發器使用嶄新的RF儀器架構,能將原本PXI平台的測試速度再推升二十倍。 |

|

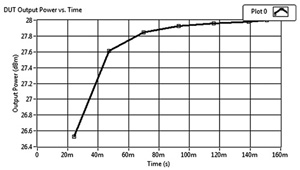

| 圖3 使用PXI平台可將時間縮短至約150毫秒。 |

量測速度的大幅提升來自於向量訊號產生器與分析儀不再須要透過匯流排傳遞資料,因為VST整合此兩者。再者,透過VST上的FPGA,原本在電腦上運算的程式,轉由如同硬體電路等級的FPGA來與VSG/VSA進行控制,跳過資料匯流排與中央處理器(CPU)的運算。

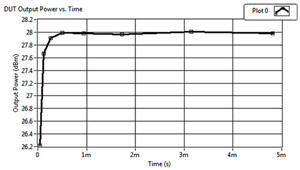

使用傳統箱型儀器進行功率放大器的功率伺服(Power Servoing),通常須要花費一至數秒來完成。若使用PXI平台可將時間縮短至約150毫秒(圖3)。若使用PXI平台VST上的FPGA來進行,則收斂時間大幅縮短至5毫秒(圖4),相較於傳統式儀器足足快上兩百倍之多。

|

| 圖4 善用VST平台上的FPGA,收斂時間可大幅縮短至5毫秒。 |

美商國家儀器在RF儀器上創新的架構,將RF訊號發射接收功能與FPGA做緊密結合,其優勢不僅僅是提升量測或待測物校正上的速度而已。未來通訊系統將走向寬頻,但高頻寬所帶來的高資料量在即時運算上,不論是調變解調、編碼解碼等應用,FPGA都將是寬頻通訊系統上量測的重要功臣。

VST能進行80MHz即時頻寬的通訊,更可運用多個VST輕鬆建構出多重輸入多重輸出(MIMO)系統,足以因應未來寬頻通訊量測需求。以下就以高通創銳訊(Qualcomm Atheros)使用PXI產品的應用案例進行說明,提供更多無線測試上的新啟發。

目前高通創銳訊正在改良Wi-Fi等高傳輸率的無線技術,以便滿足新的連線應用需求。最新的高通創銳訊晶片是一種具有三組無線電的MIMO收發器,適用於802.11ac這項最新的Wi-Fi標準。

呼應新型WLAN測試系統要求

由於將逐漸改用802.11ac這項最新的Wi-Fi標準,所以要持續加入新的調變機制,以及更多的通道、頻寬設定與額外的空間串流數目。此外,數以千計的獨立運作增益設定也會讓無線區域網路(WLAN)收發器的特性測試變得更加棘手。

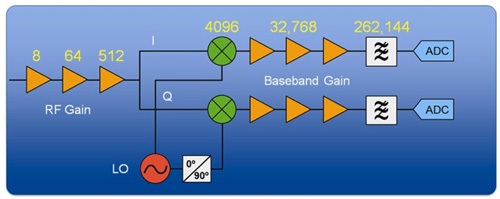

WLAN收發器的每個元件都具備多重增益階段。為了在低成本的互補式金屬氧化物半導體(CMOS)流程中開發出高效能無線電,高通創銳訊的設計團隊必須針對每個無線電架構階段採用靈活的操作方式。

一旦加入新的架構階段,多重增益設定便會大幅提高可能的設定組合數量,因此單一運作模式可能具有成千上萬個資料點,而且這只是一個無線電收發器的資料點而已(圖5)。如果系統搭載多個天線,MIMO設定的電路排列(Permutation)數量也會持續地增加。隨著可能的設定組合數量激增,要避免測試時間延長,便會是相當困難的挑戰。

|

| 圖5 以常見的WLAN接收器程式方塊圖為例,可以看出每個元件都具有多重增益階段,因此一個接收器可能會有成千上萬種不同的增益設定。 |

善用PXI儀器/LabVIEW FPGA

為解決這類測試時間的挑戰,高通創銳訊採用美商國家儀器PXIe-5644R向量訊號收發器。由於PXIe-5644R內建FPGA,所以可透過向量訊號收發器內的RF向量訊號產生器/分析器,同時控制晶片的數位介面。

一般而言,FPGA的程式設計必須藉由VHSIC硬體描述語言或Verilog。但其實許多工程師和科學家並不熟悉這些複雜的語言,不然就需要特定的工具,才能針對高階抽象層面增進設計產能,進而簡化FPGA程式碼的產生流程。

LabVIEW可清楚呈現平行機制與資料流,因此非常適合FPGA設計;無論使用者是否熟悉傳統的FPGA設計,都能有效運用可重設硬體的功能。

高通創銳訊採用LabVIEW來設計美商國家儀器向量訊號收發器的FPGA,以便控制待測裝置並處理資料。儀器內部即可執行處理程序,毋須透過匯流排來回傳輸至控制器,因此有助於大幅提升測試速度(圖6)。

|

| 圖6 高通創銳訊採用LabVIEW來設計美商國家儀器向量訊號收發器的FPGA,藉由數位方式來控制待測裝置。 |

傳統的機架堆疊式量測作業通常會受限於最佳的評估增益表選項,因此高通創銳訊的團隊必須透過反覆評估才能找出最終的解決方案,每次評估都得還原增益表特性。這是相當緩慢的流程,每次評估都會產生大約四十個重要資料點。

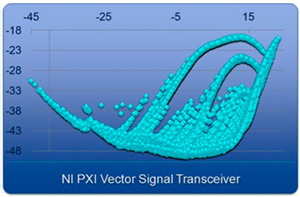

改用PXI向量訊號收發器後,因為測試速度變快,所以可執行完整的增益表掃頻,捨棄反覆評估的方法。這樣一來,即可在單一裝置的每次測試掃頻作業中全面測試無線電運作的特性,進而擷取全部共三十萬個資料點,以便確實判斷出最理想的運作設定。

|

| 圖7 PXI向量訊號收發器的測試速度更快,能執行完整的增益表掃頻,因此可擷取全部三十萬個資料點。 |

藉由這樣的資料操作流程,可以前所未有的方式掌握裝置的運作狀況,負責團隊即可探索以前從未想過的運作機制(圖7)。

透過儀器的RF前端元件直接同步處理數位控制時序,測試速度比以前的PXI解決方案多了二十倍以上,甚至超越原本的傳統儀器解決方案兩百倍之多。

對高通創銳訊來說,儀器彈性與精密控制非常重要,因為這可以有效地提升RF測試流程的效率,所以使用美商國家儀器全新的向量訊號收發器時,優異的測試效能讓人非常滿意。為客戶開發802.11ac解決方案時,PXIe-5644R也能夠提供更多自由與彈性,因此測試效能相當出色。

(本文作者任職於美商國家儀器)