正如同其他新科技,3D IC從醞釀到實際成形,也需要一段時間才能真正問世。但對有志投入3D IC領域的業者來說,面對挑戰並加以克服,更是必經之路。因此,相關業者必須解決規格、成本與設計工具等多項難題,才能真正在3D IC領域中找到春天。

一直以來,摩爾定律(Moore's Law)左右了半導體產業的研發與市場應用的進展,雖仍被大多數業者奉為圭臬,但因技術面臨瓶頸,導致演進速度漸有放慢的趨勢。以製程來看,目前處於32奈米(nm)製程時代,預估到2019年左右時,才可能進入16奈米製程。換句話說,必須經歷長達11年的時間,才能維持這樣的步調。也因此,愈來愈多的業者,努力提升技術,以便打破瓶頸與超越摩爾定律。

封裝技術演進複雜量產難題懸而未決

以封裝技術來說,其成長速度較前段製程產業快,在過去的5年內,其封裝型態數量成長快了將近五倍。但由於消費者需求的產品往往是朝體積小、功能複雜,且價格便宜等方向發展,新一代的半導體製程也因此有更多的設計成本,且面臨更複雜的設計模式、更獨特的設計,製程與封裝模式便成了關鍵。

目前市場的主流封裝方式,是在單一晶片上發展所有應用技術於系統單晶片(SoC),而封測公司也隨著發展出可支援多個功能晶片的解決方案,由於後段技術的發展趨勢在於「厚度空間的研發」,因此封測廠已提供3D封裝方案,例如使用打線接合(Wiring Bonding, WB)堆疊系統級封裝(SiP)晶片,以便追求更符合消費者想要的小而美產品。

然而,這樣的技術追求,並非全然無條件,至少在成本、效率、功能、散熱、耗電及產品上市時間,都須要同時考量。矽穿孔(Through Silicon Via, TSV)的立體互連技術便應運而生,除可提供比打線接合更短的互連路徑、更低的電阻與電感,以及更有效率地傳遞訊號與電力,還擁有不限制裸晶堆疊數量等優勢。而這樣的立體堆疊技術,須包含晶圓的薄化、鑽孔、以導電材質填孔、晶圓連接等。

至於在製程順序的規畫上,則選擇於互補式金屬氧化物半導體(CMOS)之前的先鑽孔(Via First)與CMOS之後的後鑽孔(Via Last)的方式,因此將影響設計、製造、設備與材質、封裝等價值鏈。

雖然市場對TSV技術已有應用時程的共識,然而,若要讓TSV應用在半導體元件製程中順利商品化而量產,究竟須要考量哪些因素,恐怕會是一大難題。

3D IC設計須全面 實作難題涉及廣泛

在2009年於加州聖荷西舉辦的國際電子電機工程學會(IEEE)/電腦協會(ACM)國際會議中,研發聯盟國際半導體製造聯盟(SEMATECH)發表了有關3D IC之設計與測試議題。根據了解,透過ACM/自動化設計技術聯盟(SIGDA)的贊助,SEMATECH網羅了3D IC的專家,如TechSearch針對市場、英特爾(Intel)瞄準設計與測試、晶片整合由IBM負責、Gradient針對散熱管理、電能供應為明尼蘇達大學、成本為潘州大學、記憶體架構與應用則分別由RPI與北卡大學負責。

至於3D-TSV堆疊的設備與測試方法,則由高通(Qualcomm)等提供探討。由以上探討則不難看出,TSV在應用上所須考慮的因素是全面性的,缺一不可。以下則根據筆者之觀察進行探討。

矽穿孔技術內容/規格不盡相同

應用TSV來堆疊3D IC是封裝技術的一個新突破,其未來可以用來整合IC、邏輯晶片、射頻(RF)、CMOS影像感應器與微機電系統(MEMS)等。然而,廠商要導入一個新技術,必須同時評估所有的面向,也就是說,首先至少須了解3D-TSV在製程目前可以達到的水準概況,才可作一全面的衡量。

如EMC3D便認為,要觀察與評估TSV的製程規格,應該從鑽孔的規格、可應用的材料、TSV製程的位置、堆疊與接合所使用的對準精密度等進行觀察。但是不同的應用所執行的TSV製程,其規格也不盡相同。

舉例來說,由於市場上對TSV三維堆疊技術應用時程之普遍看法,皆認為接續CMOS影像顯示器之後,下一波的TSV 應用將會鎖定在動態隨機存取記憶體(DRAM)的堆疊上,那是由於記憶體堆疊較屬同質性,在技術上較容易成形。

在此將使用DRAM堆疊的技術參數值,來說明目前TSV技術可達的技術水準指標,以及未來的預測值。其中包含了TSV孔的尺寸、薄化後的晶圓厚度、深寬比值等規格資料,並已可預測相關技術到2015年後的發展將更為突出。

另外,記憶體的封裝,主要仍使用打線接合,以及堆疊式封裝層疊(PoP)的封裝方式,此兩封裝方式大約占有80%以上的產值。而使用TSV來作堆疊的比例,亦將會從2007年的0.3%持續成長,並同時會在功能與封裝尺寸上有所進展。例如TSV的孔徑將會由目前的大於10微米(μm),預估在2015年之後縮小至5微米以下,至少縮減50%。而深寬比也將會放大到十倍以上,並將擁有不到50微米的間距。另外,在2015年之後,使用3D-TSV製程作堆疊的記憶體市場,預估至少有25%的規模。然而,儘管市場大部分業者樂觀預估TSV的應用成長,但亦有持保守態度者。根據三星(Samsung)的評估,由於記憶體堆疊的熱處理問題仍未見有效的解決方案,因此要樂觀看待3D-TSV應用在記憶體產品上,可能仍須進一步審慎評估。從表1的時程規畫可以看出,相關應用可能會往後延遲。

| 表1 DRAM應用TSV製程的預測表 |

| 時程 |

~2009 |

2010~2015 |

2015~ |

| 孔徑(μm) |

10~30 |

5~10 |

1~5 |

孔深(μm)

|

50~100 |

25~50 |

15~25 |

| 晶圓厚度(μm) |

50~100 |

25~50 |

15~25 |

| 深寬比 |

3:1~5:1 |

5:1~10:1 |

10:1~ |

| 間距(μm) |

75~100 |

50~75 |

20~50 |

| TSV密度(I/O數) |

~100 |

100~500 |

500~1,000 |

| 封裝型態 |

DDP |

QDP |

8DP |

TSV加工整體成本高

投入TSV製程來堆疊晶片,成本通常都會是廠商的首要考量,而部分的半導體聯盟,為了替會員評估相關成本,都努力嘗試找尋TSV的成本模式作為依據。

如EMC3D聯盟即是個例子,自成立以來,便致力於創造成本效益的角度,來評估執行TSV技術整體成本。而針對TSV成本方面控制部分,EMC3D公布了3年的目標如表2,也可稍微看出TSV成本在市場上的普遍需求。

| 表2 2008~2010年EMC3D之目標 |

| 時間(年) |

目標 |

| 2008 |

利用聯盟會員的設備與製程技術,將先鑽孔TSV製程導入到8吋晶圓的製作,並將成本控制在每晶圓400~500美元。 |

2009

|

可依技術趨勢,來調整使用先鑽孔或後鑽孔的製程,以便產出同第一年規格的晶圓,但成本須下降至每晶圓300美元。 |

2010 |

妥善整合TSV製程於12吋晶圓的架構中,並改善TSV製程的可靠度,不論是先鑽孔或後鑽孔的TSV,都將控制應用成本至每晶圓200美元以下。 |

以目前的狀態來看,EMC3D所設的成本目標,似乎進行得非常順利。然而,將TSV應用於三維堆疊,目前每片晶圓大概仍需要200~300美元的加工成本,以這樣高的成本,並不能滿足應用TSV的成本效益需求。部分廠商已經宣稱未來幾個月將會將TSV成本降低至每晶圓100~150美元的水準。然而,理想的TSV成本應該要再壓低,才能滿足引進新技術的合理價格。而根據半導體廠商和製造設備廠商的說法,隨著TSV爆發式的普及,成本將降至每片晶圓50美元,這意味著對於每片晶圓3,000~5,000美元左右的總成本而言,TSV加工成本可控制在1~2%左右。另外,若考慮封裝製程成本,只要單片晶圓的晶片裁切量超過五百枚,則每枚將不會追加超過10美分的成本。

另一方面,執行TSV須考慮的成本結構,應當包含多個不同製程,根據EMC3D針對內連線矽穿孔(Interconnect Through Silicon Via, iTSV)製程,應用於12吋晶圓時的成本結構,便可以看出TSV應用在3D整合時,可能會包含的成本因素。

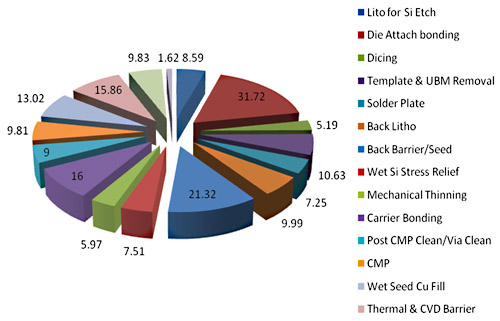

再者,由於執行TSV時,TSV孔的相關規格,也會影響成本結構,若以穿孔尺寸為5微米×30微米的TSV製程為例,並根據EMC3D在iTSV所公布的成本結構來作分析,從圖1可以看出,若以整個iTSV製程應用在晶圓整合時的整體成本來說,在圖中的統計總合為183.31美元,稍低於目前在市場中普遍的CoO。

|

| 圖1 執行iTSV於穿孔尺寸5微米×30微米製程之成本結構圖 |

另外,由圖1亦可看出EMC3D的iTSV製程,以Die Attach Bonding所花的成本31.72美元最高,其次是Back Barrier/Seed的21.32美元,再來便是Carrier Bonding與Thermal & CVD Barrier,各占16與15.86美元,此三項成本共占了約47%,已將近一半的成本比例,應是未來TSV成本控制的主要項目。

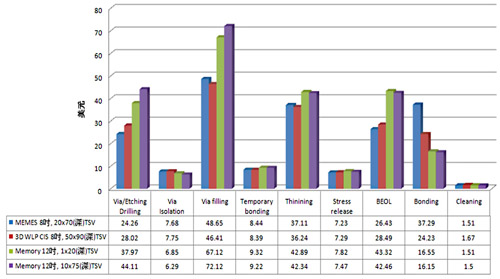

由於不同的TSV應用,將會產生不同的成本結構,因此根據Yole的統計,若是以不同穿孔尺寸的12吋記憶體晶圓、使用3D晶圓級封裝(WLP)的8吋影像感應器晶圓和8吋的MEMS來作比較,歸納共同的製程,其所模擬到的成本結構如圖2。雖然此為模擬結果,但若計算其所列的成本總合來看,以穿孔尺寸直徑10微米、孔深75微米(10微米×75微米)的12吋記憶體晶圓,所花的成本最大。其次是1微米×20微米的12吋記憶體晶圓。然而隨著穿孔的尺寸縮減,在成本的花費上,卻沒有太明顯的增加,反而有稍下降的現象。其中包含穿孔的蝕刻成本、填孔製程等,都有些微的減少,這代表隨著穿孔尺寸的精密度增加,TSV的應用成本將有下降的趨勢。

|

| 圖2 不同產品應用TSV的相關製程成本統計圖 |

另外,成本最低的是應用在8吋3D晶圓級封裝製程的影像感應器,其吻合目前3D-TSV,主要應用的產品為CMOS影像感應器的市場現況。若以個別製程來觀察,以填孔製程所費的成本占最多,大約為25%以上的成本,必須花在填孔製程上;而前三大成本,則主要包含有鑽孔、填孔及晶圓薄化,其成本的總合,約總成本的60%以上。也因此,在執行TSV時,應慎選如穿孔形成的方法DRIE或Laser、填孔的材料與方法,以及晶圓薄化的方法與載板等,以便可以降低TSV的整體成本;另外,若是以此四類的TSV應用總成本來看,目前可預見,單一晶圓須花費180~240美元的成本,來進行3D-TSV的加工製程,因此,離理想的TSV成本,仍有一大段的距離。

關鍵TSV製程考量因素所在多有

在業界的觀點,以3D堆疊技術來研發與量產,究竟關鍵因素為何?。稍早時SEMATECH聯盟針對不同角色如製程工具供應商、材料供應商、製造商與研究機構等,統計各角色認為投入3D IC時之重點(表3)。

| 表3 業界對3D IC投入重點之評估 |

| 項目 |

評分 |

| 設計工具 |

86 |

| 產品應用設計 |

84 |

熱能監控 |

83 |

| 雛型製造能力 |

73 |

| 測試方法 |

73 |

| 應用進路與標準化 |

72 |

| 基礎整合能力 |

69 |

| 可靠度 |

68 |

| 單元製程發展 |

63 |

| 測量 |

63 |

| 材料特性 |

46 |

| 相關工具開發 |

60 |

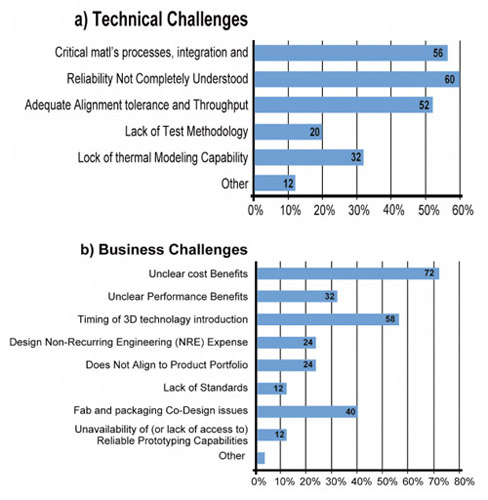

因此,普遍認為較重要的是設計工具、產品設計、熱能模式之建立、雛型能力及測試方法。另外,又根據技術與營運兩方面作調查(圖3)。從圖3可以看出,技術方面最重要的是沒有設計的基礎架構(Design Infrastructure),而在營運上則是較在乎採用後成本利潤不明確。由此可知,現階段3D IC產業在執行上的重點與將面臨的挑戰,首先必須克服的是軟硬體設備的建立與提供、製程設計與可靠度評估,以及成本模式之衡量等面向。

|

圖3 a 3D IC TSV技術挑戰因素

圖3b 3D IC TSV營運挑戰因素 |

TSV量產能力評估關鍵

作為新一代的封裝技術,根據各界的觀察,3D-TSV目前在封裝技術的應用,主流技術仍然是打線接合,當然,在需求與技術雙面的趨勢發展來看,打線接合的封裝仍會走到末路。大多數主要的半導體廠如台積電、日月光等,都已明白規畫3D-TSV到自己的演進上。但正如所有的主流技術一樣,在市場成熟到一定程度時,仍須作標準化的規範,才可搭上主流的列車。因此,以下將會從標準化的角度,來看3D-TSV技術該如何評估量產的能力、是否已經成熟。

現今市場上對3D-TSV的標準著墨甚少,許多國際組織如國際半導體設備材料產業協會(SEMI)等,都致力於推動3D IC的標準化。至少業界都有共識,當立體堆疊進入主流市場後,將會對半導體業產生重大影響,諸如設計規則與模組結構、供應鏈或價值鏈架構,以及如製程、設備與材料商等,都將重新定位。

不同的角色,在切入3D IC應用時,決策重點將會不一,從目前市場觀察,3D-TSV在進行整合製程,並作量產準備時,其主要的技術決策考量如表4。

| 表4 3D IC量產之決策考量 |

| 項目 |

考量內容 |

| 鑽孔方法 |

使用Laser或DRIE |

| 填孔材質 |

複晶矽、銅、鎢、Conductive Polymer等 |

| 填孔技術 |

電鍍(Electroplating)、蒸汽沉澱法(CVD)、聚合物塗裝法(Polymer Coating)等 |

| TSV製程使用時程 |

先鑽孔(Via-First)、早鑽孔(Via-Early)、後鑽孔(Via-Last) |

| TSV執行位置 |

正面(Front-side)與背面(Back-side) |

| 低溫接合方式 |

Direct Cu-Cu、Adhesive、Direct Fusion、Intermetallic及混合式接合 |

| 堆疊方法 |

W2W、C2W與Chip-to-substrate(C2S) |

| 薄化後晶圓裝卸 |

是否使用載具(Carrier) |

換句話說,當要應用3D-TSV於立體晶片堆疊時,上面所列的各種決策,都須要妥善配置,才有能力進行量產,而標準化的建立,則是主要的關鍵因素。 反觀目前在3D-TSV應用市場上,已公布的標準,僅有記憶體互連標準(IMIS)。

根據Tezzaron的說法,未來在發展高速處理器核心時,必須應用三維互連技術,來提供更大的訊號頻寬。因此,其所屬的3D IC聯盟(3D IC Alliance)便發起的記憶體互連標準(IMIS),公布了三維記憶體晶片堆疊的官方標準規格。若以一千支接腳的記憶體為例,此標準將處理器與記憶體作平行互連,電能便可控制在3瓦以內,遠低於傳統互連技術至少需30瓦的電容量;另一方面,IMIS標準也提供解決處理器製造商想要處理數十億記憶體訊號頻寬問題的解決方案,將DRAM的訊號密度提升並直逼靜態隨機存取記憶體(SRAM),但卻能讓DRAM的成本更低。

IMIS的埠數,若在測量面積為450×2,000平方微米下,柵格(Pin Grid)可達高十九格,寬八十格的水準,而每格平均尺寸為25平方微米,若是處理器製造商將其原有的晶片加入IMIS標準,便可以輕易地與3D IC聯盟成員所提供的記憶體晶片相容。因此,聯盟的創始成員中,Tezzaron和Ziptronix已經使用IMIS標準來製造記憶體晶片,並於2008年末發布第一個產品線。

另外,在製程標準化上,由於3D-TSV牽涉到如執行的位置、鑽孔的方式、互連的方法等問題,仍未有明確的標準公布。而EMC3D針對TSV的Via-First製程則公布iTSV,並且於Via-Last的製程部分,亦規畫有pTSV,此兩類為目前市場所見有關TSV製程的標準。可見應用TSV的領域,仍舊屬於開發啟蒙的階段,如前述在標準化須要考量的因素來看,TSV仍須仰賴價值鏈中各廠商,共同發展研發,並尋求標準作法,才能成為主流應用。

3D IC從谷底出發搶先卡位有助未來發展

TSV的應用市場,以目前的階段來看,仍然屬於未成熟的市場。反觀自從IBM發表覆晶技術之後,也須經歷數10年的時間,才有今日覆晶技術成熟市場的局面。因此,相較於覆晶技術而言,TSV也將經歷一段相類似的技術開發生命週期。

其實,一個製程技術可以進展到足以量產的地步,必須具備製程中的可靠度評估、成本衡量,以及標準的製造程序等標準的建立,以下綜合各方看法,提供應用TSV技術量產時,應具備條件的檢核項目:製程成本是否可以合理降低,是否可以明確界定市場未來的應用,三維設計自動化設備(EDA)是否可以支援製程設計,是否可以提供熱處理和材料的問題,是否具有足以量產的工具設備,以便滿足具有經濟效益的產量需求,以及是否可以提供測試工具等。

到目前為止,除了第一項成本控制,似乎已有較明顯的進展,例如EMC-3D可以讓使用iTSV製程的晶圓成本,控制在每晶圓145美元的水準內,而其他的項目,如市場應用的定位、支援的工具設備、可靠度的評估模式等,都仍處於初期的階段,不論是在8吋或12吋晶圓之應用上,除了晶圓薄化、組裝和最終測試方法外,大多數的製程都屬於成長期,仍須進一步的驗證與標準化。特別是12吋晶圓之應用,由於未臻於成熟,因此如蝕刻工具與方法、薄化後晶圓的卸載等技術都屬於雛型開發的階段,而進行過TSV加工後的晶圓探針(Wafer Probing)則仍無有效的解決方式來支援。

量產3D IC可以讓消費者取得更加滿足效用的電子產品,並且可以讓半導體業開闢另一塊藍海。然而,許多研發聯盟與其會員,仍然駐足觀望。若以短視的角度來看,立體堆疊或3D TSV的應用,既不符合成本效益,更會產生更多的不確定性;但若以遠視的角度來思考,若不搭上這班從谷底出發的列車,中途想上車時,就會發現3D IC列車上已擠滿了人群。

(本文作者張嘉華為南台科技大學科技管理研究所 助理教授、唐經洲為工研院資通所專案副組長)

| 參考資料 |

.EMC-3D Consortium Targets Cost-Effective TSV Interconnects, SemiConductor, Feb/2007,

http://www.semiconductor.net/article/CA6409528.html?q=EMC3D

.Highlights of 3D ASIP, SemiConductor, Nov/2008, http://www.semiconductor.net/blog/200000420/post/270037227.html

.3-D chip stacks standardized, EE Times, July/2008, http://www.eetimes.com/showArticle.jhtml?articleID=208808499

.Samsung devises 3-D DRAM with TSVs, EETimes, Feb/2009, http://www.eetimes.com/showArticle.jhtml?articleID=213403028

.R&D Consortium readies for Low Cost WLP of Silicon Interposers, I-Micronews, Nov/2008,

http://www.i-micronews.com/news/RD-Consortium-readies-Low-Cost-WLP-Silicon-Interposers,2510.html

.How much cost can be reduced for TSV technology, Nikkei business, Apr/2009,

http ://china.nikkeibp.com.cn/news/semi/45584-20090409.html

.3D IC Questions and Answers with the EMC-3D Consortium, SemiConductor, Oct/2008,

http://www.semiconductor.net/blog/Perspectives_From_the_Leading_Edge/12504-3D_IC_Questions_and_Answers_with_the_EMC_3D_Consortium.php

.3DIC & TSV Interconnects, Yole Developpement, Nov/2008

.IITC reports on interconnect progress, EETimes, Sep/2008, http://www.eetimes.com/showArticle.jhtml;jsessionid=

MMF3EGKJRN0HWQSNDLPSKH0CJUNN2JVN?articleID=207601527

.Wanted: Thermal Management Materials for 3-D ICs, i-Micronews, Oct/2008, http://www.imicronews.com/analysis/

Wanted-Thermal-Management-Materials-3-D-ICs,2359.html

.Semi Standards- a 3D Conundrum, May 2009,

http://francoisevontrapp.blogspot.com/2009/05/semi-standards-3d-conundrum.html

.3-D chip stacks standardized, EETimes, Jul/2008, http://www.eetimes.com/showArticle.jhtml?articleID=208808499

.3D-IC Alliance, Introducing the Intimate Memory Interface Standard, July/2008,

http://www.chipcrunch.com/Blogs/Technical.Bits/3D-IC.Alliance.introducing.the.intimate.memory.interface.standard.html

.Tackling the TSV Checklist, Feb/2009, http://ap.pennnet.com/Articles/Article_Display.cfm?ARTICLE_ID=353615

.Susan Vitkavage, Making the Business Case for 3D, Future Fab International, Iss. 22, 2007 |